Manufacturing method of self-alignment low-voltage super-junction MOFET

A manufacturing method and self-alignment technology, applied in the fields of semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as abnormal device parameters and device failure, and achieve the goal of increasing the number of devices, reducing device production costs, and optimizing parameters. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0064] An embodiment of the present invention provides a method for manufacturing a low-voltage super-junction MOSFET. The method is as follows: filling polysilicon through deep grooves, two deep grooves are mutually charge-balanced to complete the super-junction function, and then wet etching is used to form a shallow MOSFET above the deep grooves. Grooves, low-voltage super-junction MOSFETs are fabricated in shallow trenches to form low-voltage super-junction devices.

[0065] An embodiment of the present invention provides a method for manufacturing a low-voltage super-junction MOSFET, which is implemented through the following steps:

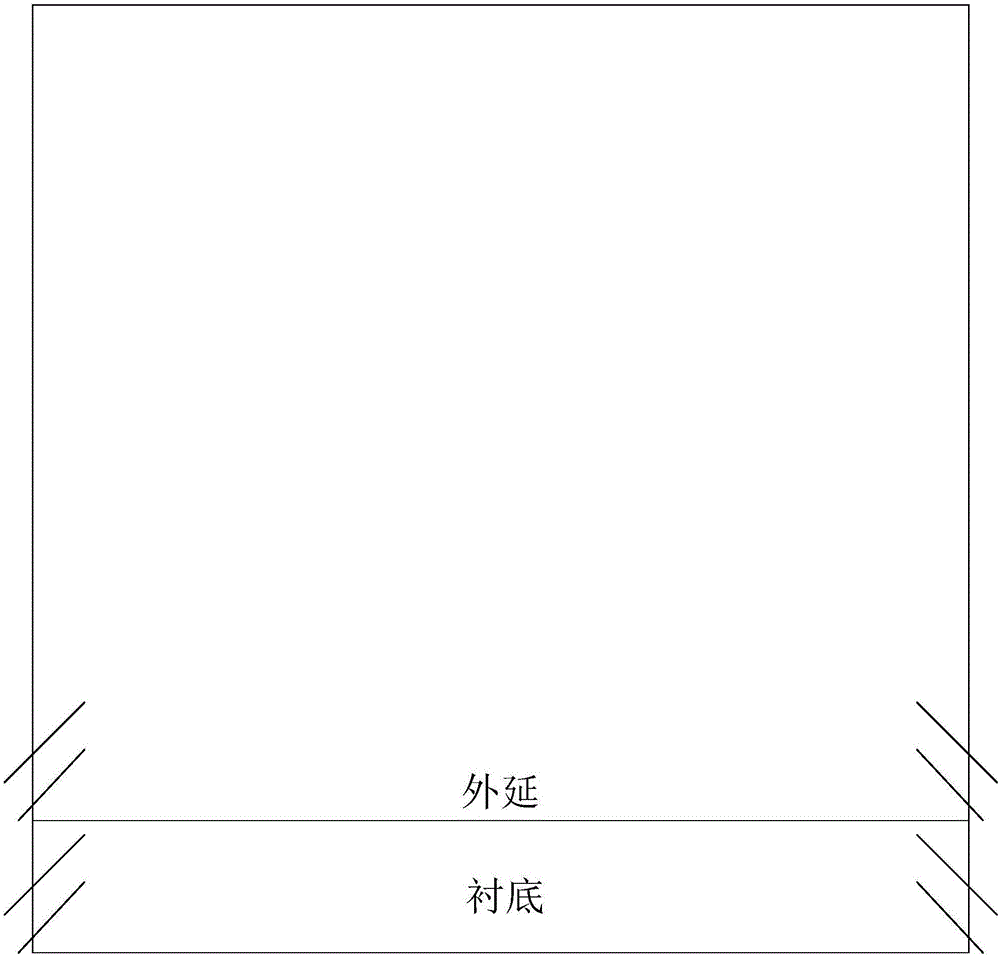

[0066] Step 1: Provide an n-type heavily doped n+ substrate, and form an n-type epitaxial layer on the n+ substrate, such as figure 1 Show;

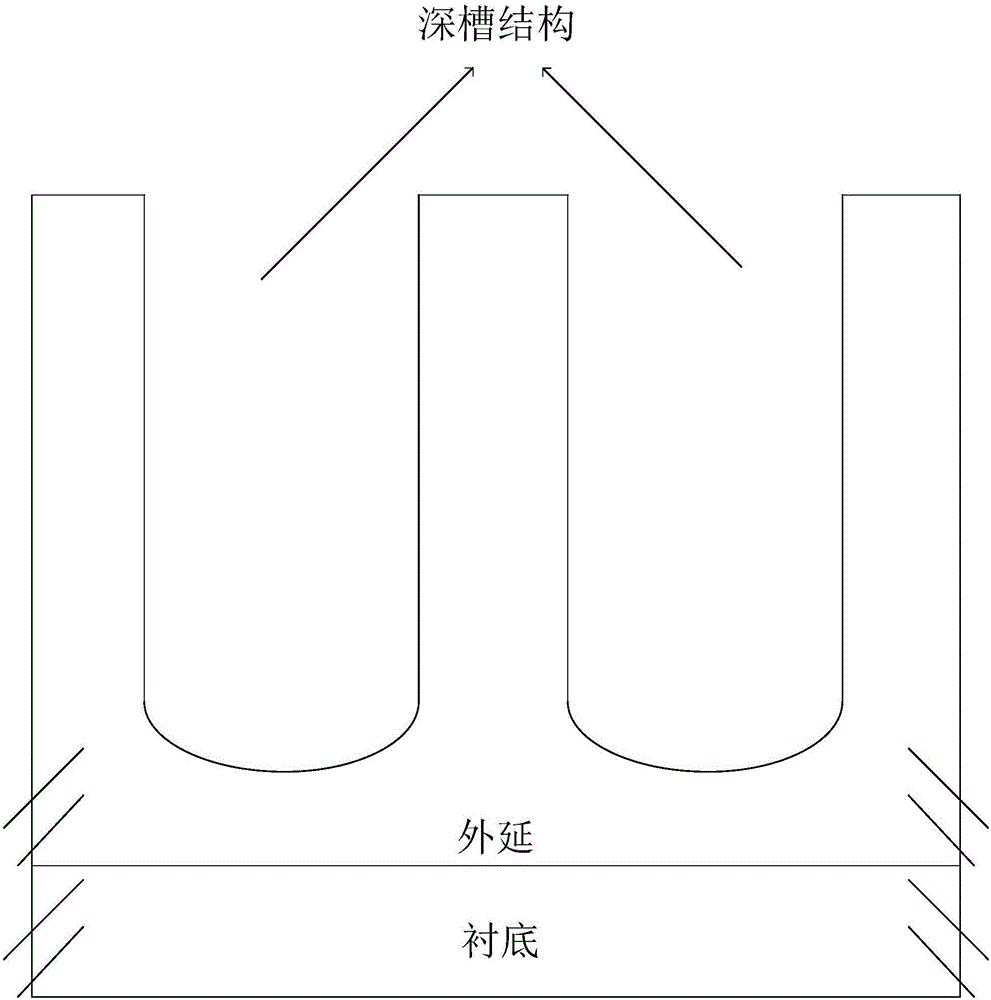

[0067] Step 2: On the n-type epitaxy, form multiple array-type strip-shaped deep grooves by photolithography and dry etching, such as figure 2 Show;

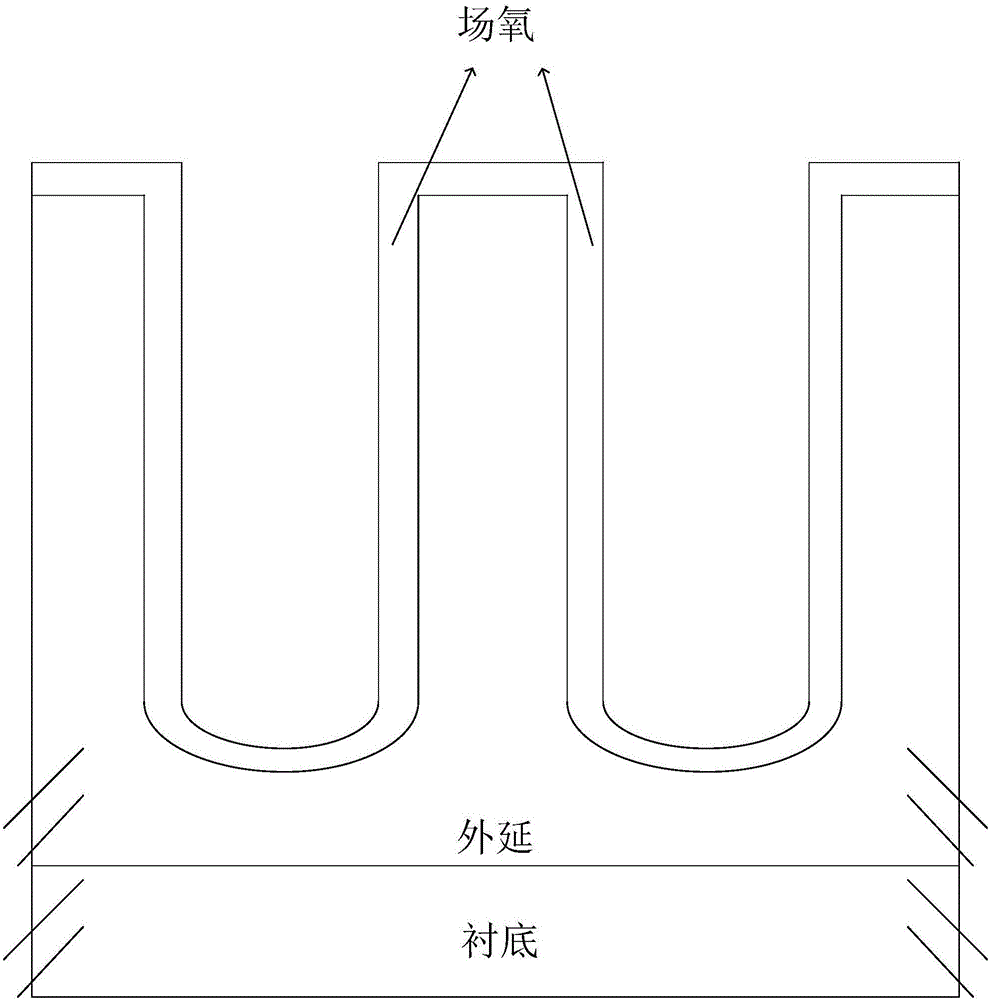

[0068] Step 3: using a thermal oxidation process...

Embodiment 2

[0087] The embodiment of the present invention also provides a method for manufacturing a self-aligned low-voltage super-junction MOSFET, which is characterized in that the method is implemented through the following steps:

[0088] Step 1: providing an n-type heavily doped n+ substrate, and forming an n-type epitaxial layer on the n+ substrate;

[0089] Step 2: Forming deep trenches in the active region and deep trenches in the terminal region by photolithography and dry etching on the n-type epitaxy, and the deep trenches in the terminal region surround the deep trenches in the active region;

[0090] Step 3: using a wet thermal oxidation process to grow a field oxide layer on the bottom and sidewalls of the deep trench;

[0091] Step 4: using the polysilicon deposition process to perform the first polysilicon deposition;

[0092] Step 5: Etching back the polysilicon through a dry etching process until the polysilicon is flush with the upper surface of the epitaxial layer; ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More