Parallel implementation method of real-time phase noise hardware generators

A technology of phase noise and implementation method, applied in digital function generators, instruments, digital data processing components, etc., can solve problems such as low speed and poor real-time performance, and achieve the effect of large bandwidth, good quality, and low FPGA resource consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The present invention will be described in detail below with reference to the accompanying drawings and examples.

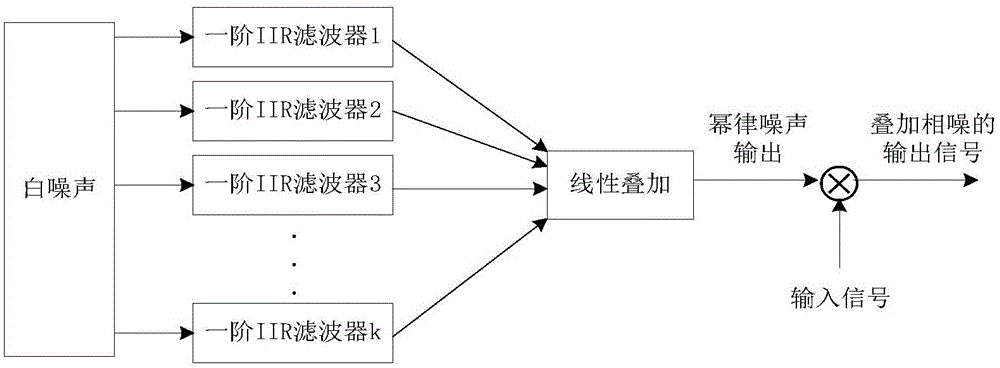

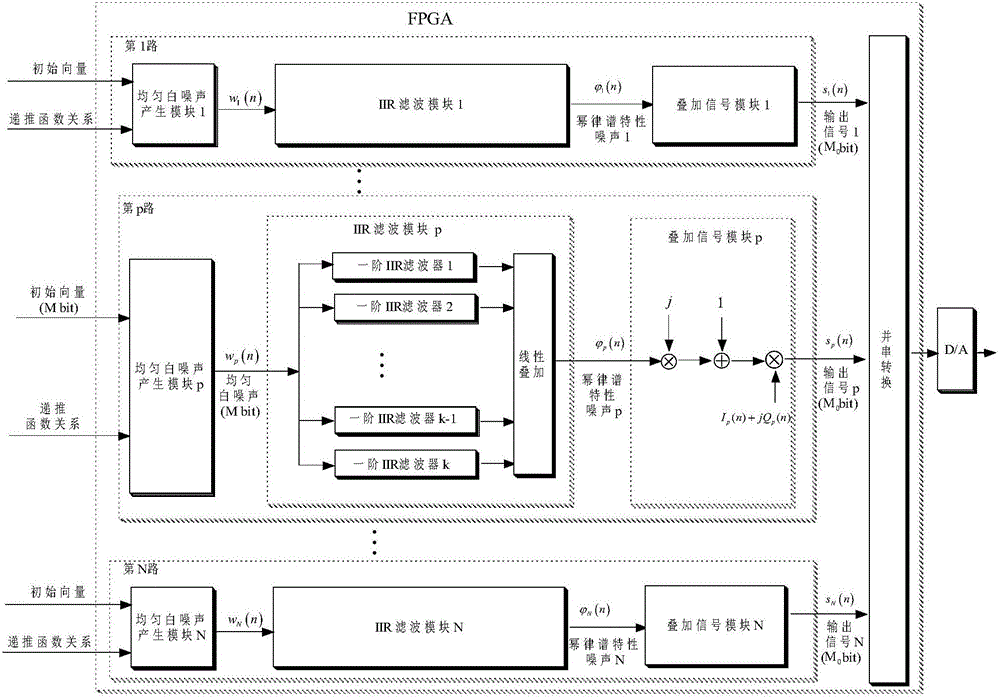

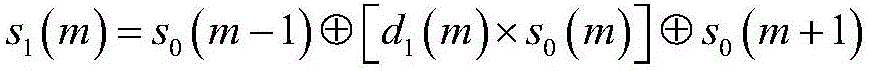

[0035]The invention provides a parallel implementation method of a real-time phase noise hardware generator. According to the cellular automata theory and the IIR filtering process, power-law spectral noise is generated in parallel, real-time and high-speed on the FPGA, and on this basis and effectively Signal superposition to complete parameter controllable phase noise simulation. Firstly, according to the noise cycle length, the high-speed sampling frequency of the actual system and the FPGA low-speed working clock, etc., the order, rules and parallel paths of the cellular automata are determined; subsequently, according to the order and rules of the cellular automata, the Reed algorithm or look-up table to obtain regular vectors; at the same time, according to the theory of cellular automata, the N-way initial vectors and function recursion relations re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More