Automatic test platform of high-speed ADC chip and test method

An automatic test and chip technology, applied in the direction of automatic test system, electronic circuit testing, etc., can solve the problem of short test process time-consuming, and achieve the effect of improving test efficiency, high test efficiency and high test rate.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0042] The technical solutions described in the present invention will be clearly and completely described below in conjunction with an embodiment of the present invention and the accompanying drawings. Apparently, the described embodiment is only a part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

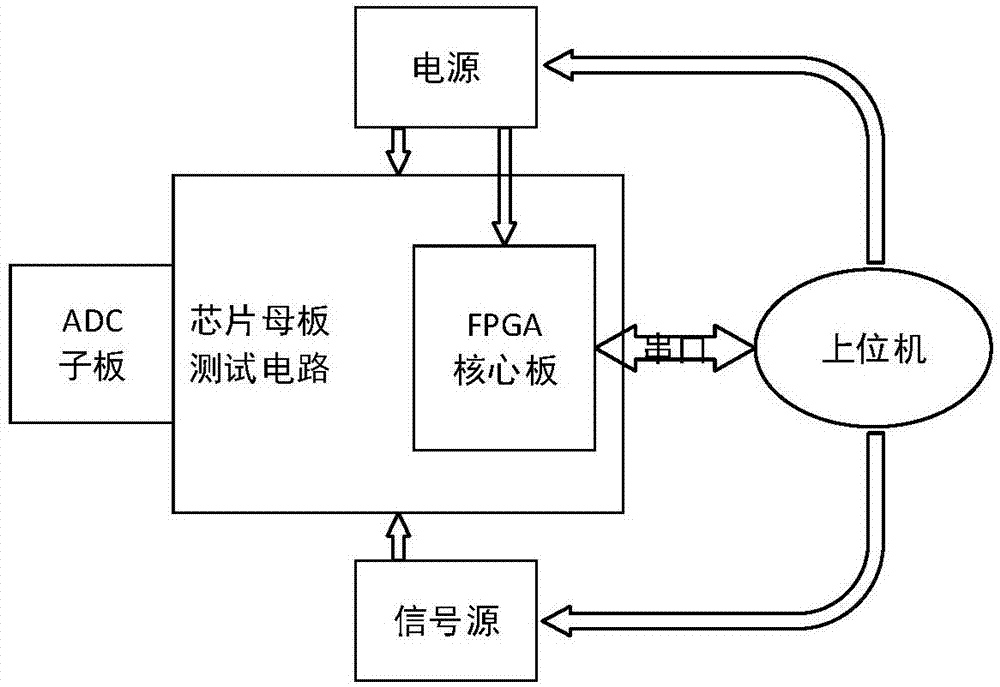

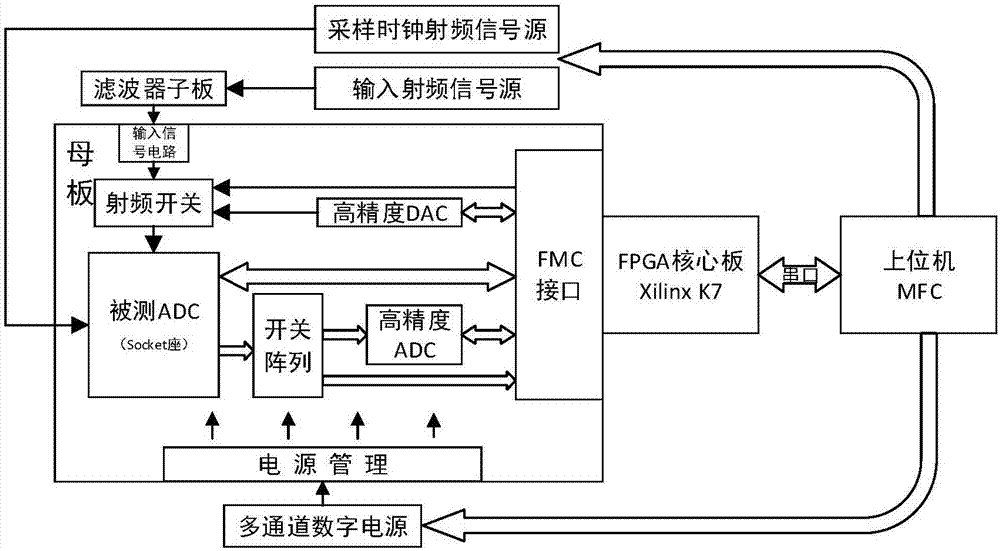

[0043] see figure 1 As shown, the automatic test platform of a kind of high-speed ADC chip of the present invention is made up of five parts: ADC sub-board, test motherboard, FPGA core board, host computer and test equipment.

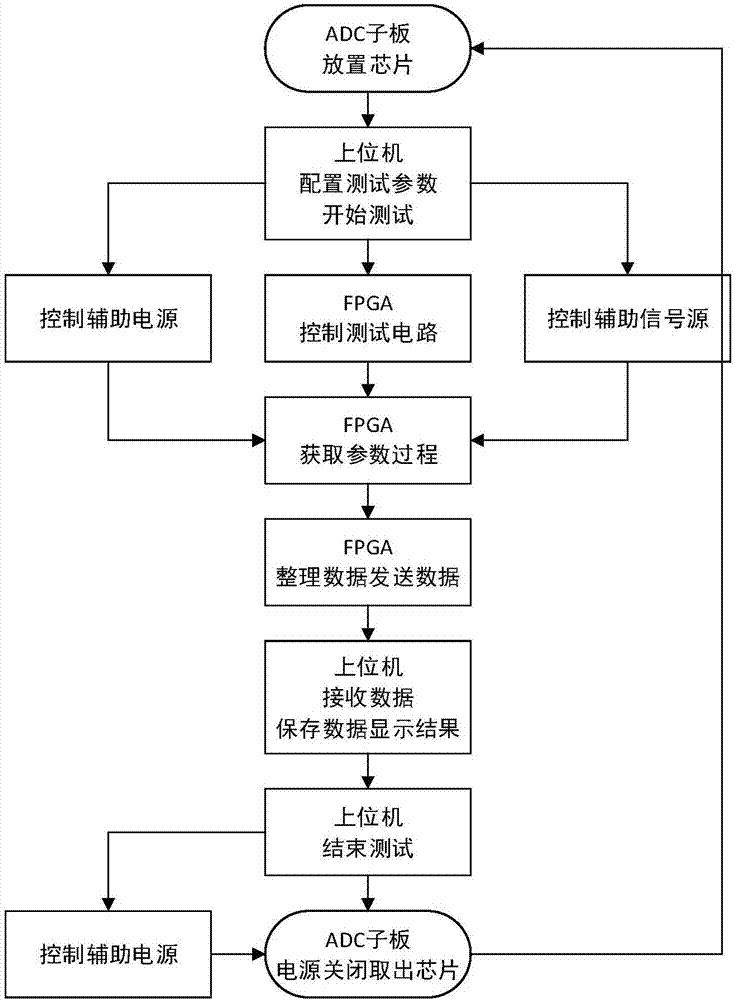

[0044] The ADC sub-board includes the ADC chip placement test socket, the basic working circuit of the chip and the chip interface that leads out. The device for placing the ADC chip is used to replace the ADC chip. After testing one ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More