A wafer-level fan-out packaging structure and packaging method

A technology of packaging structure and packaging method, which is applied in the direction of semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of poor electrical performance and poor electromagnetic shielding function of wafer-level packaging structure, and reduce chip displacement The possibility of reducing impact and improving the effect of electrical performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

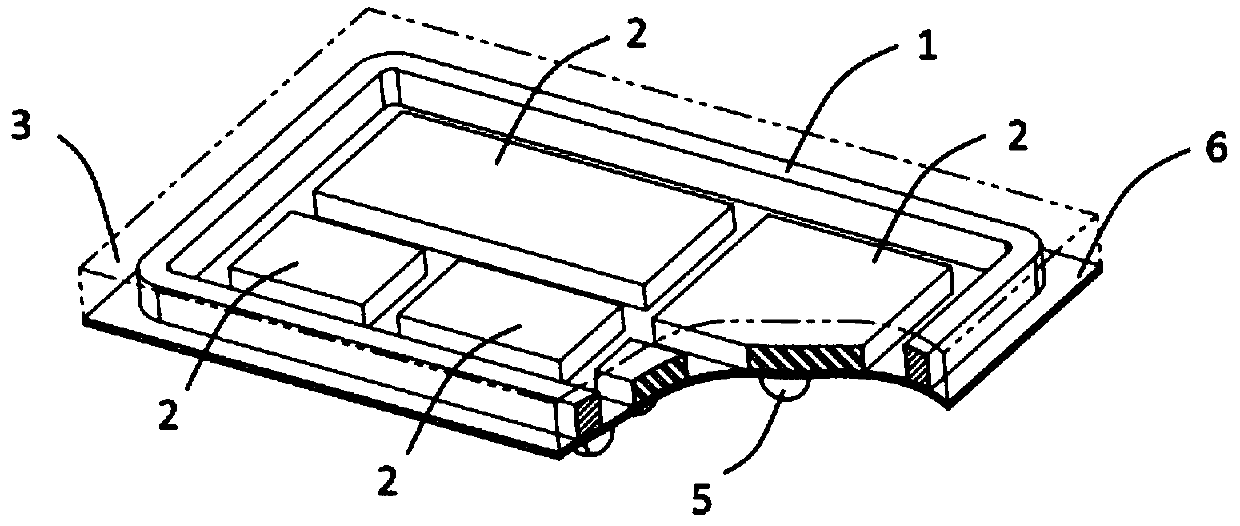

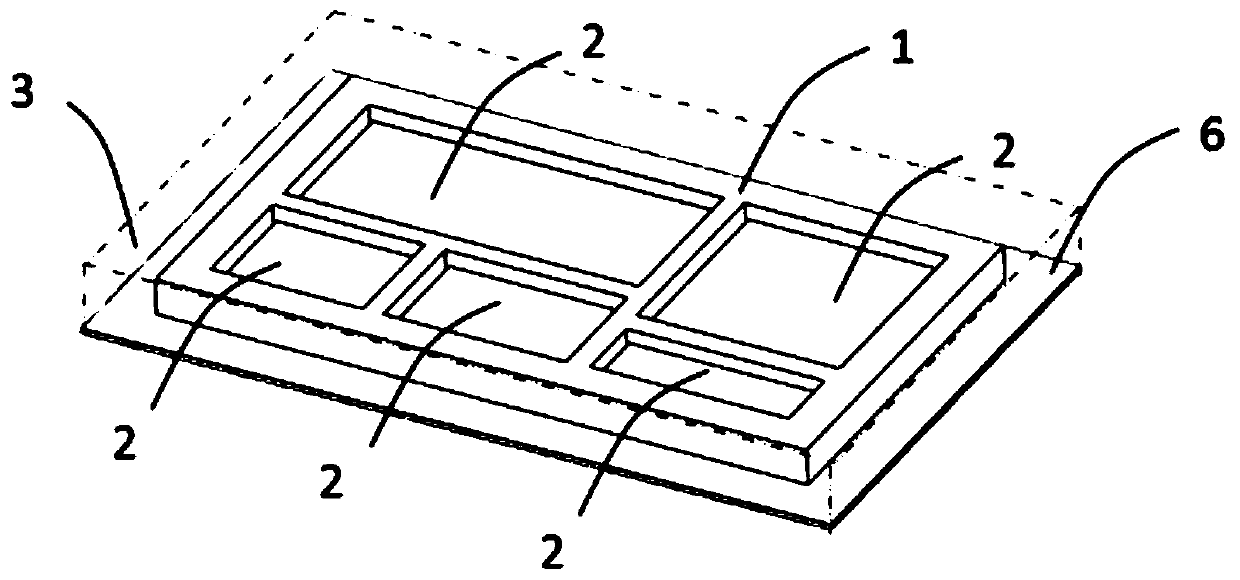

[0040] The embodiment of the present invention discloses a wafer-level fan-out packaging structure, please refer to figure 1 , figure 1 It is a schematic diagram of a three-dimensional structure of a wafer-level fan-out packaging structure disclosed in an embodiment of the present invention, including: a frame 1, which is used to place one or more chips 2; the frame 1 is connected to the ground; the package body 3. The frame 1 and the chip 2 are packaged in the package 3; the lower surface of the package 3 is located on the same plane as the lower surface of the frame 1 and the device surface of the chip 2. In this embodiment, the coefficient of linear expansion of the frame 1 is greater than that of the chip 2, and the frame 1 is a high-rigidity frame. Specifically, the material of the frame 1 is a metal conductor, such as copper, aluminum, alloy, etc. or the surface is plated with Metallic ceramic materials. Ground the metal or the metal-plated frame 1 so that the package ...

Embodiment 2

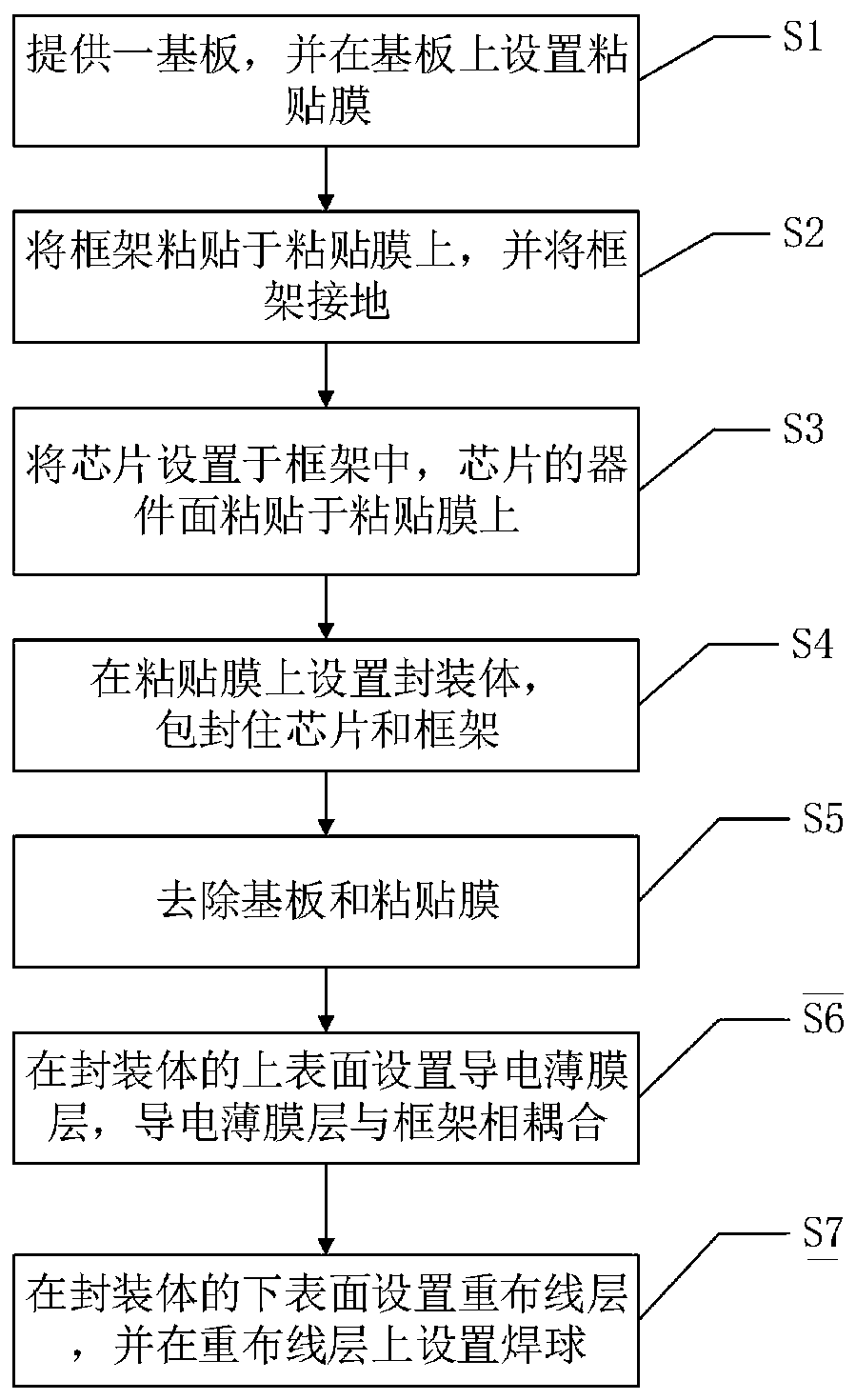

[0052] The embodiment of the present invention discloses a wafer-level fan-out packaging method, please refer to image 3 , image 3 A process flow chart of a wafer-level fan-out packaging method disclosed in this embodiment includes the following steps:

[0053] Step S1: providing a substrate, and setting an adhesive film on the substrate. Please refer to Figure 4 , Figure 4 It is a schematic diagram of setting an adhesive film on a substrate disclosed in an embodiment of the present invention. In this embodiment, the material of the substrate 7 can be a metal substrate or a glass substrate, and the adhesive film 8 can be a heat-peelable adhesive or a UV adhesive film. In a specific embodiment, the adhesive film 8 may be disposed on the substrate 7 by means of spray coating, spin coating, or film sticking. Preferably, the thickness of the adhesive film 8 is less than 100 um.

[0054] Step S2: Paste the frame on the adhesive film, and ground the frame. Please refer to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com