Electrostatic discharge protection circuit and manufacturing method thereof

A technology of electrostatic discharge protection and manufacturing method, which is applied in the direction of circuits, electrical components, electric solid devices, etc., can solve the problems of reducing the ESD protection ability of GGNMOS, uneven heat distribution, and reducing the service life of integrated circuits, so as to improve ESD protection effect of ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

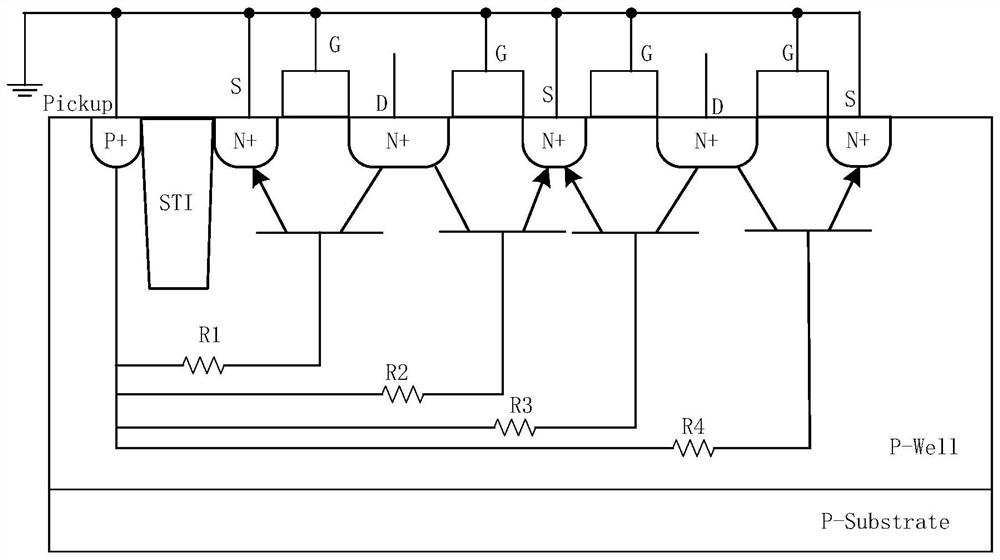

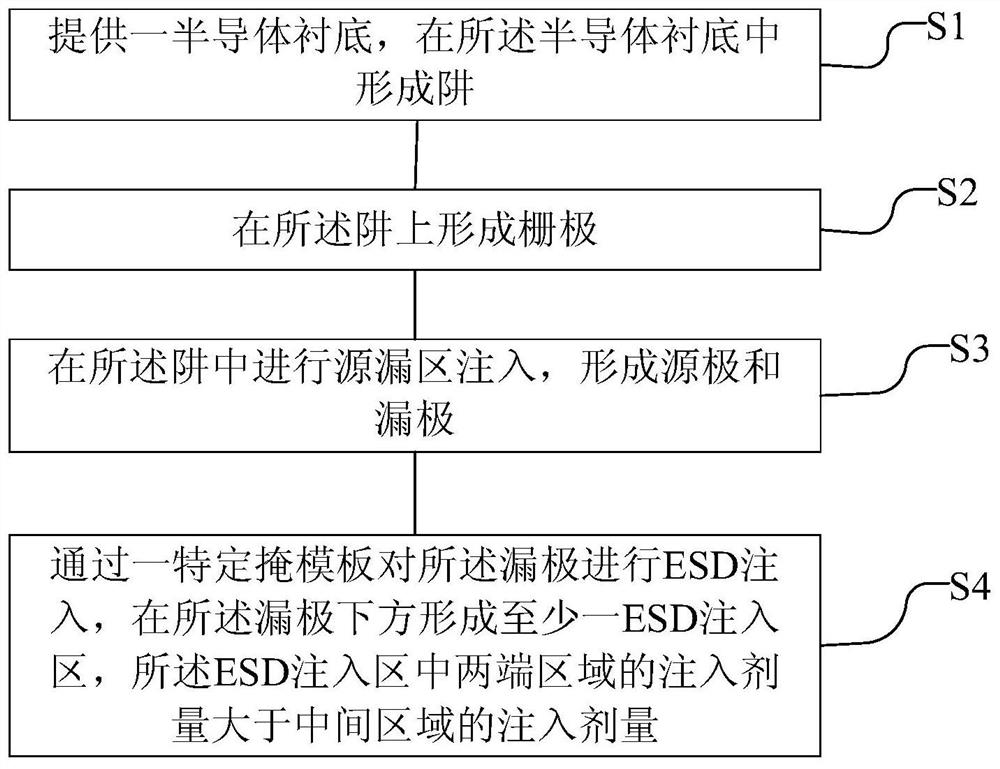

[0065] see Figure 2-Figure 7 , first, as figure 2 As shown, step S1 is performed to provide a semiconductor substrate, and a well is formed in the substrate. The selected semiconductor substrate in this embodiment is a P-type semiconductor substrate (P-Substrate), and the P-type semiconductor P-Well is formed in the substrate.

[0066] Then, execute step S2, such as Figure 4 As shown, a gate 13 is formed on the P-Well, and the formation of the gate 13 is polysilicon deposited by selective etching. The specific operation is to pass silane into the process chamber of the low-pressure chemical vapor deposition equipment, and the polysilicon generated by the decomposition of the silane is deposited on the surface of the P-Well. Then, in the photolithography area, the structure of the polysilicon gate is photoetched by deep ultraviolet lithography technology, and the polysilicon is etched by anisotropic plasma etching to form the gate 13 with a multi-finger structure.

[006...

Embodiment 2

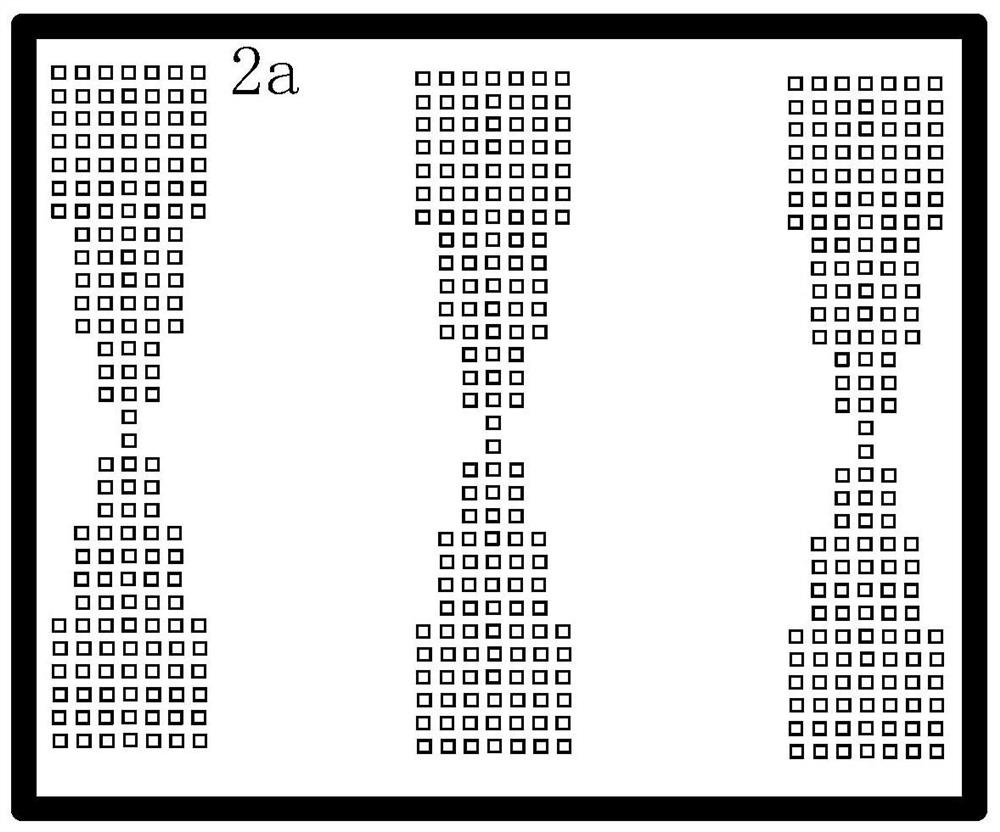

[0073] see Figure 8 , where reference numbers indicate the same Figure 2-Figure 7 The same expression and the same structure as the manufacturing method of the first embodiment. The manufacturing method of the second embodiment is basically the same as the manufacturing method of the first embodiment, the difference being that the specific mask used is different when ESD implantation is performed. In the second embodiment, at least one pair of funnel-shaped windows is provided on the specific mask plate 2b, each of the funnel-shaped windows has a large opening end and a small opening end, and each of the ESD injection regions corresponds to a pair of the The funnel-shaped window, in each pair of the funnel-shaped window, the small opening ends are oppositely arranged and correspond to the middle area of the ESD injection region, and the large opening ends are arranged opposite to each other and correspond to the two sides of the ESD injection region end area. Refer to E...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More