A fan-out wafer level chip packaging structure and packaging method

A wafer-level chip and packaging structure technology, which is applied in semiconductor/solid-state device parts, semiconductor devices, electrical components, etc., can solve the problems of high production cost and difficult preparation of fan-out wafer-level chip packaging structure, etc. Achieve the effect of less difficulty in preparation, improve heat dissipation performance, and improve manufacturing precision

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

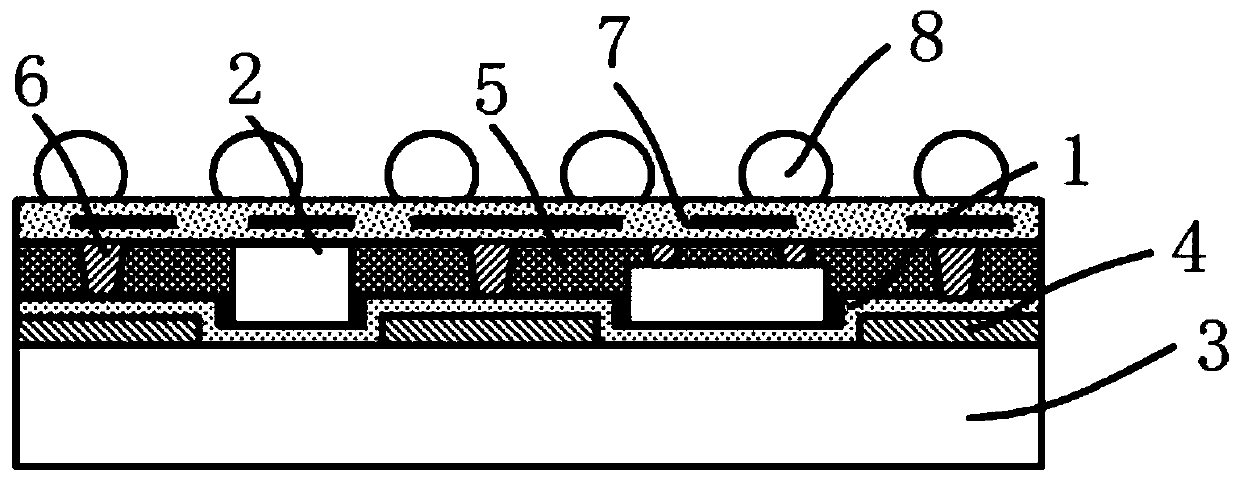

[0032] This embodiment provides a fan-out wafer level chip packaging structure, such as figure 1 As shown, it includes: conductive layer 1, a groove for setting chip 2 is formed on conductive layer 1; conductive layer 1 is arranged on substrate 3; insulating layer 4 is arranged between conductive layer 1 and substrate 3 for filling The gap between the conductive layer 1 and the substrate 3; the package 5 is arranged on the upper surface of the conductive layer 1; the chip 2 is packaged in the package 5, and the pad of the chip 2 is exposed outside the package 5; the conductive column 6 is set In the package body 5 , one end is coupled to the conductive layer 1 , and the other end is exposed outside the package body 5 ; the conductive post 6 is connected to the ground wire. In a specific embodiment, the depth of the groove is smaller than the thickness of the chip 2, and the conductive layer 1 is aluminum, copper, aluminum alloy or copper alloy layer. Preferably, the thickness ...

Embodiment 2

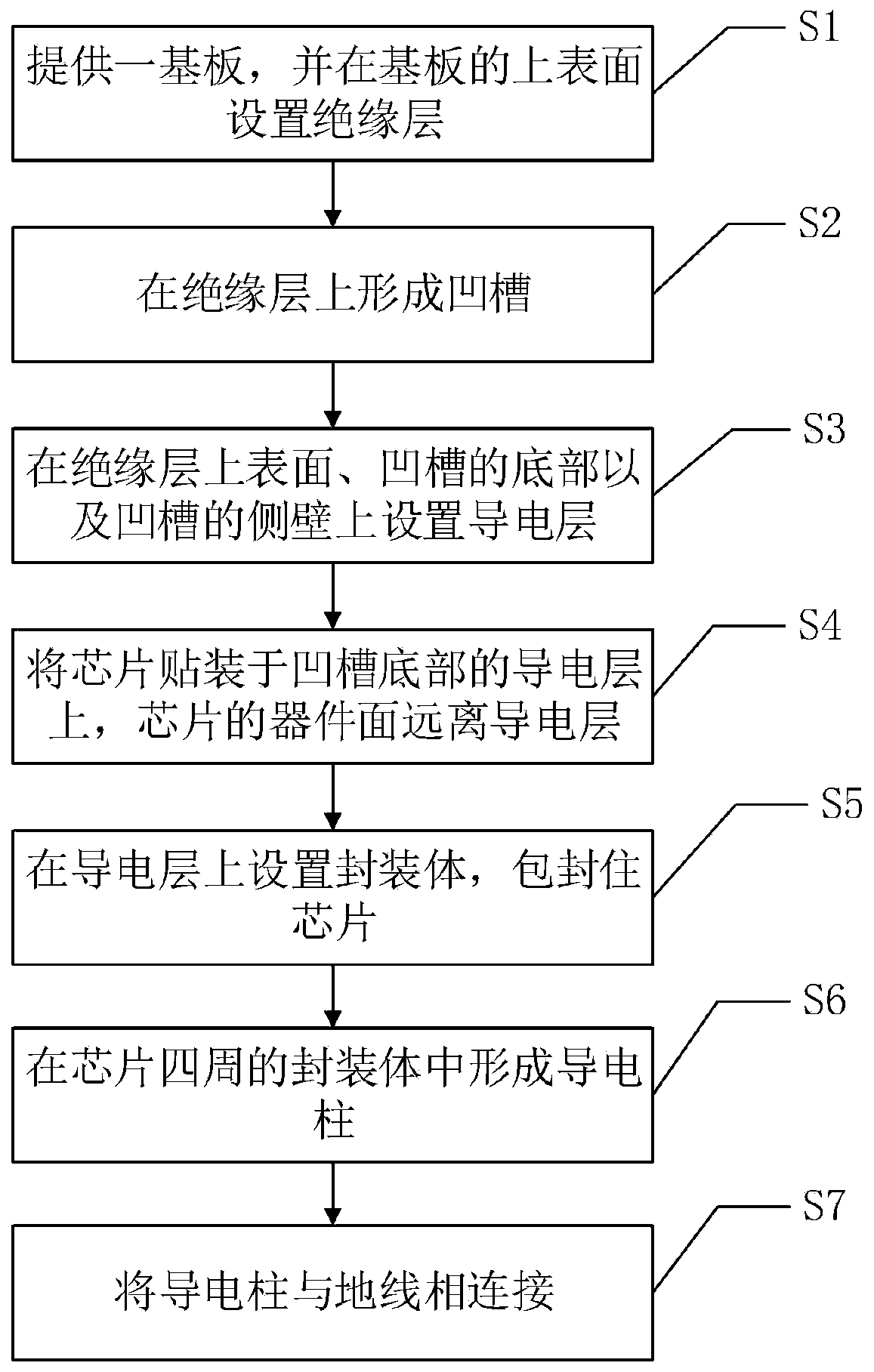

[0040] This embodiment provides a fan-out wafer level chip packaging method, such as figure 2 As shown, including the following steps:

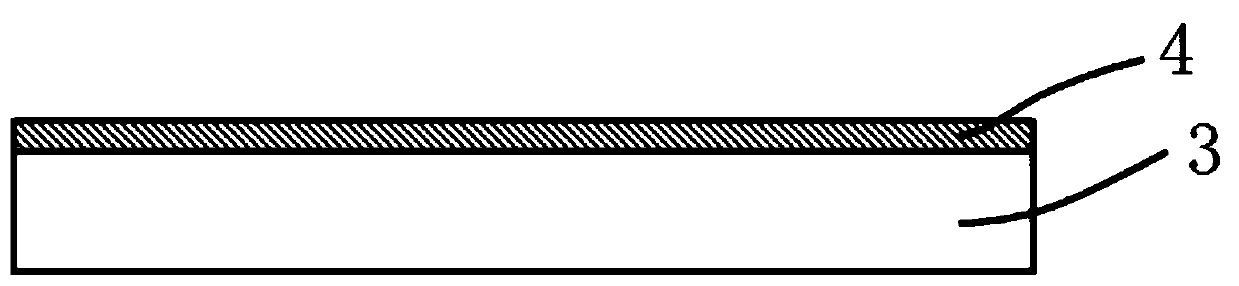

[0041] Step S1: providing a substrate, and disposing an insulating layer on the upper surface of the substrate. Such as image 3 As shown, in this embodiment, the insulating layer 4 may be provided by spray coating or spin coating. In a specific embodiment, the material of the substrate 3 is a material with good thermal conductivity such as silicon, silicon carbide, thermally conductive ceramics or metal, and the insulating layer 4 is a photosensitive material layer prepared by photosensitive polyimide or other photosensitive resins. Of course, it can also be a non-photosensitive material layer. Preferably, the thickness of the insulating layer 4 is 2-20um.

[0042] Step S2: forming grooves on the insulating layer. Such as Figure 4 As mentioned above, in a specific embodiment, when the insulating layer 4 is a photosensitive material la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More