A kind of semiconductor device with super junction structure and its manufacturing method

A semiconductor and device technology, applied in the field of semiconductor devices with a superjunction structure and their fabrication, can solve the problems affecting the conduction performance of the device, low saturation current, and large on-resistance of the device, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

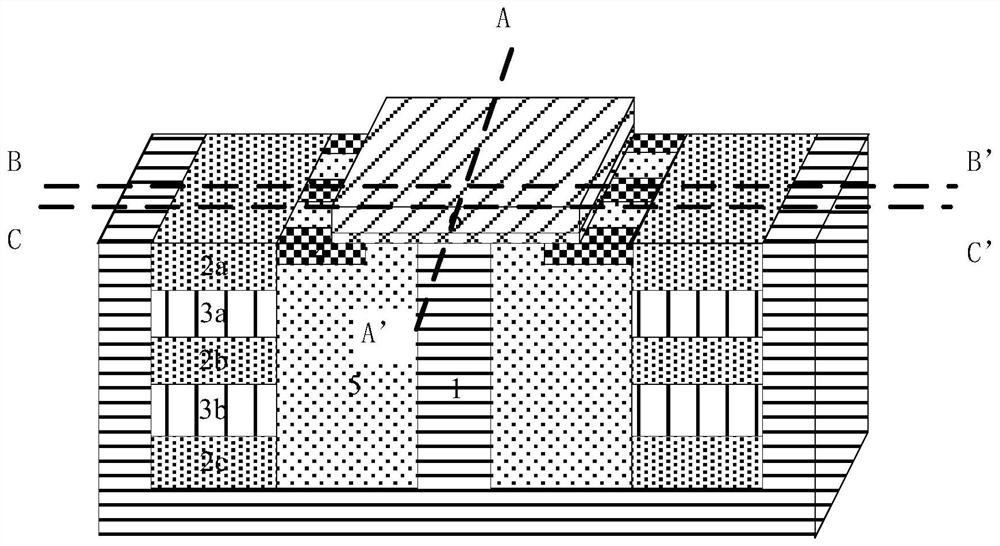

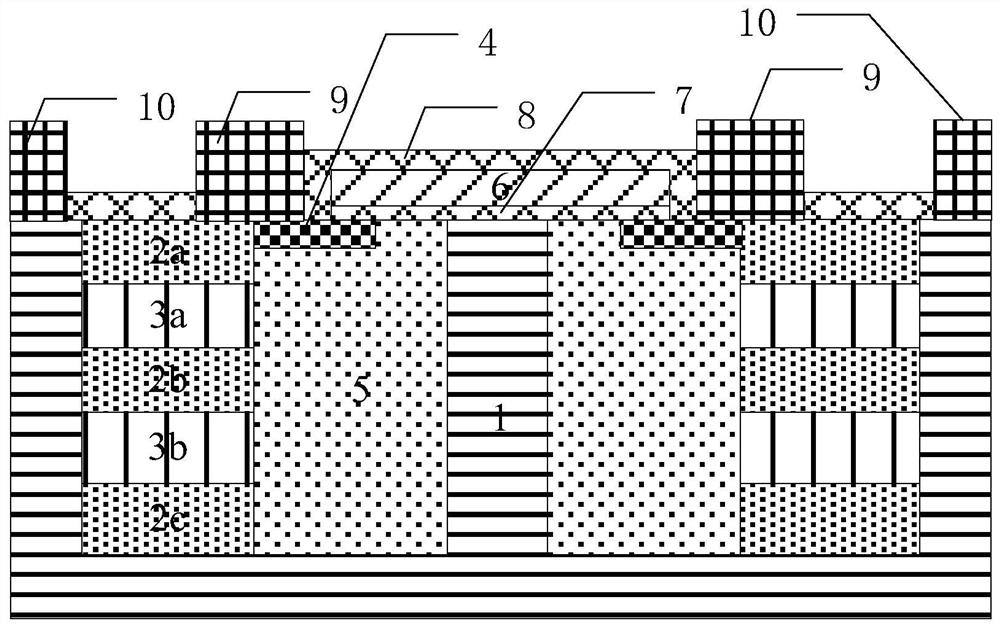

[0045] see Figure 1 to Figure 4 , a three-dimensional structure diagram and an internal cross-sectional diagram of a semiconductor device with a superjunction structure provided by an embodiment of the present invention. A semiconductor device with a superjunction structure provided by an embodiment of the present invention includes: an N-type substrate (not shown in the figure), an N+ region 1, a P-body region 5, a PN alternating superjunction region, and an N+ source region 4 , gate oxide layer 7, polysilicon gate 6, dielectric layer isolation 8, device source metal 9 and device drain metal 10. Wherein, the N+ region is an electron drift region composed of a central region, a bottom region and a side region. The cross-section of the side area is "mouth", the cross-section of the central area is "one", located in the center of the side area, and the bottom area is square, located at the bottom of the device.

[0046] The top of the N-type substrate is connected to the bott...

Embodiment 2

[0059] A method for manufacturing a semiconductor device with a super junction structure provided by an embodiment of the present invention includes:

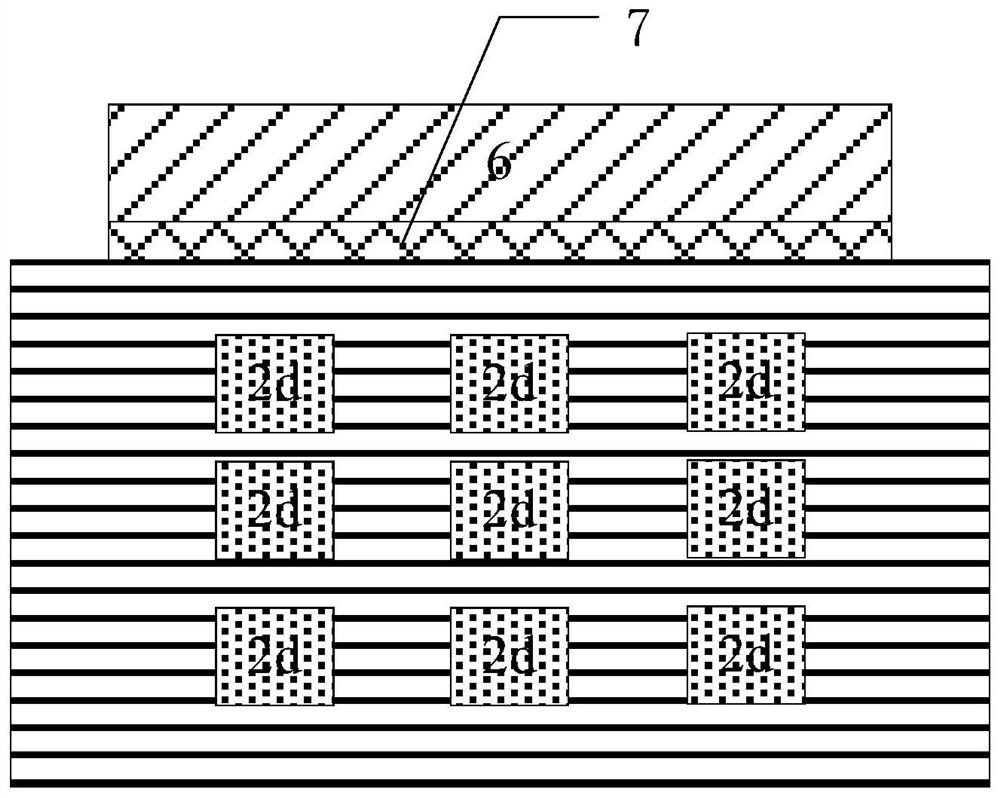

[0060] Step S1: providing an N-type substrate, forming an N+ epitaxial layer on the upper surface of the N-type substrate, forming a P- epitaxial layer on the upper surface of the N+ epitaxial layer, and performing surface planarization after epitaxy. see Figure 6 , a product schematic diagram of step S1 in the method for manufacturing a semiconductor device with a super junction structure provided by an embodiment of the present invention.

[0061] Step S2: forming deep trenches on both sides of the P- epitaxial layer, the bottom of the deep trenches extending to the upper surface of the N+ epitaxial layer. see Figure 7 , a product schematic diagram of step S2 in the method for manufacturing a semiconductor device with a super junction structure provided by an embodiment of the present invention.

[0062] Step S3: forming...

PUM

| Property | Measurement | Unit |

|---|---|---|

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More