Design method of master/slave station cards for implementing Powerlink industrial real-time Ethernet communication

A design method and Ethernet technology, applied in the bus network, data exchange network, data exchange through path configuration, etc., can solve the problems of large signal transmission jitter, unstable transmission, slow transmission rate, etc., to improve real-time, The effect of improving communication speed and saving cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

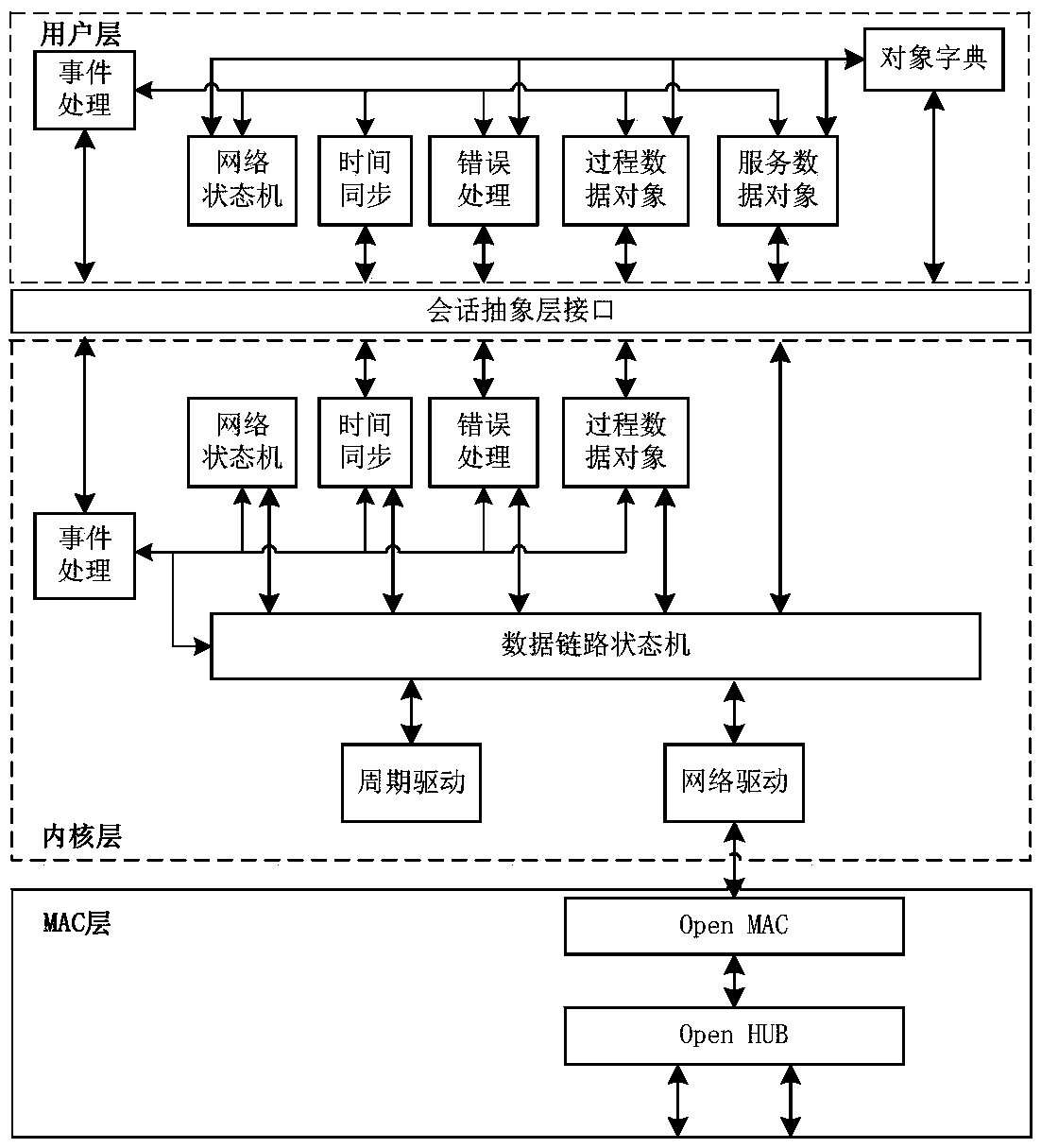

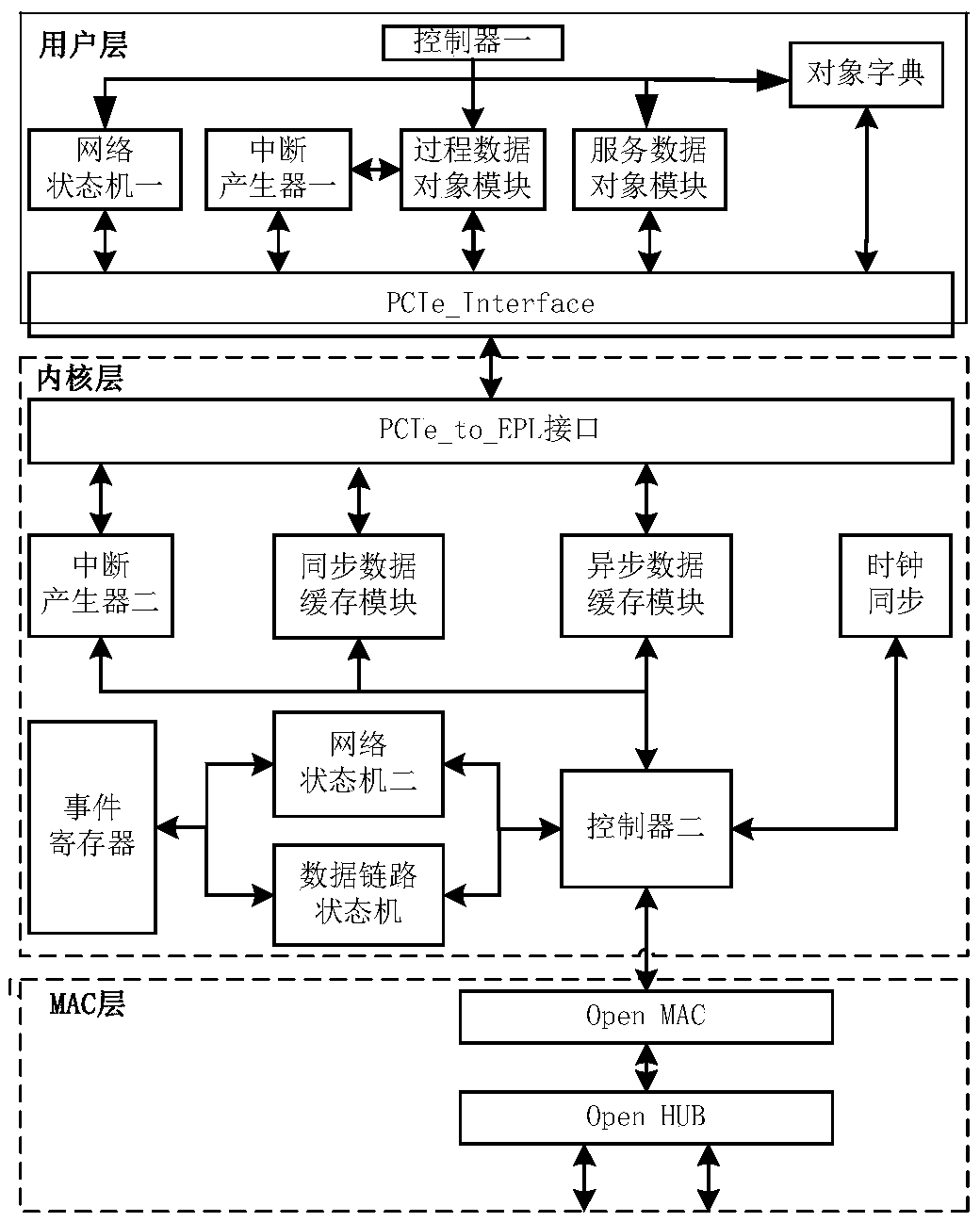

[0042] see figure 2 , the Powerlink master / slave station card model diagram of the present invention, and figure 1 In contrast, when the present invention designs and realizes the master / slave station card of Powerlink industrial real-time Ethernet communication, Powerlink industrial real-time Ethernet communication model is made up of user layer+Powerlink industrial real-time Ethernet communication IP core (hereinafter referred to as IP core), wherein IP core = kernel layer + MAC layer, and the communication between the user layer and the IP core is realized through the CAL interface in each layer. The user layer contains the CAL interface—PCIe interface, and the IP core contains the CAL interface——PCIe_to_EPL. figure 2 The CAL interface shown is a high-speed serial communication interface. In order to ensure synchronous communication, a synchronous data cache and asynchronous data cache software modules are designed in the IP core.

[0043] The event register module of t...

Embodiment 2

[0069] For the design method of the master / slave station card realizing Powerlink industrial real-time Ethernet communication in embodiment 1, its functional structure and design method are as follows.

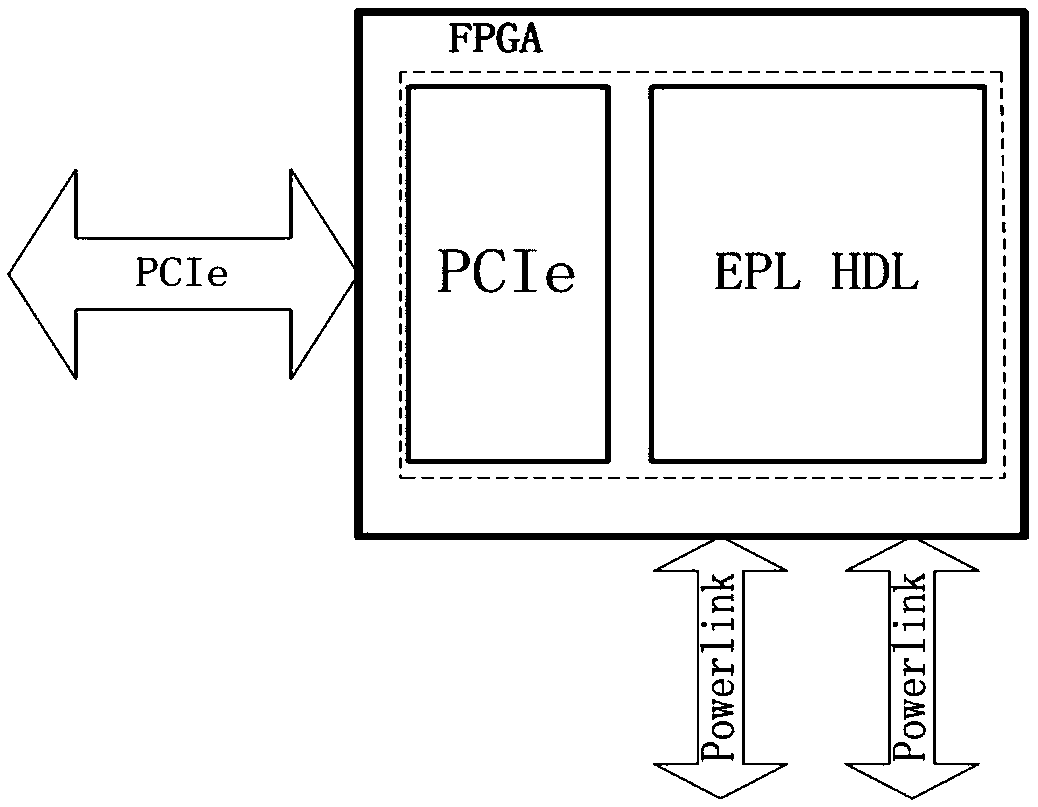

[0070] Step 1: The main control chip of the card is composed of FPGA, and other main electronic components include: power management chip, network transceiver physical layer PHY, FLASH chip, DDR3 memory, clock chip, etc.

[0071] For example, select an FPGA chip supporting the PCIe high-speed serial interface, and use a hardware description language to construct the kernel layer and the Mac layer of the Powerlink protocol stack (master / slave station) inside the FPGA.

[0072] It is the key technology that the kernel layer of Powerlink master / slave station adopts HDL hardware description language to realize. The core layer of the master station is mainly the core of the master station, which includes data sending and receiving buffer module, interrupt generation module, timer m...

Embodiment 3

[0090] For the design method of the master / slave station card realizing Powerlink industrial real-time Ethernet communication in embodiment 1, the following detailed scheme is provided.

[0091] 1. Program analysis

[0092] (1) Program structure

[0093] The structure of the Powerlink master / slave station card in this scheme is as follows image 3 As shown, the block diagram of the internal functional modules of the Powerlink master / slave card and the upper computer is as follows Figure 4 shown. The core layer and MAC layer of the Powerlink protocol stack are completed in the card FPGA through logic code, and then connected to the CPU of the host computer through the PCIe interface, and the host computer runs the user layer code of the Powerlink protocol stack. The master card is connected to the PCIe female socket of the network card in the PC through the PCIe golden finger, and then the host computer can use the two Powerlink Ethernet ports of the board to communicate wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More