Design method of high-power vertical tiled multi-channel digital transceiver sub-array

A design method and high-power technology, which is applied to the design of two-dimensional active digital phased array radar transceiver components or transceiver sub-arrays, in the field of radar, to achieve excellent platform adaptability, easy disassembly and maintenance, and save carrier space.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] The present invention will now be further described in conjunction with the embodiments and accompanying drawings:

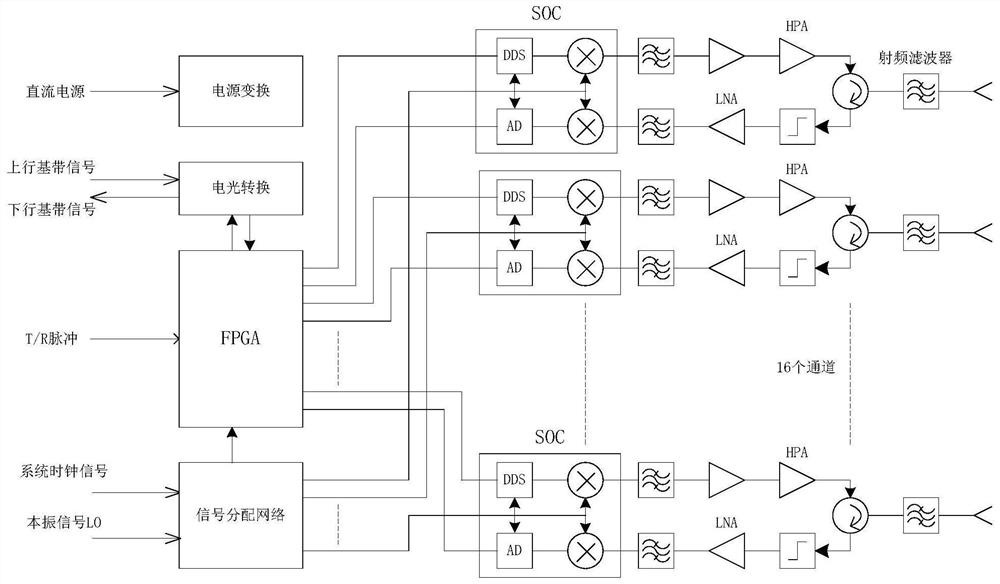

[0023] The principle block diagram of the high-power vertical tiled multi-channel digital transceiver sub-array according to the present invention is as follows: image 3 As shown, the uplink baseband signal is phase-controlled by the FPGA, together with the system clock signal and the local oscillator signal LO through the SOC to generate the emission excitation signal, which is sent to the antenna radiation unit through the power amplifier, circulator and RF filter; the target received by the antenna is reflected back The wave signal is sent to the SOC with low noise through the radio frequency filter, circulator and limiter, and is processed by down-conversion with the local oscillator signal LO inside the SOC to generate a digital received signal.

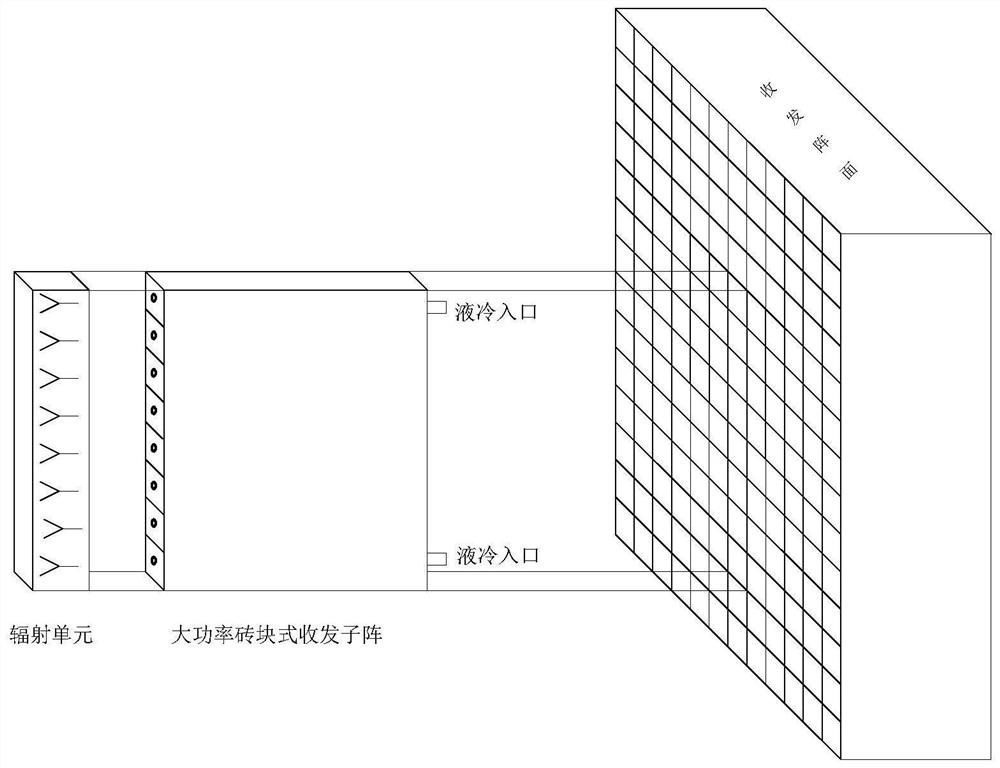

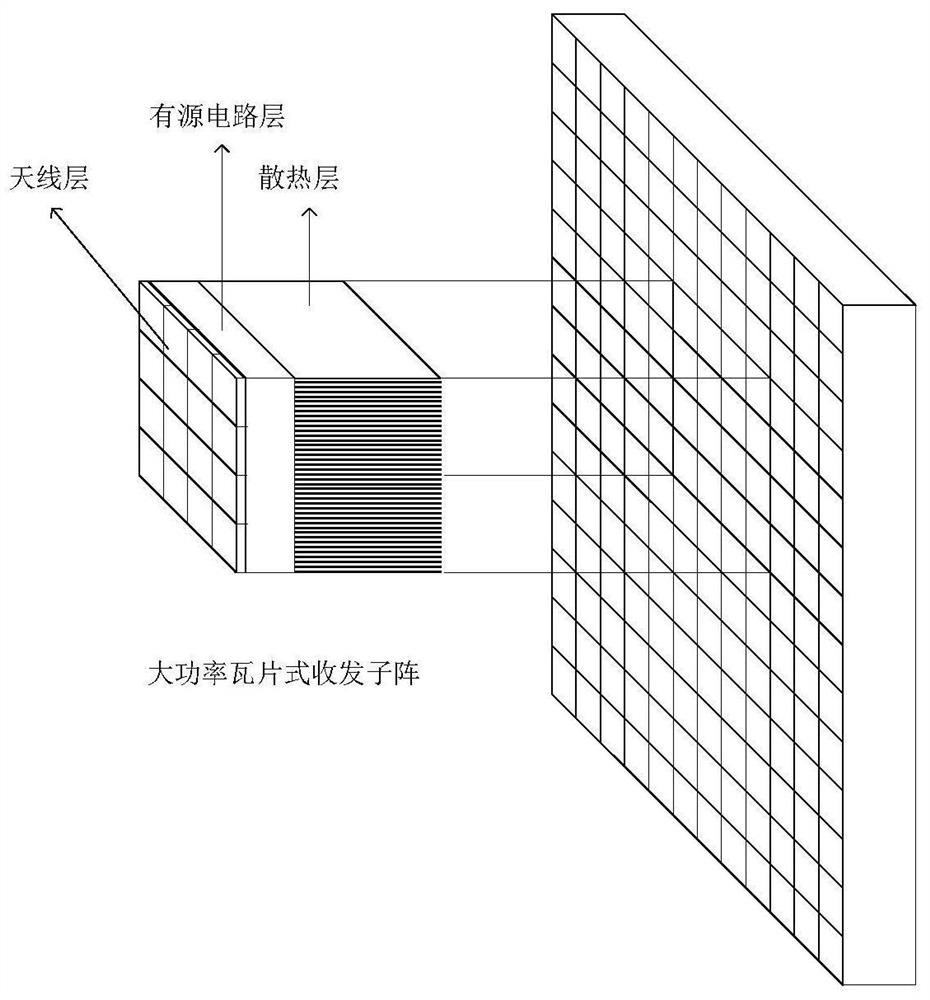

[0024] The vertical tile-type integration method of the present invention requires that the transceiver...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More