32-bit MCU chip test system and test method thereof

A technology of chip testing and testing methods, which is applied in automated testing systems, electronic circuit testing, electrical measurement, etc., can solve problems such as difficulty in yield analysis, low effective accuracy of multiple simulation indicators, and undisclosed serial port configuration instructions of communication protocols. , to achieve high-quality production testing requirements, save personnel efficiency costs, and achieve good user experience effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0046] To achieve the above object, the technical scheme of the present invention is as follows:

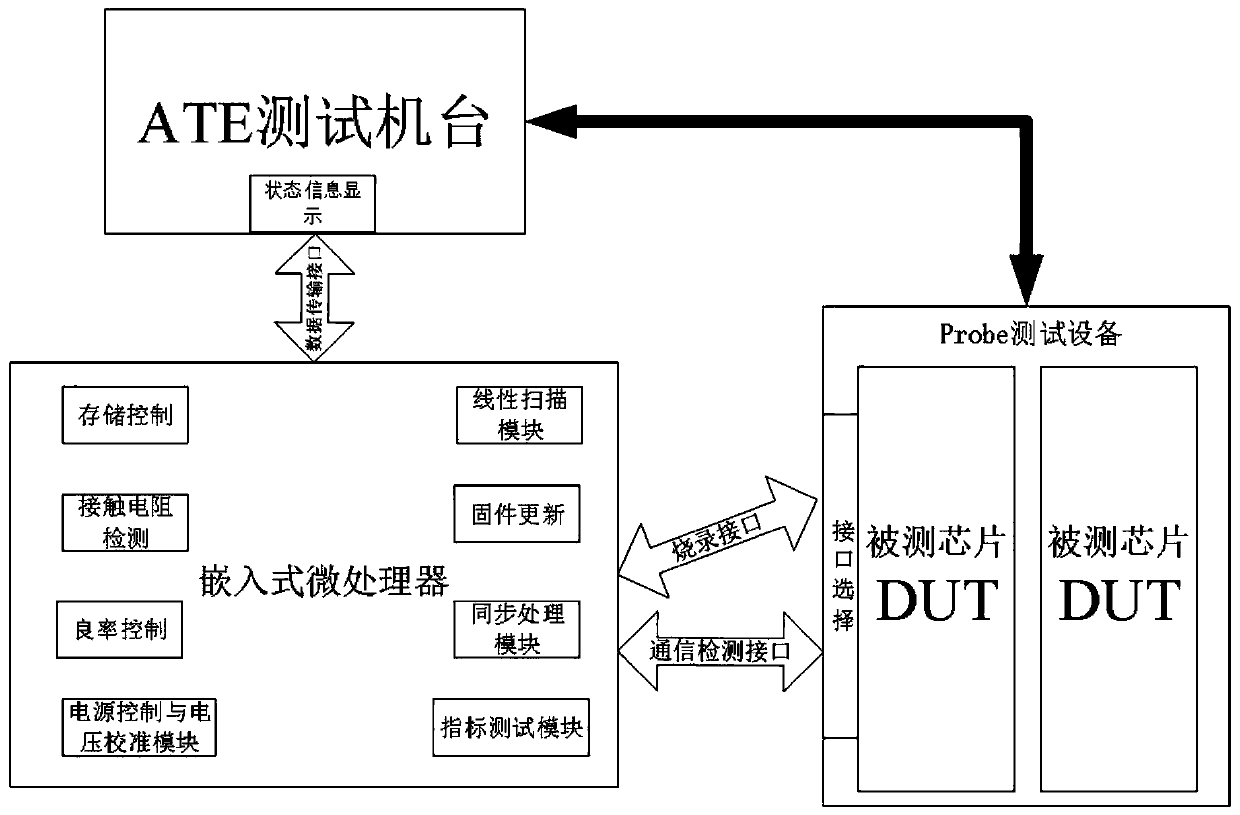

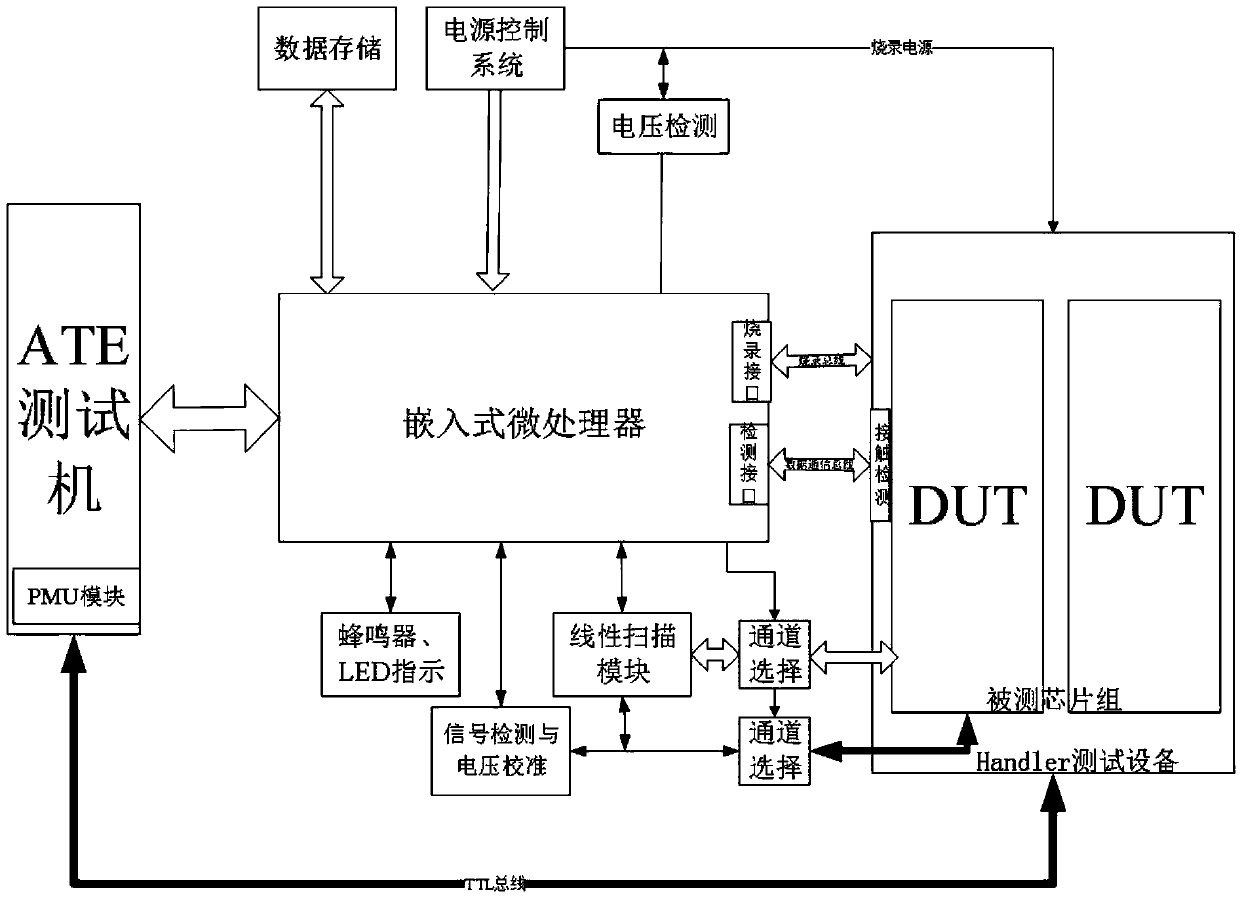

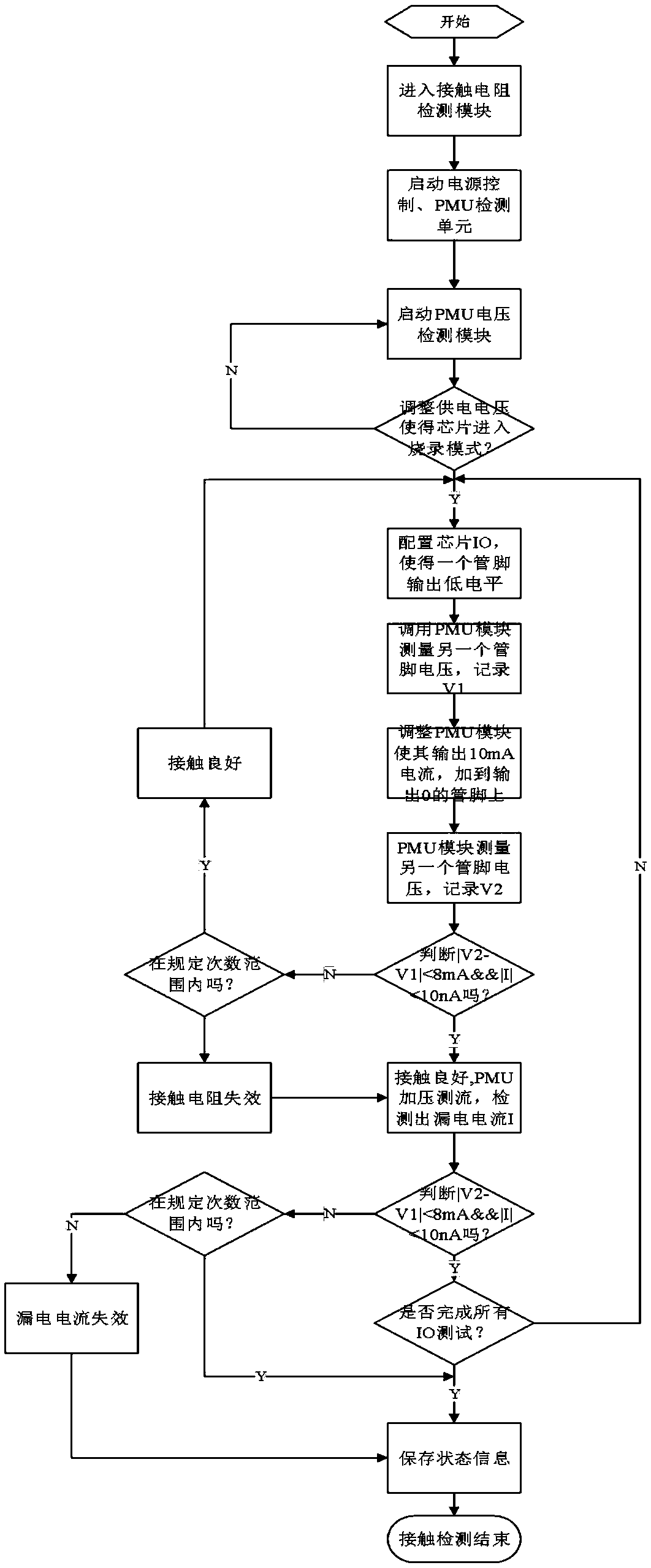

[0047] see Figure 1-2 As shown, the 32-bit MCU chip test system realized by the present invention includes an ATE test machine and an embedded microprocessor, and the ATE test machine is connected with the embedded microprocessor through a data transmission interface; the embedded microprocessor There are: a control module used to complete the core calculation and control functions, and a multi-power management module configured to complete the supply of various types of programming voltage and supp...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More