VCSEL chip and preparation method thereof

A chip and confinement layer technology, applied in the field of VCSEL, can solve the problems of high photon confinement and carrier confinement at the same time, small carrier gain, complex process, etc., to improve fundamental mode capability and reduce edge mode The effect of producing and reducing the absorption of impurities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

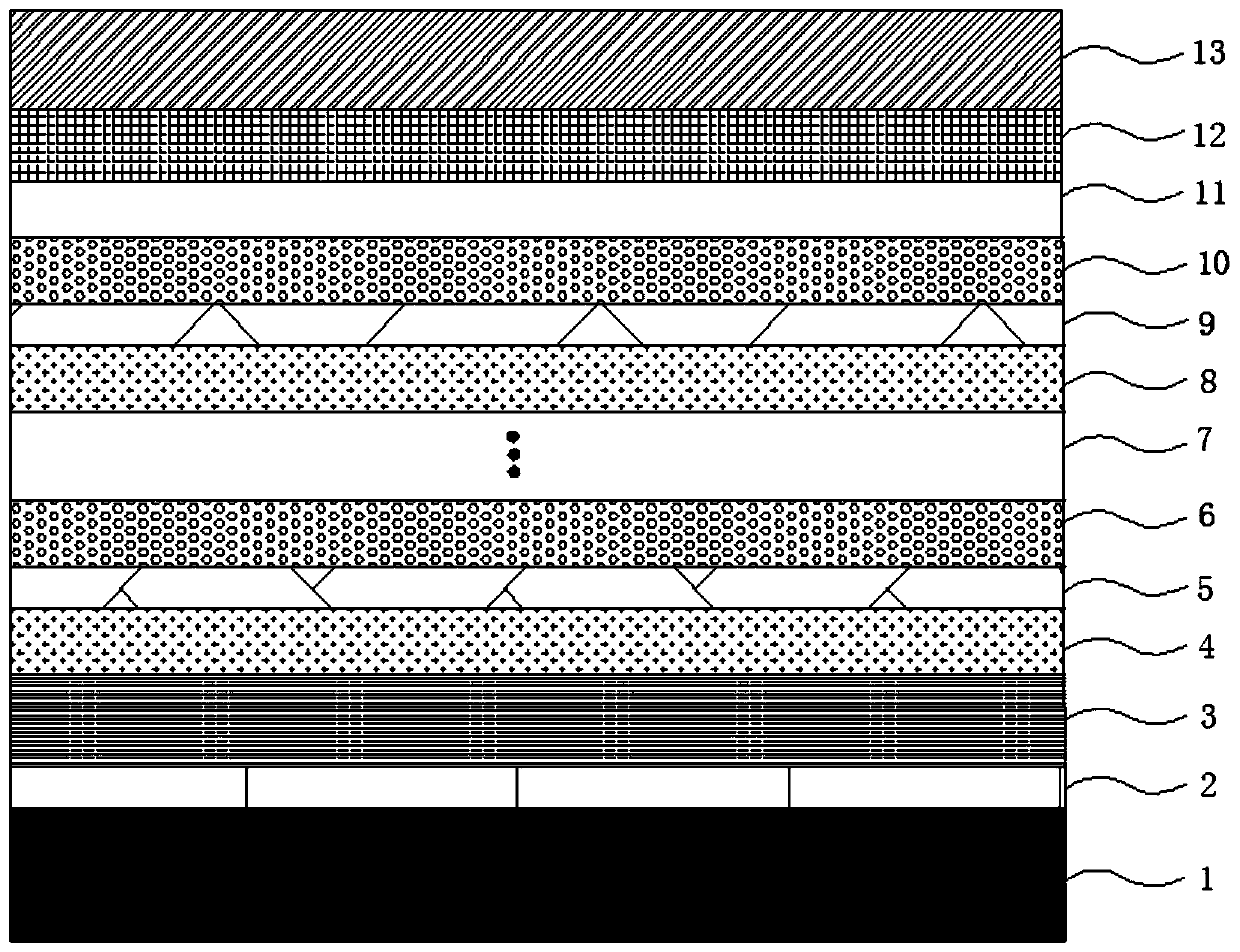

[0055] Such as figure 1 Shown, a kind of preparation method of VCSEL chip comprises:

[0056] Provide a substrate 1;

[0057] On the surface of the substrate 1, a buffer layer 2, an N-type DBR layer 3, an N-type confinement layer 4, a first waveguide layer 5, a second waveguide layer 6, a quantum well 7, a second symmetric waveguide layer 8, and a first symmetric waveguide are sequentially grown. Layer 9, P-type confinement layer 10; N-type confinement layer 4, first waveguide layer 5, second waveguide layer 6, second symmetric waveguide layer 8, first symmetric waveguide layer 9, P-type confinement layer 10 all include Al x GaAs layer, where X is the elemental composition of Al, and the first waveguide layer 5 and the first symmetrical waveguide layer 9 are respectively obtained through the modulation process of gradually changing the function of the potential barrier, specifically: by passing the flow rate to the Al element respectively , Ga element flow rate and Al elemen...

Embodiment 2

[0091] Such as figure 1 Shown, a kind of preparation method of VCSEL chip comprises:

[0092] Provide a substrate 1;

[0093] On the surface of the substrate 1, a buffer layer 2, an N-type DBR layer 3, an N-type confinement layer 4, a first waveguide layer 5, a second waveguide layer 6, a quantum well 7, a second symmetric waveguide layer 8, and a first symmetric waveguide are sequentially grown. Layer 9, P-type confinement layer 10; N-type confinement layer 4, first waveguide layer 5, second waveguide layer 6, second symmetric waveguide layer 8, first symmetric waveguide layer 9, P-type confinement layer 10 all include Al x Ga y In z In the P layer, X is the elemental composition of Al, and the first waveguide layer 5 and the first symmetrical waveguide layer 9 are respectively obtained through the modulation process of gradually changing the function of the potential barrier, specifically: by passing the flow rate to the Al element respectively , Ga element flow rate and...

Embodiment 3

[0127] Such as figure 1 Shown, a kind of preparation method of VCSEL chip comprises:

[0128] Provide a substrate 1;

[0129] On the surface of the substrate 1, a buffer layer 2, an N-type DBR layer 3, an N-type confinement layer 4, a first waveguide layer 5, a second waveguide layer 6, a quantum well 7, a second symmetric waveguide layer 8, and a first symmetric waveguide are sequentially grown. Layer 9, P-type confinement layer 10; N-type confinement layer 4, first waveguide layer 5, second waveguide layer 6, second symmetric waveguide layer 8, first symmetric waveguide layer 9, P-type confinement layer 10 all include Al x In y GaAs layer, where X is the elemental composition of Al, and the first waveguide layer 5 and the first symmetrical waveguide layer 9 are respectively obtained through the modulation process of gradually changing the function of the potential barrier, specifically: by passing the flow rate to the Al element respectively , Ga element flow rate and Al ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More