A three-dimensional stacked integrated structure and its multi-chip integrated structure and preparation method

A multi-chip integration and chip technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problem of high interface leakage, achieve good passivation performance, high vertical interconnection density, and conductance high rate effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0063] The present invention is a multi-chip integrated structure. A plurality of chips are buried in a substrate with conductive through holes to form a structure of reconstructed chips. The substrate can be silicon or glass; when the substrate shown is a silicon base In the case of sheet 1, the conductive via is a conductive via 17 passing through silicon, that is, a TSV (Through-Silicon-Via) hole; when the substrate shown is a glass substrate 31, the conductive via is through The conductive through hole 32 of the glass, that is, the TGV (Through-Glass-Via) hole;

[0064] There are external pin arrays on the upper and lower surfaces of the above-mentioned reconstructed chip, and at the same time, according to product requirements, the pins in the external pin arrays on the upper and lower surfaces can be electrically connected.

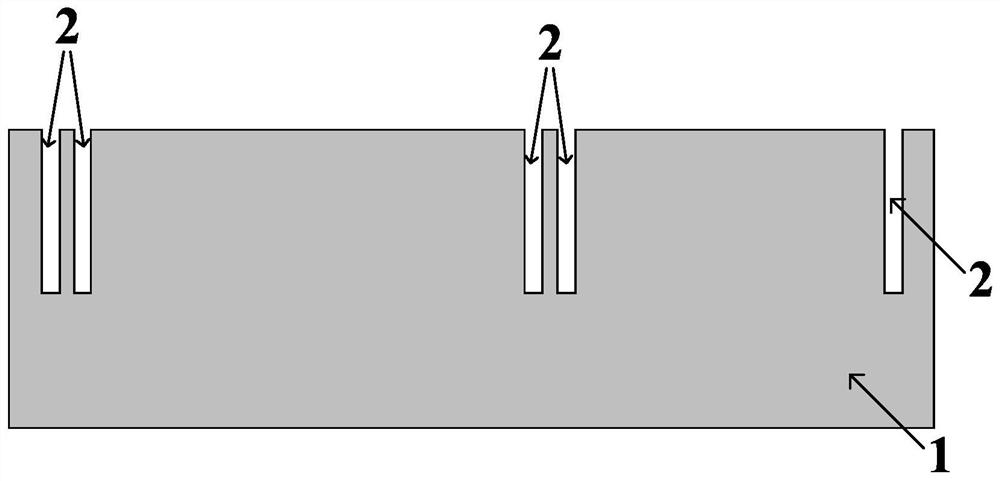

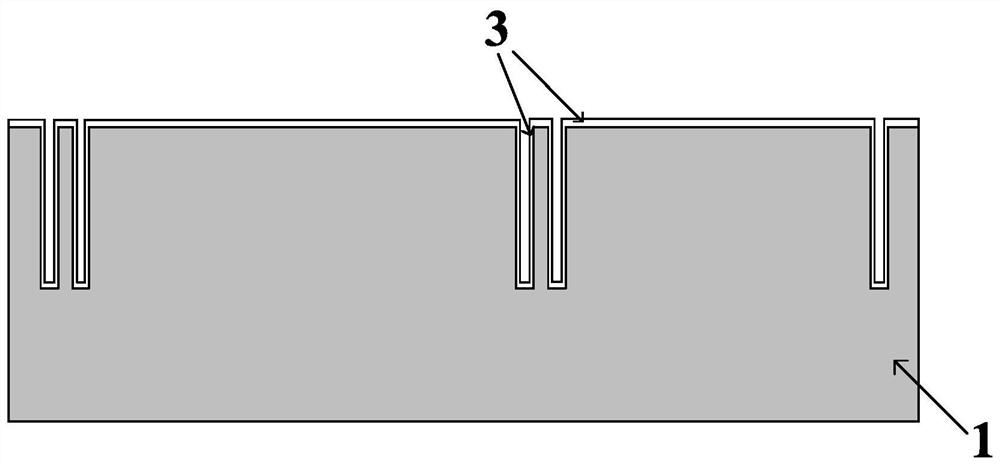

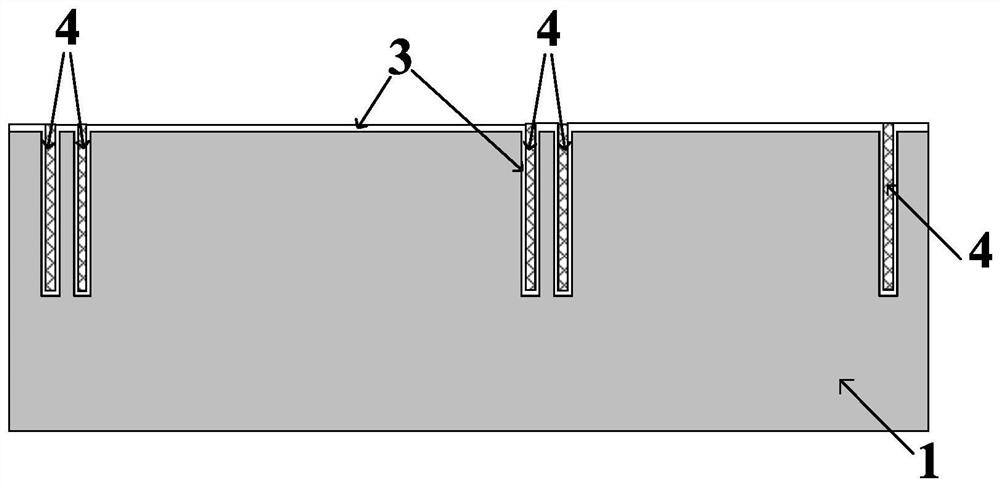

[0065] Taking the silicon wafer as the substrate as an example, it includes:

[0066] First, a conductive blind hole 4 is prepared on one side of ...

Embodiment 2

[0116] A kind of multi-chip integrated structure of the present invention, the substrate that embeds chip can be glass substrate 31, as attached Figure 14 As shown, is a schematic cross-sectional view of a glass-based reconstitution chip 300,

[0117] The first chip 13 and the second chip 14 are respectively buried in a glass substrate 31 with conductive vias (TGV) 32 passing through the glass to form a glass-based reconstitution chip 300 . Because the glass is transparent and has good high-frequency characteristics, the embedding and reconstruction of chips in the glass substrate 31 has great application potential in high-frequency high-speed, microwave, radio frequency circuits and optoelectronic systems;

[0118]Wherein, because the glass is not conductive, no additional dielectric insulating layer is needed between the conductive via (TGV) 32 passing through the glass on the glass substrate 31 and the glass substrate 31;

[0119] The groove 30 embedded in each chip on th...

Embodiment 3

[0122] A three-dimensional stacked integrated structure in the present invention, such as Figure 15 shown.

[0123] After two or more of the above-mentioned multi-chip reconfigured chips are stacked and bonded, multi-chip three-dimensional integration can be formed; the above-mentioned multi-chip reconfigured chips can also be used as an active transfer substrate, and ordinary chips can also be directly bonded to The above-mentioned multi-chip is reconstructed on the chip to form a three-dimensional integration. The bonding of ordinary chips on the above-mentioned multi-chip two-dimensional reconstruction integrated chip can be flip-chip (Flip-Chip) bonding or wire bonding, as follows:

[0124] The reconstructed chip formed by embedding the chip in a substrate with conductive through holes has an array of external pins on its upper and lower surfaces, and at the same time, according to product requirements, the pins in the array of external pins on the upper and lower surfac...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More