Readout circuit structure and working time sequence control method thereof

A readout circuit and reset control technology, which is applied in TV, electrical components, color TV, etc., can solve the problems of complex timing control of the readout circuit, loss of analog signal input, large area occupied by capacitors, etc., so as to improve chip cost Competitiveness, improved circuit accuracy, and reduced complexity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

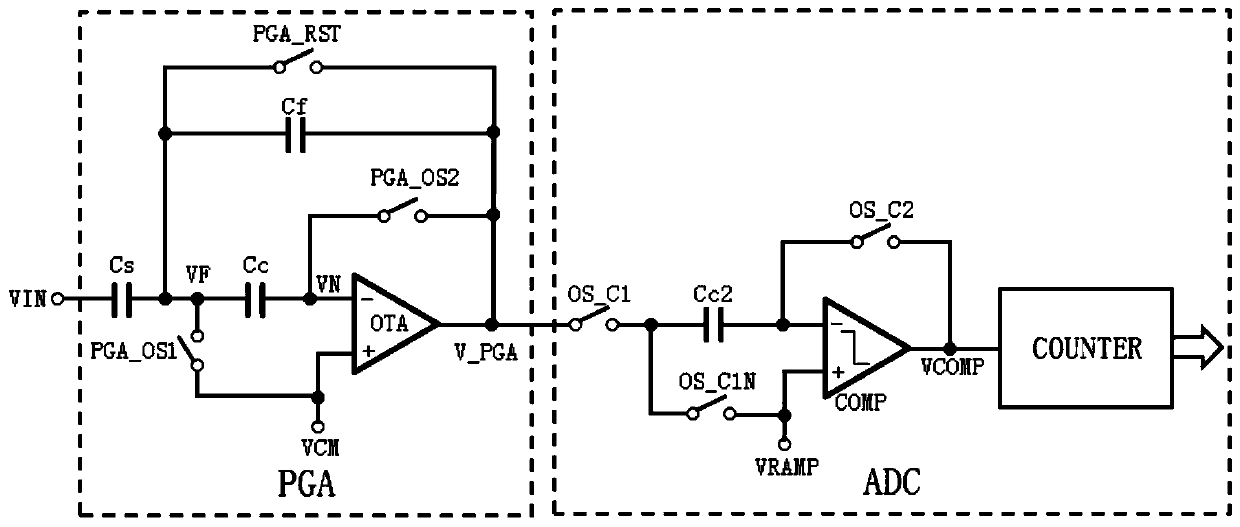

[0037] In order to make the purpose, advantages and characteristics of the present invention clearer, the following in conjunction with the attached Figure 5-7 The structure of the readout circuit proposed by the present invention and its working sequence control method are further described in detail. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

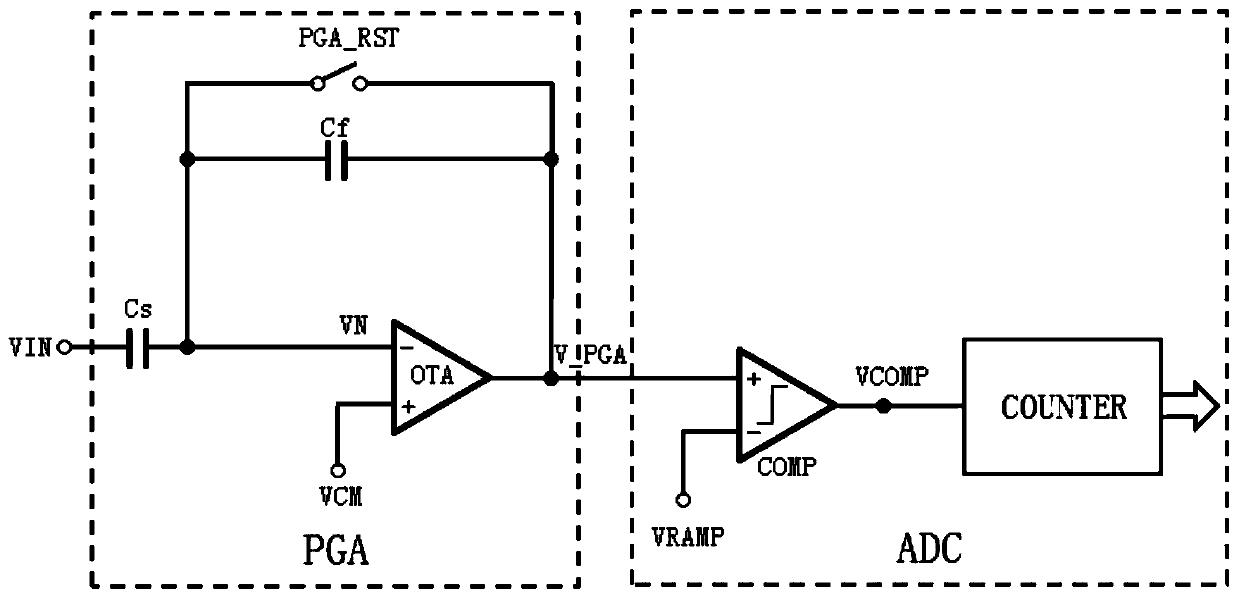

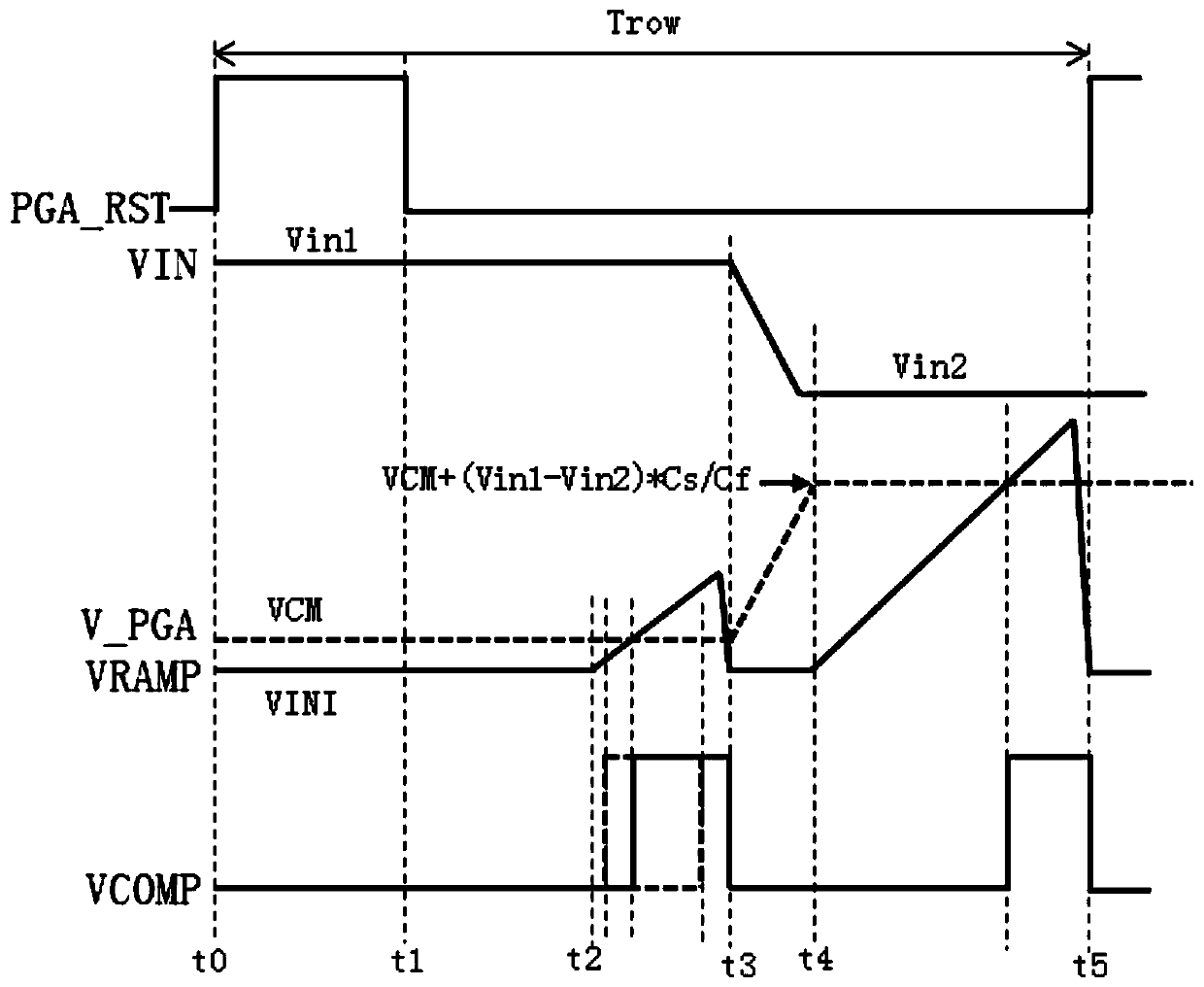

[0038] An embodiment of the present invention provides a readout circuit structure, refer to Figure 5 , Figure 5 It is a schematic diagram of the structure of a readout circuit with an offset cancellation function according to an embodiment of the present invention, from Figure 5 It can be seen that the readout circuit structure includes: a programmable gain amplifier circuit PGA and an analog-to-digital converter circuit ADC provided by phase coupling, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More