multi-die FPGA for realizing clock tree by using active silicon connection layer

A connection layer, multi-die technology, used in CAD circuit design, special data processing applications, climate sustainability, etc., can solve problems such as large structural limitations, asynchronous clocks, single signal interconnection, etc. Design Convergence, Improved Performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The specific embodiments of the present invention will be further described below with reference to the accompanying drawings.

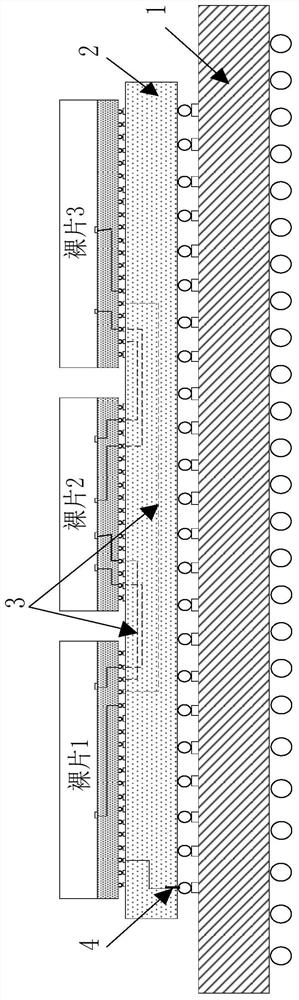

[0029] This application provides a multi-die FPGA that uses an active silicon connection layer to implement a clock tree. Please refer to figure 1 , the multi-die FPGA includes a substrate 1 , a silicon connection layer 2 and a number of FPGA die that are stacked at least sequentially from the bottom, which are respectively represented by die 1 , die 2 , etc., and so on. In actual implementation, the FPGA also includes an encapsulation shell that is packaged on the substrate 1, the silicon connection layer 2 and the outside of the FPGA die for protecting each component, and also includes pins connected to the substrate for signal extraction, etc., figure 1 These conventional structures are not shown in detail.

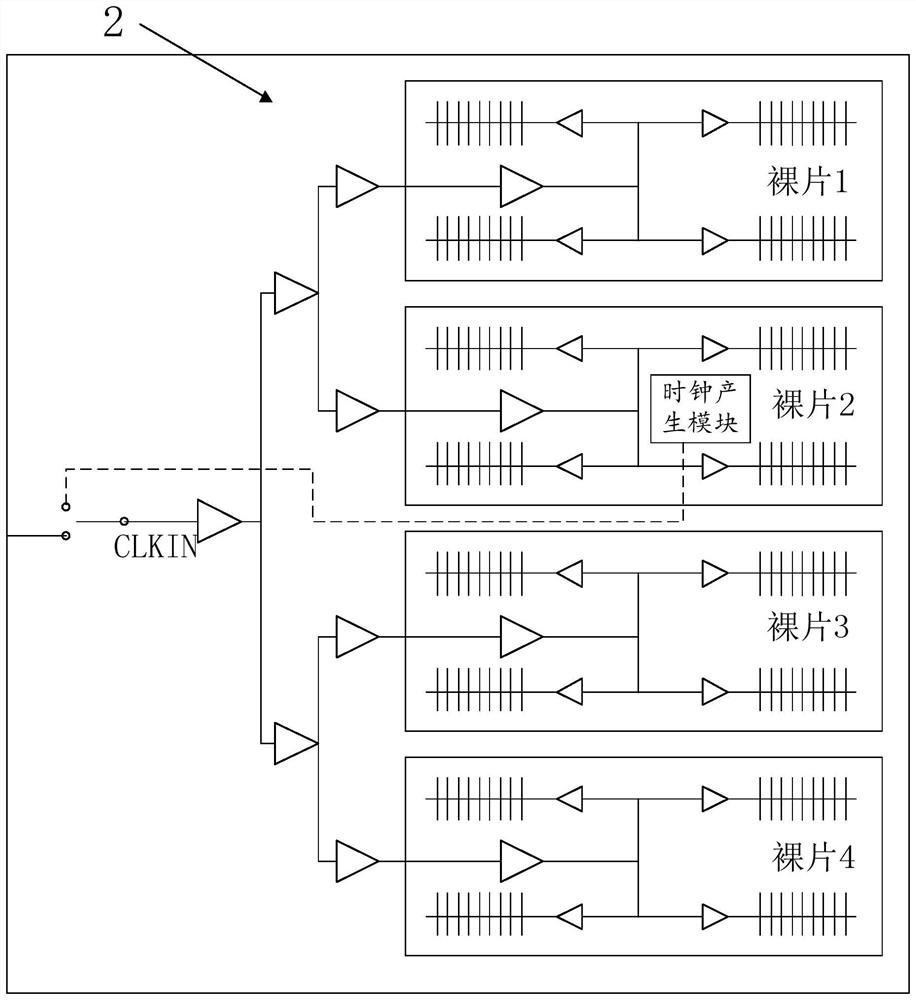

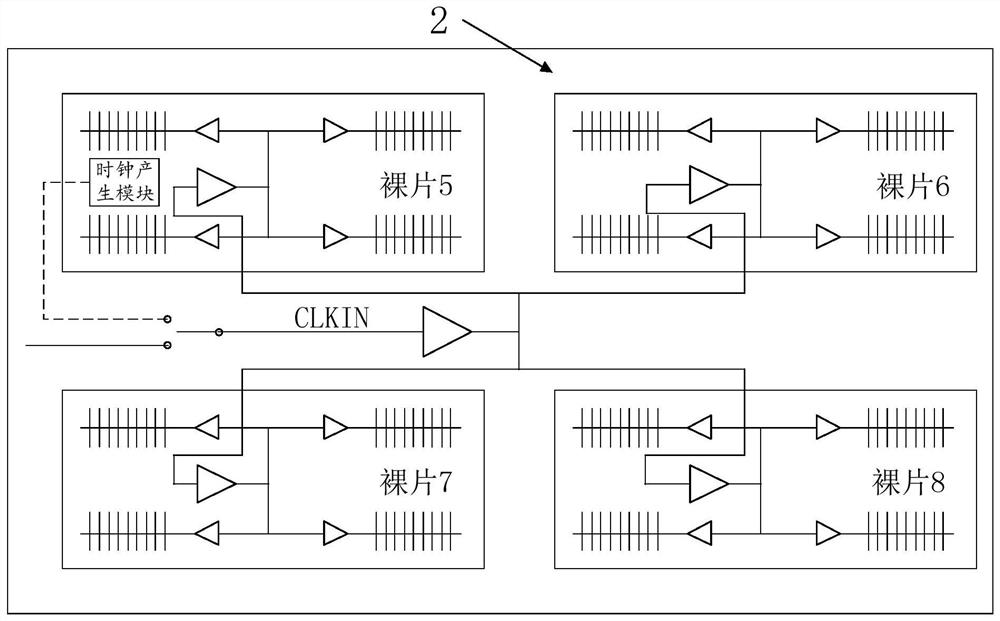

[0030] The FPGA of the present application does not use a single FPGA die structure, but includes multiple FPGA die, and the multipl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More