Integrated circuit static time sequence analysis method for GPU accelerated calculation

A static timing analysis, integrated circuit technology, applied in computing, computer-aided design, CAD circuit design, etc., can solve problems such as performance degradation, lack of coordination, GPU slowness, etc., to improve performance, reduce adverse effects, and reduce costs. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] Below in conjunction with accompanying drawing, through embodiment, further illustrate the present invention, but do not limit the scope of the present invention in any way.

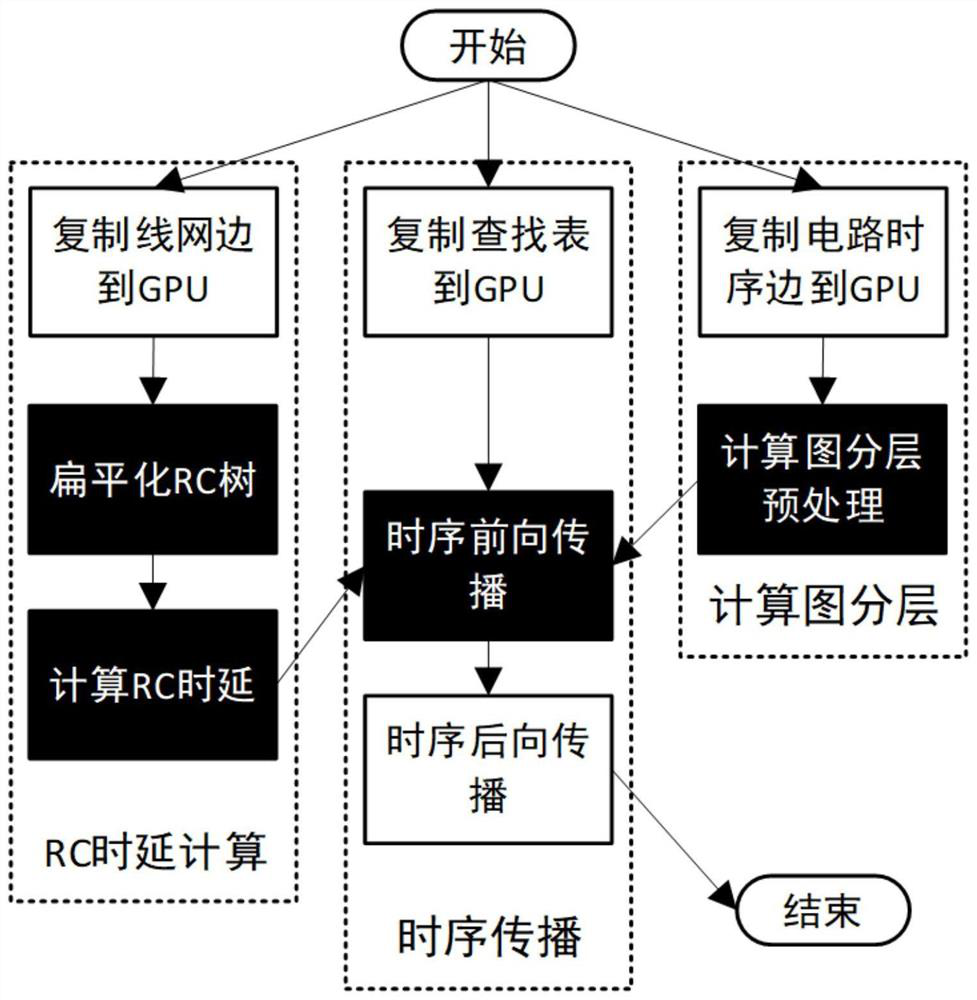

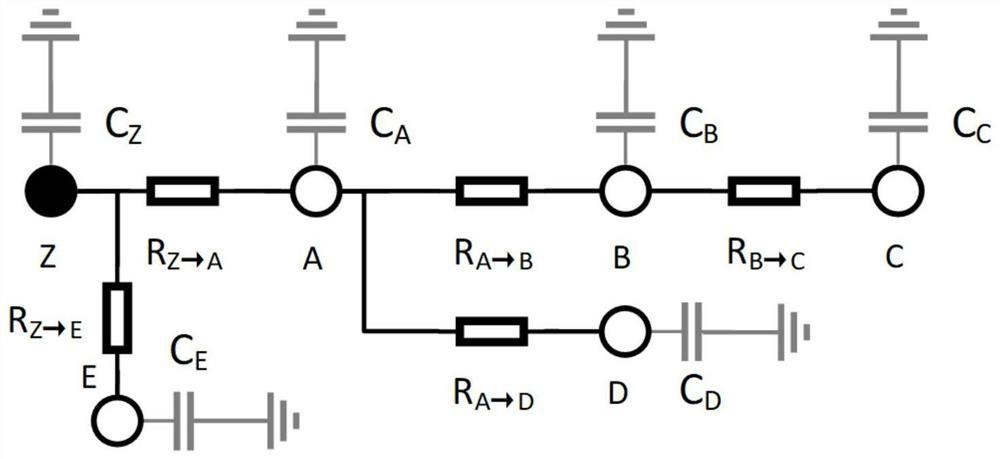

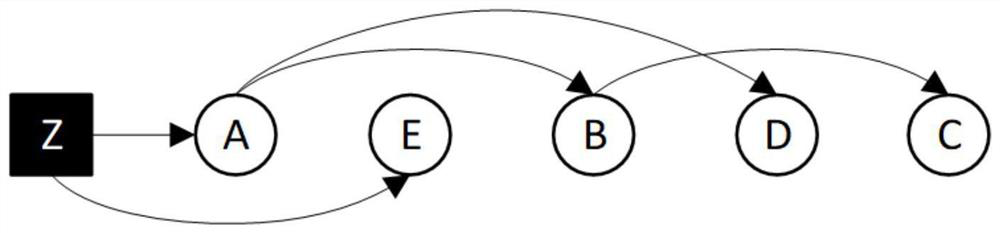

[0034] The present invention provides a method for static timing analysis of an integrated circuit for GPU accelerated calculation, which represents the input circuit information as a circuit structure diagram, flattens the circuit structure diagram, and expresses the edge relationship in the circuit structure diagram as a parent node pointer Or compress the form of adjacency list, and design the dynamic programming and topological sorting algorithm on the circuit structure diagram; design the GPU algorithm of all steps of the static timing analysis of the integrated circuit, and the GPU algorithm conforms to the "single instruction multi-threading" architecture, making CPU-GPU Time merging of computing tasks. By adopting the method of the invention, the cost of static timing analysis can be reduc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More