Forming method of semiconductor device

A semiconductor and device technology, applied in the field of semiconductor device formation, can solve the problems of poor fin topography uniformity, fin field effect transistor threshold voltage shift, affecting the performance stability of fin field effect transistors, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

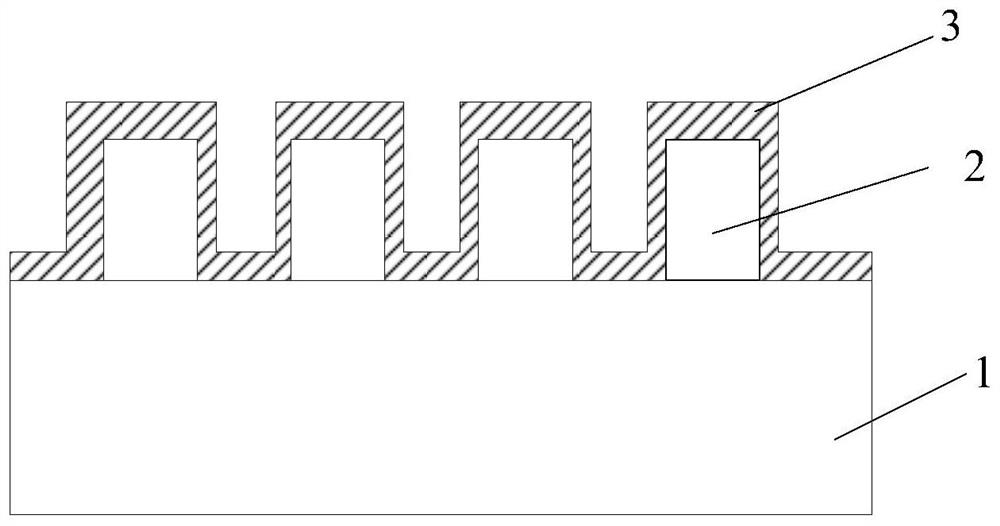

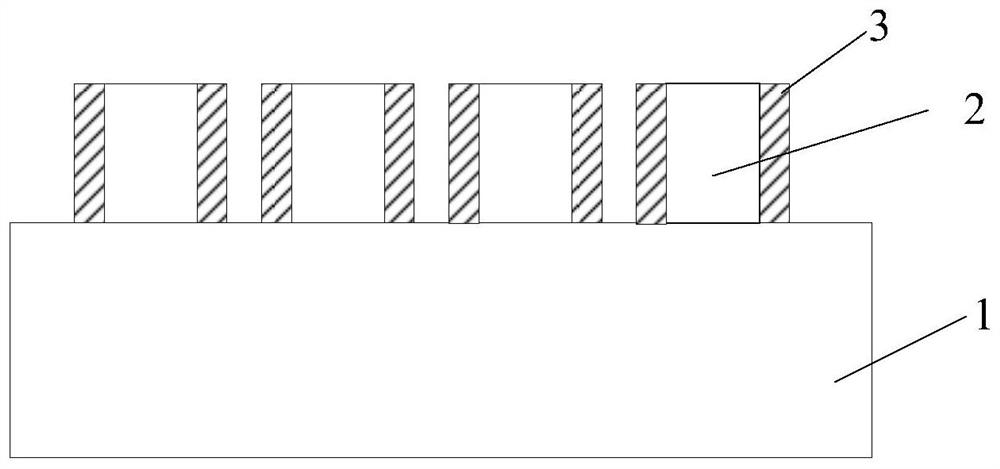

[0031] Figure 5 to Figure 11 It is a structural schematic diagram of the formation process of the semiconductor device in the first embodiment of the present invention.

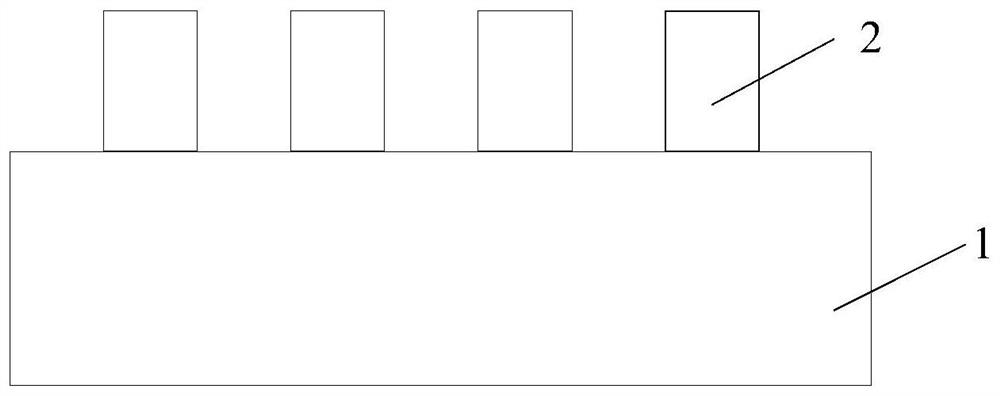

[0032] first reference Figure 5 , providing a substrate 100 on which core layers 200 are discretely arranged.

[0033] The substrate 100 may be monocrystalline silicon, polycrystalline silicon or amorphous silicon; the substrate 100 may also be semiconductor materials such as silicon, germanium, silicon germanium, gallium arsenide; in this embodiment, the substrate 100 The material is monocrystalline silicon.

[0034] In this embodiment, before forming the discretely arranged core layer 200 on the substrate 100, a protective layer 110 is formed on the substrate; in other embodiments, before forming the core layer, the The protection layer 110 is not formed on the substrate.

[0035] In this embodiment, the material of the protective layer 110 is silicon oxide; in other embodiments, the material of the p...

no. 2 example

[0074] Figure 12 to Figure 15 It is a structural schematic diagram of the formation process of the semiconductor device in the second embodiment of the present invention.

[0075] The difference between this embodiment and the first embodiment is that multiple oxidation and etching processes are used to process the sidewall layer until the substrate and the top of the core layer are exposed.

[0076] The number of times of the oxidation etching process is N times, 1≤N≤4, and N is a natural number greater than or equal to 1.

[0077] In this embodiment, N=2, that is, two oxidation etching processes are used to process the sidewall layer until the substrate and the top of the core layer are exposed; in other embodiments, three or four times can also be used. The oxidation etching process processes the sidewall layer to expose the substrate and the top of the core layer.

[0078] The process from providing the substrate to forming the side wall layer is the same as that of the f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More