Nanosheet transistor with heterogeneous gate medium and preparation method

A technology of nanosheets and heterogeneous gates, which is applied in the field of nanosheet transistors and its preparation, can solve the problems of increasing static power consumption of devices, achieve the effects of reducing short channel effects, reducing off-state current leakage, and improving channel mobility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be described in further detail below in conjunction with specific examples, but the embodiments of the present invention are not limited thereto.

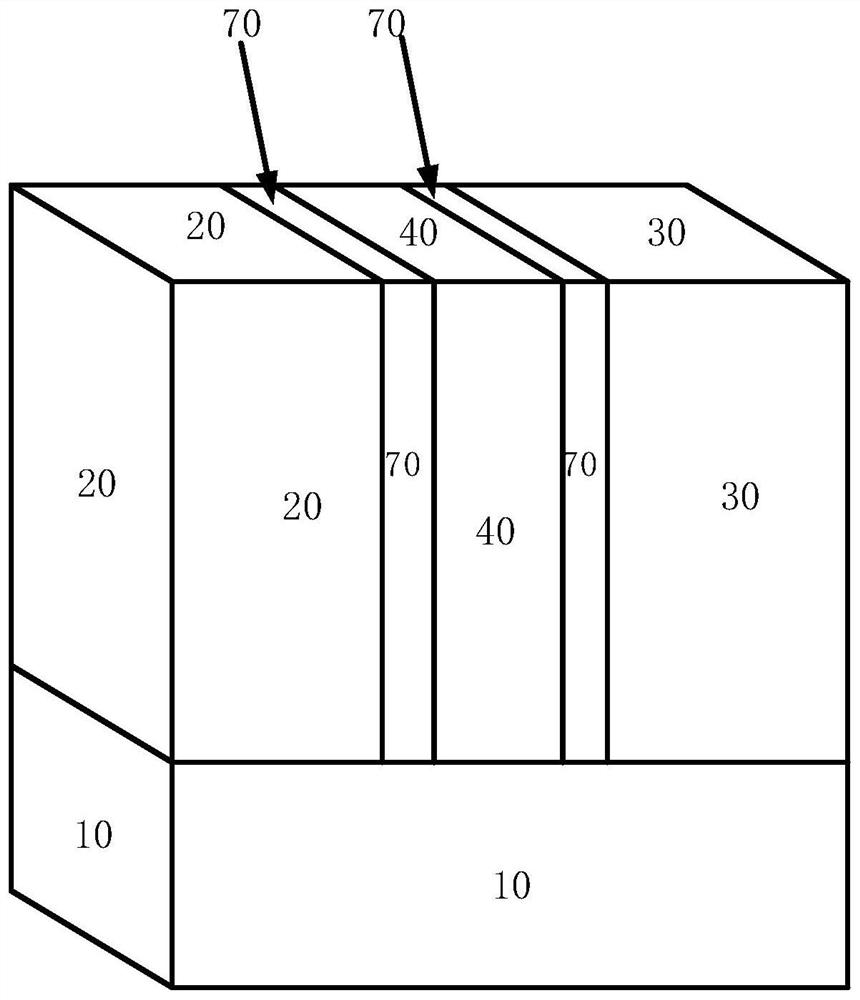

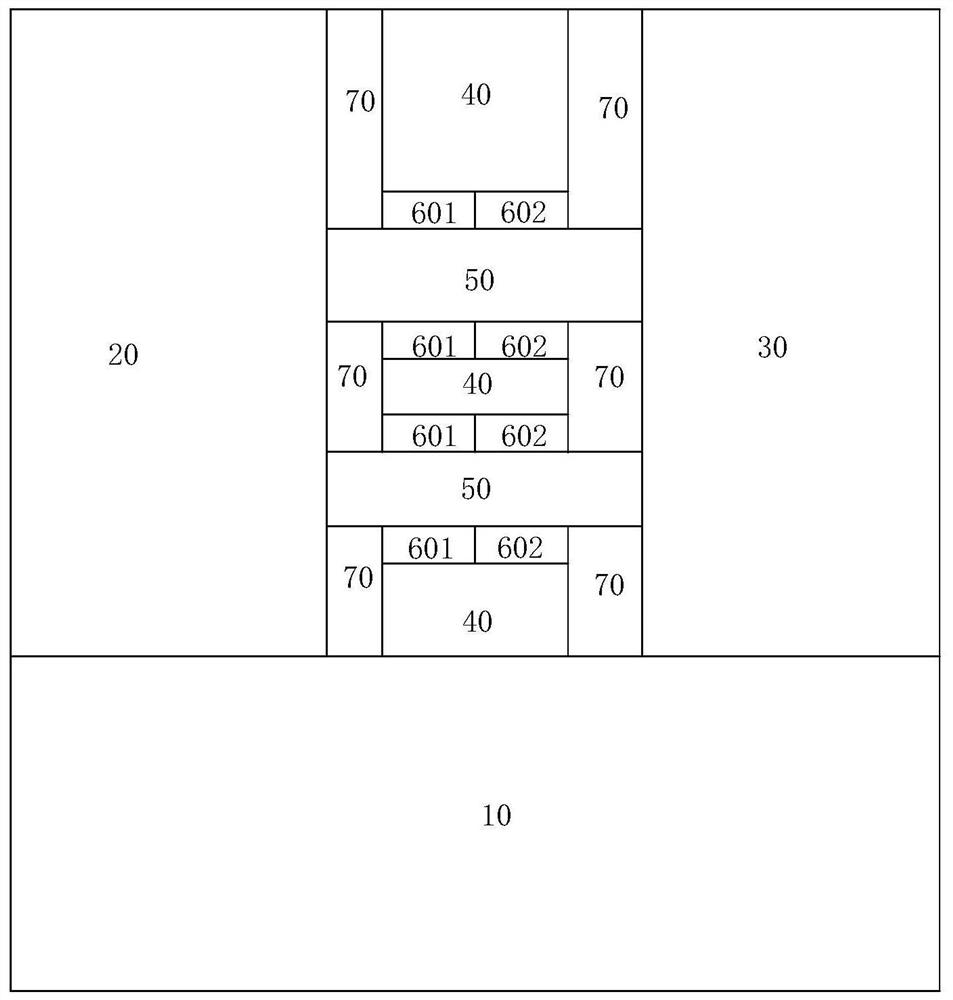

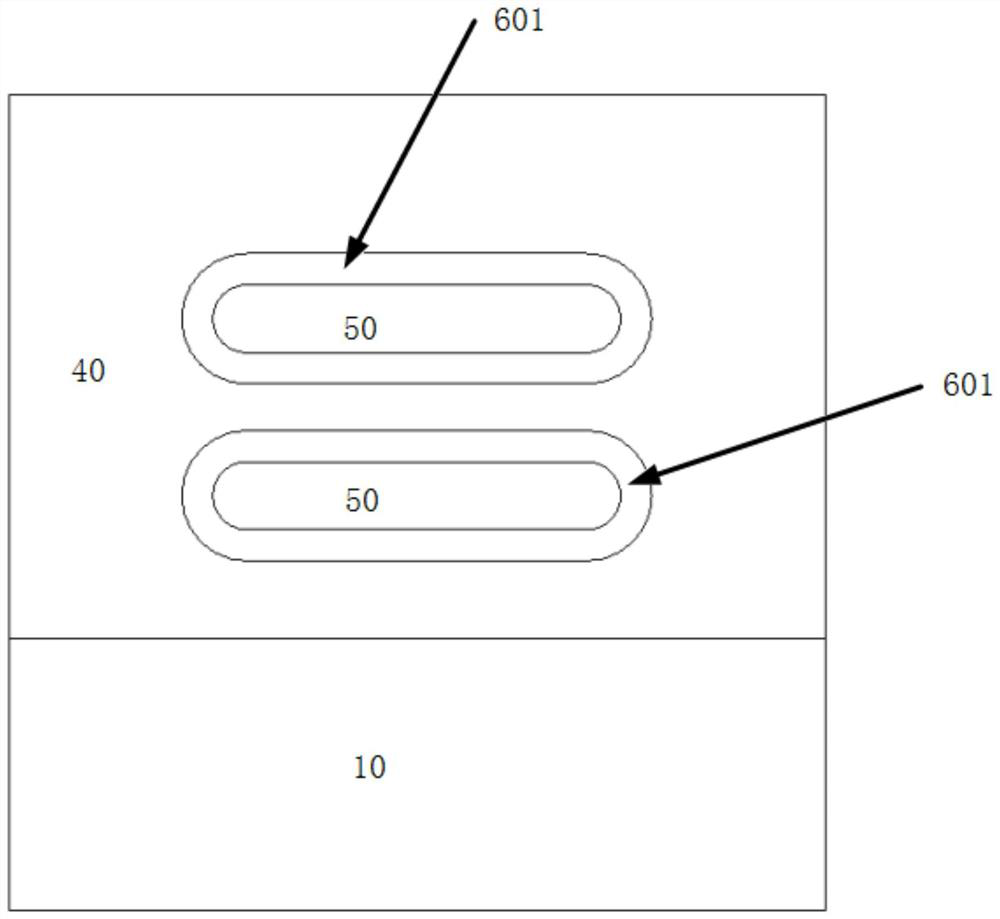

[0044] In order to reduce the short channel effect and off-state current leakage of small-sized field effect transistors and improve the electrical performance of small-sized field effect transistors, embodiments of the present invention provide a nanosheet transistor with a heterogeneous gate dielectric and a preparation method. Firstly, the nanosheet transistor with heterogeneous gate dielectric provided by the embodiment of the present invention will be described in detail. see figure 1 and figure 2 As shown, the nanosheet transistor includes: a substrate 10, a source region 20, a drain region 30, a gate material 40, and a plurality of nanosheet channel layers 50 arranged in parallel; figure 1 is the three-dimensional structure diagram of the nanosheet transistor, figure 2 is a cross-sectio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More