SiP module based on silicon switching four-layer three-dimensional stacking and manufacturing method

A manufacturing method and switching technology, applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of bare chips without considering chip stacking, lack of versatility, and inability to meet the application requirements of SiP products, etc. Achieving the effect of reduced area, good flexibility, and low overall cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0053] The first step: system design and simulation:

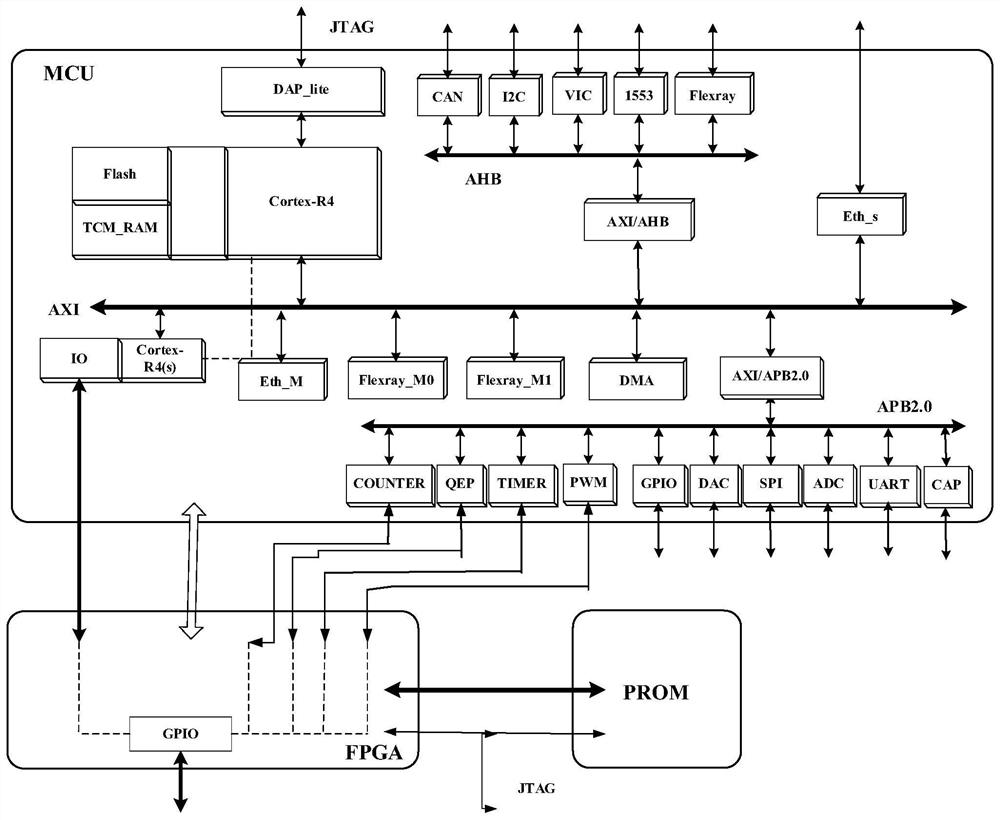

[0054] Phase 1: According to the system block diagram ( figure 1 ) to carry out the principle design of the SiP module, integrate the MCU, FPGA and PROM of the ARM core into the SiP, and form an embedded minimum system based on MCU+FPGA. The hardware implementation can be divided into two parts, namely MCU part and FPGA and configurable IO part. MCU implements system control, data calculation and peripheral interface control, FPGA implements logic decoding, IO and other function expansion;

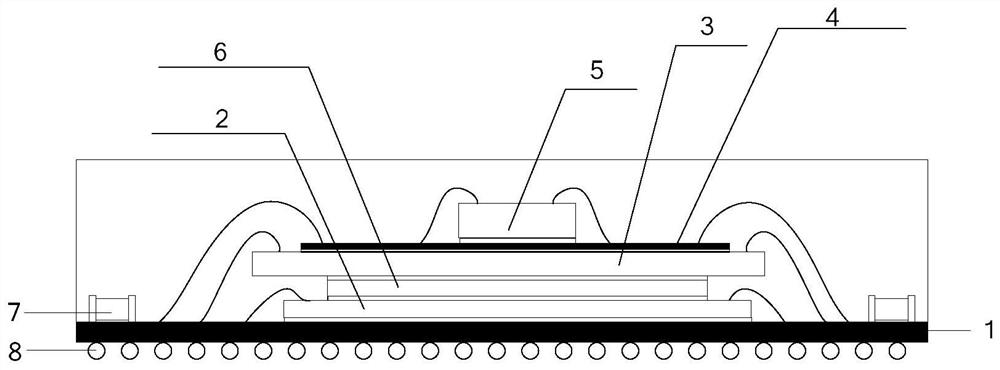

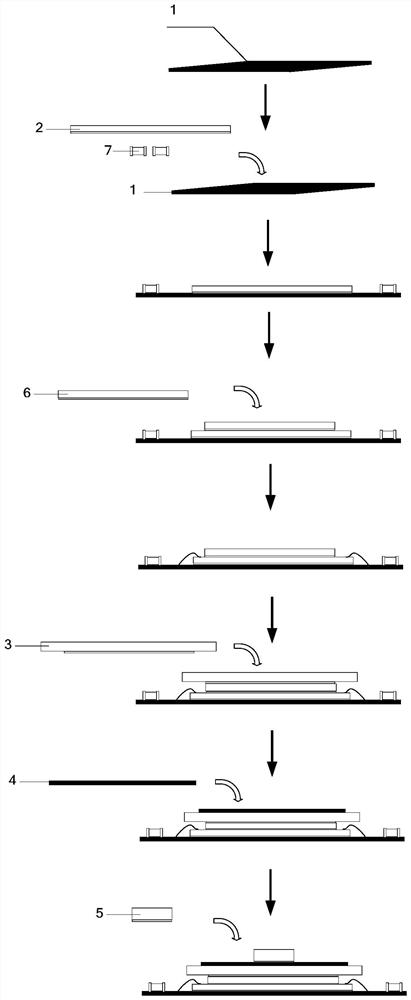

[0055] Phase 2: Carry out the process design of the SiP module, propose a feasible process and packaging scheme, and complete the design of the organic substrate and silicon interposer substrate. The module adopts the packaging process based on the organic substrate, and the multi-chip layout is carried out on the surface of the substrate, and the MCU, FPGA, silicon transfer substrate and PROM are stacked in four layers: bottom, midd...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Plate thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More