Power device single particle burnout resistant reinforced structure and preparation method thereof

A technology for power devices and anti-single events, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc. Reduce and other problems, achieve the effect of improving anti-SEB performance, improving anti-SEB performance, and reducing transient current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the purpose, technical solution and advantages of the present invention clearer, the present invention will be described in detail below in conjunction with the accompanying drawings.

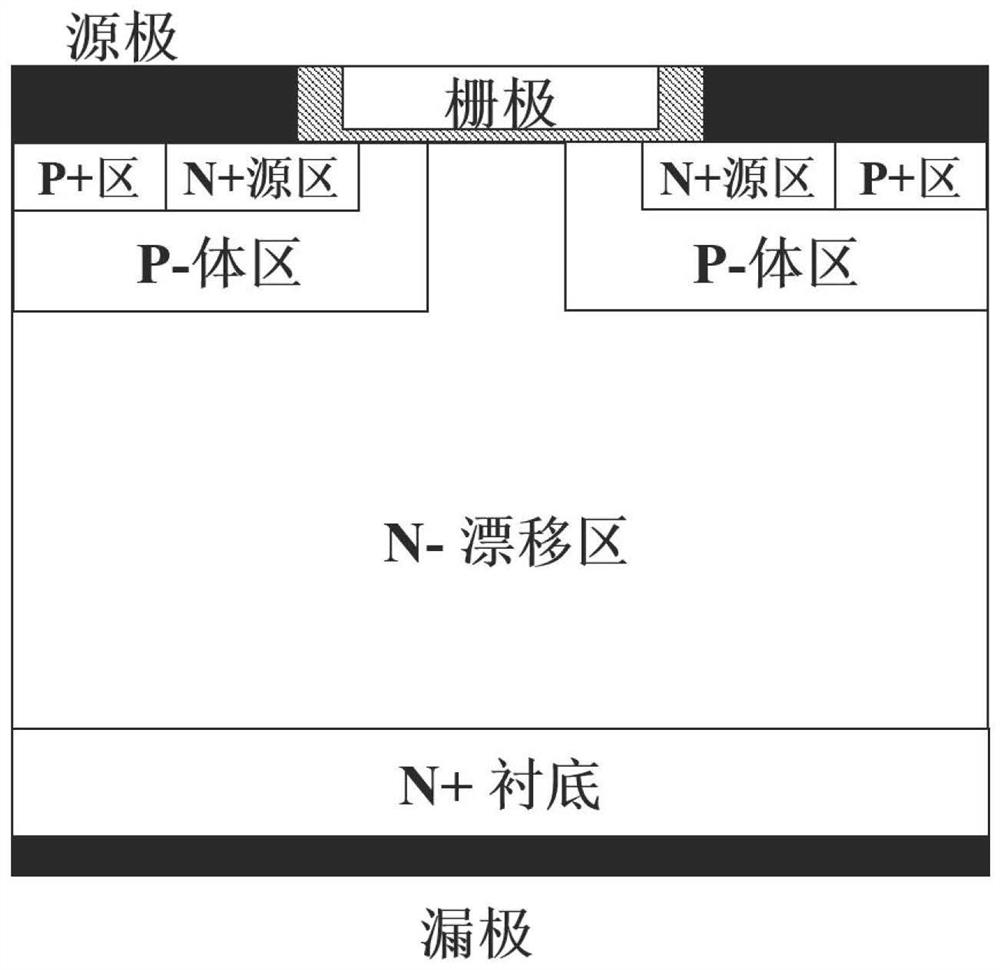

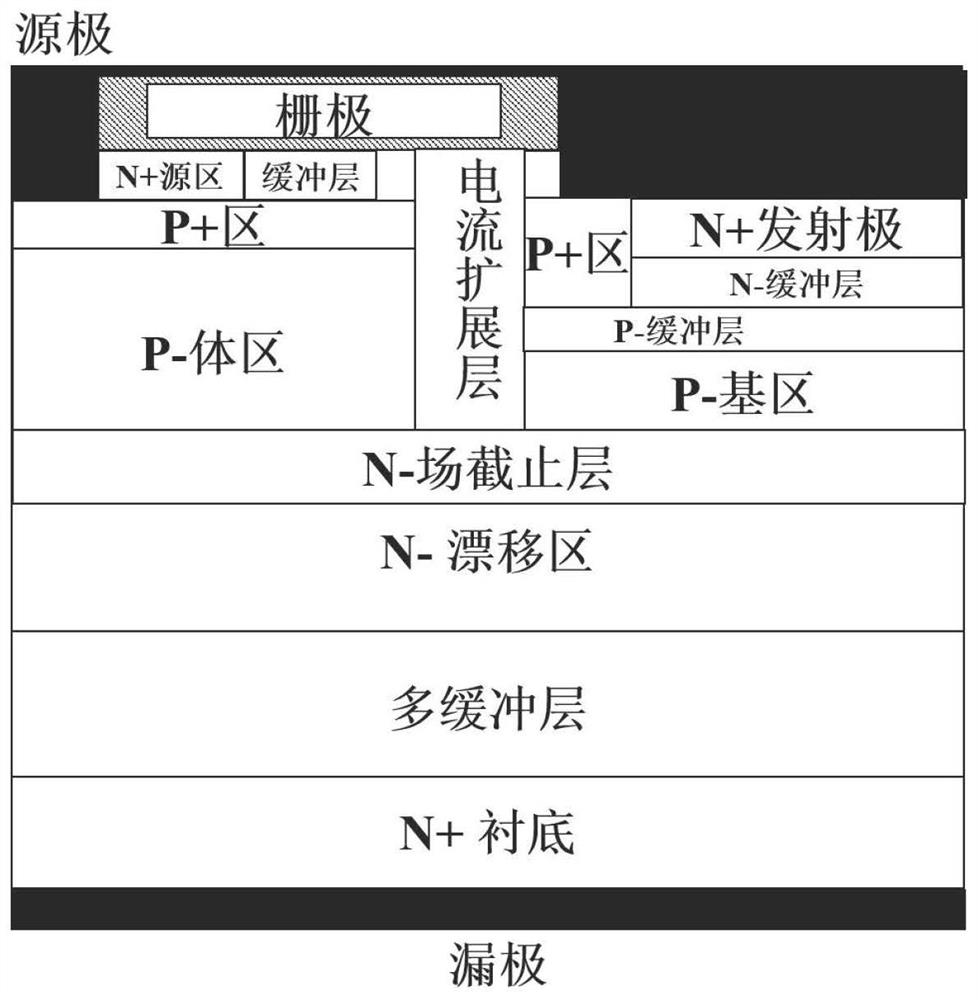

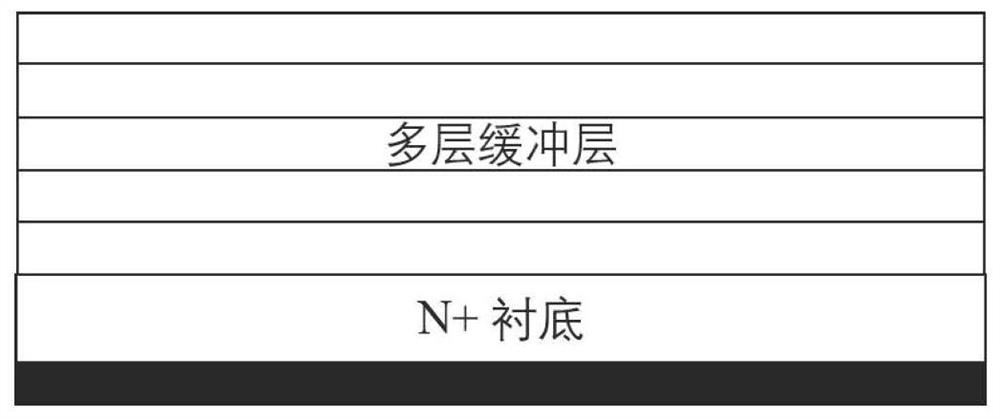

[0031] Such as figure 1 , 2 As shown, the present invention provides a power device anti-single event burning reinforcement structure, which is suitable for planar gate power VDMOSFET devices, figure 2 and figure 1 the difference lies in figure 2 The structure introduces an N-type multi-buffer layer, an N-type field stop layer and an integrated transistor structure under the neck electrode. Specifically, an N-type multi-buffer layer structure is set in the drain (cathode) electrode region of the semiconductor power device; a 0.5 μm groove is formed at the source (positive) electrode and the neck region electrode and a metal electrode is formed; the neck region An integrated transistor is arranged below the P-type body region and an N-type field stop layer is arrang...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| depth | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More