Hierarchical protection circuit for internal data of SoC

A technology for internal data and protection circuits, applied in the protection of internal/peripheral computer components, etc., can solve the problems of increasing SoC design complexity and design difficulties, and achieve the effect of low resource occupation and simple circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

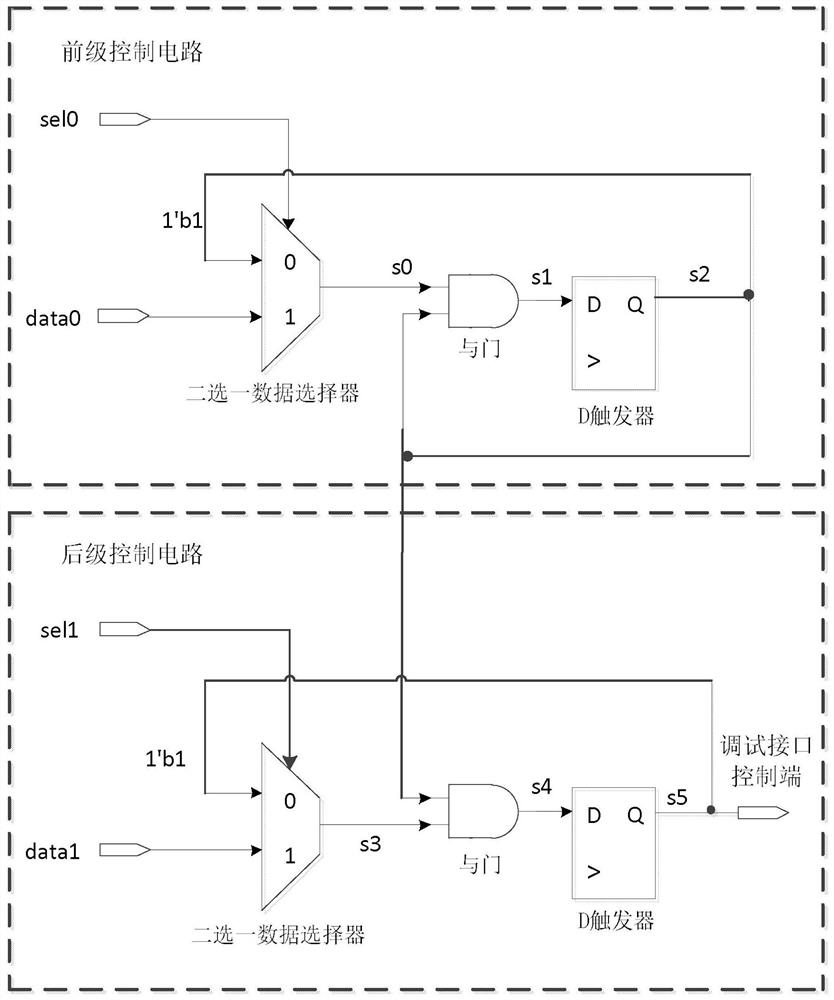

[0011] refer to figure 1 . In the preferred embodiment described below, based on the ARMv7 debugging architecture, a SoC chip internal data classification protection circuit includes a subsequent control circuit and a previous control circuit. The front-stage control circuit uses the input control signal and selection signal to generate an on-off signal, and the on-off signal directly acts on the rear-stage control circuit to control the output and on-off of the latter-stage circuit, and the on-off of the debugging interface of the latter-stage circuit; The front-stage D flip-flop of the control circuit is connected to the input end of the front-stage data selector (MUX) through the feedback line of the control terminal of the debugging interface. , output the value of the selected output result to the front-stage AND gate circuit VHD through the data output terminal, and add it to the previous-stage AND gate output terminal s1, turn on the D-side of the previous-stage D flip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More