FD-SOI back deep channel isolation process based on bonding process

A technology of FD-SOI and bonding process, which is applied to semiconductor devices, electrical components, circuits, etc., and can solve the problems of large chip area and high cost of FDSOI transistors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

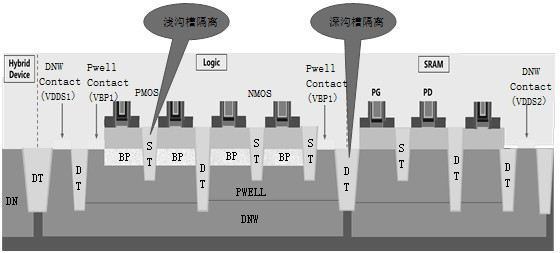

[0038] The present invention is described in further detail now in conjunction with accompanying drawing. These drawings are all simplified schematic diagrams, which only illustrate the basic structure of the present invention in a schematic manner, so they only show the configurations related to the present invention.

[0039] Such as Figure 4 As shown, a bonding process-based FD-SOI rear deep trench isolation process includes the following steps:

[0040] S1: Make the first chip 101 on the first wafer 100, make M first bonding Pad103 on the metal wiring layer 102 of the uppermost layer of the first chip 101, M is a positive integer, and the tungsten on the first chip 101 Make contact Pad104 in the through hole layer;

[0041] The schematic diagram of the structure after the first chip 101, the first bonded Pad103 and the contact Pad104 are fabricated on the first wafer 100 can be referred to Figure 5 , Figure 5 The second chip 101, the first bonding Pad103 and the con...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More