FPGA (Field Programmable Gate Array) virtualization hardware system stack design for cloud deep learning reasoning

A virtualization and cloud technology, applied in CAD circuit design, neural learning method, design optimization/simulation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] Embodiments of the present application are described in detail below, and examples of the embodiments are shown in the drawings, wherein the same or similar reference numerals denote the same or similar elements or elements having the same or similar functions throughout. The embodiments described below by referring to the figures are exemplary, and are intended to explain the present application, and should not be construed as limiting the present application.

[0046] The following describes an FPGA virtualization hardware system stack design for cloud-based deep learning inference with reference to the accompanying drawings.

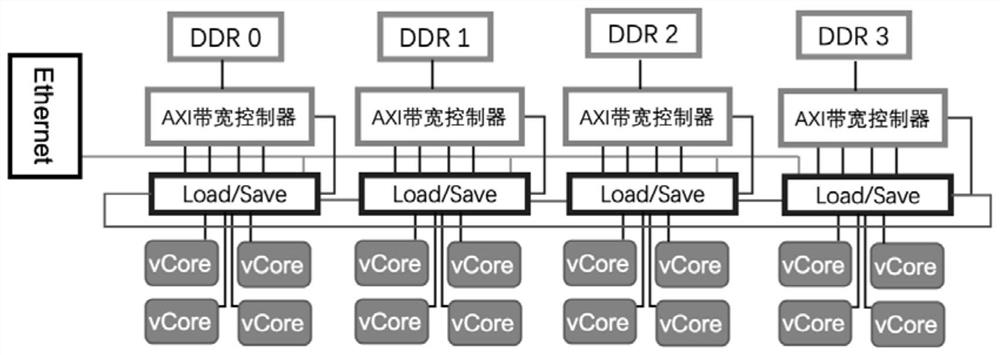

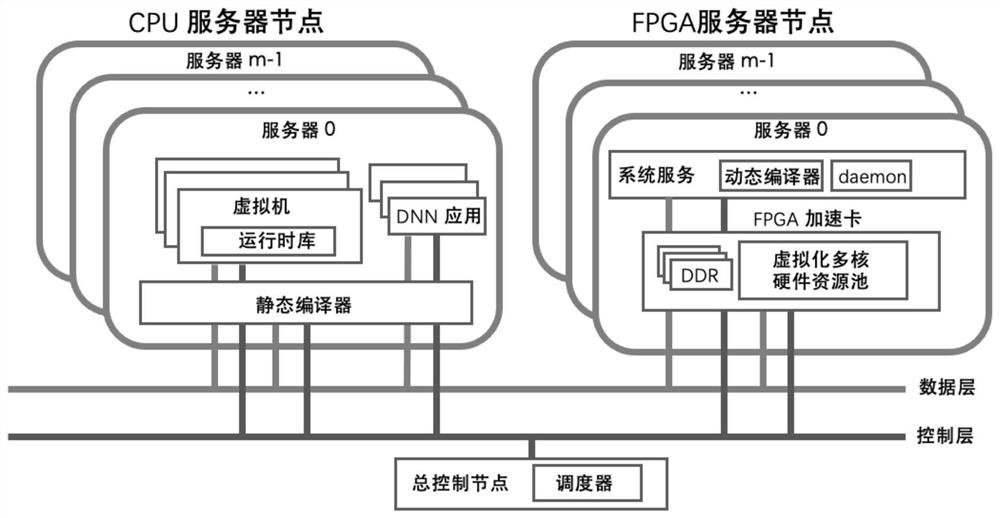

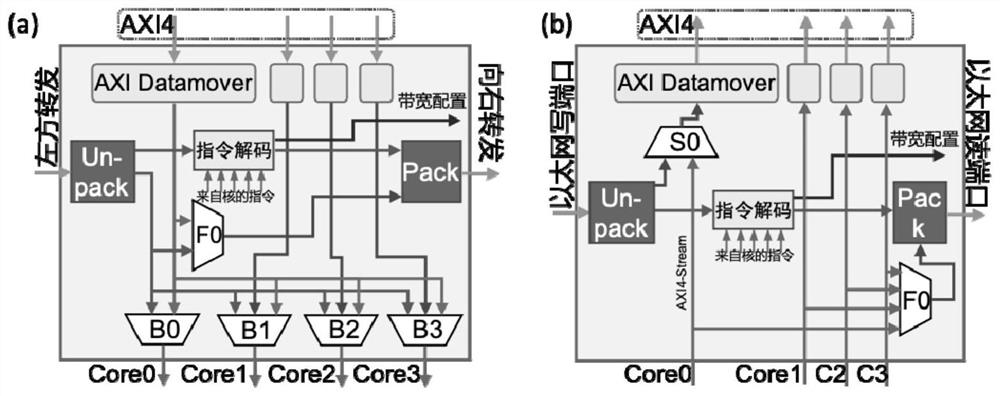

[0047] figure 1 The hardware architecture implementation of the ISA-based DNN accelerator virtualization provided by the embodiment of the present invention.

[0048] For this problem, as figure 1 As shown, the embodiment of the first aspect of the present application provides a distributed FPGA hardware-assisted virtualization hardware archi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com