SGT-MOSFET and manufacturing method thereof

A manufacturing method and deposition technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of height difference, increase the complexity of contact hole etching process, and affect the accuracy of contact hole exposure, etc., to achieve Eliminate the effect of height difference

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0058] In order to make the object, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the examples. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0059] Aiming at the problems existing in the prior art, the present invention provides a SGT-MOSFET and a manufacturing method thereof. The present invention will be described in detail below with reference to the accompanying drawings.

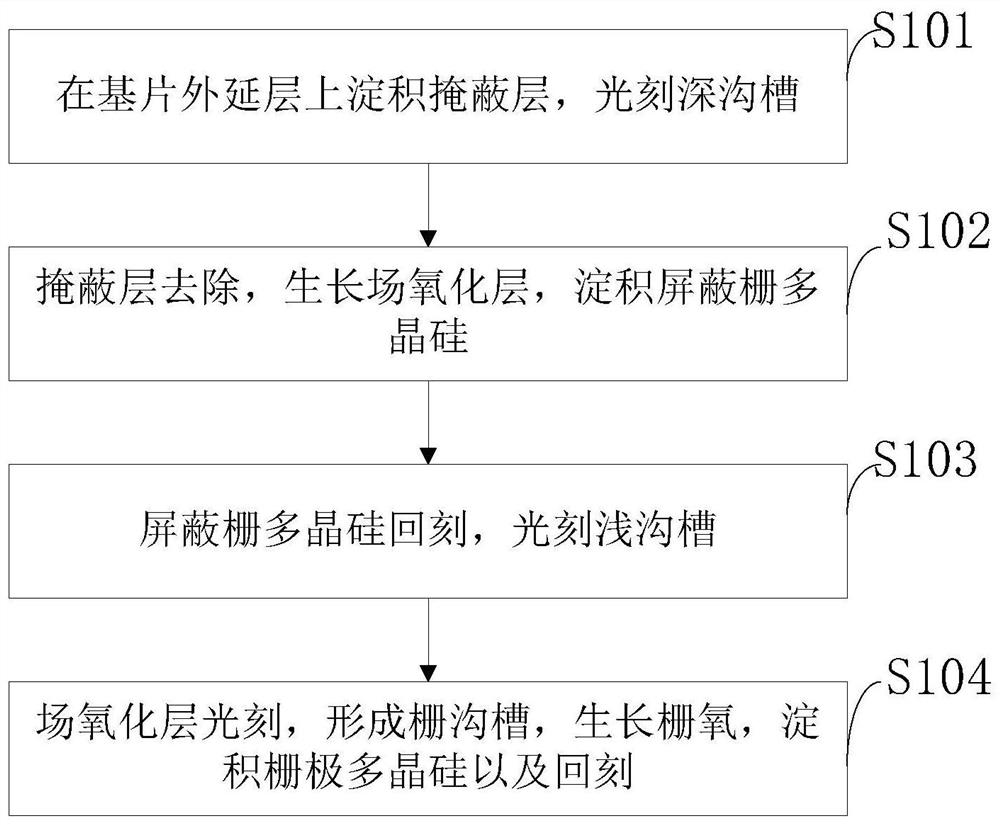

[0060] Those of ordinary skill in the industry of the manufacturing method of SGT-MOSFET provided by the present invention can also adopt other steps to implement, figure 1 The manufacturing method of the SGT-MOSFET provided by the present invention is only a specific embodiment.

[0061] Such as figure 1 As shown, the manufacturing method of the SGT-MOSFET provided by the embodiment of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More