Preparation method of heterojunction battery

A heterojunction cell and impurity technology, applied in circuits, photovoltaic power generation, electrical components, etc., can solve the problems of heterojunction cell photoelectric conversion efficiency distribution trailing, high cost, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

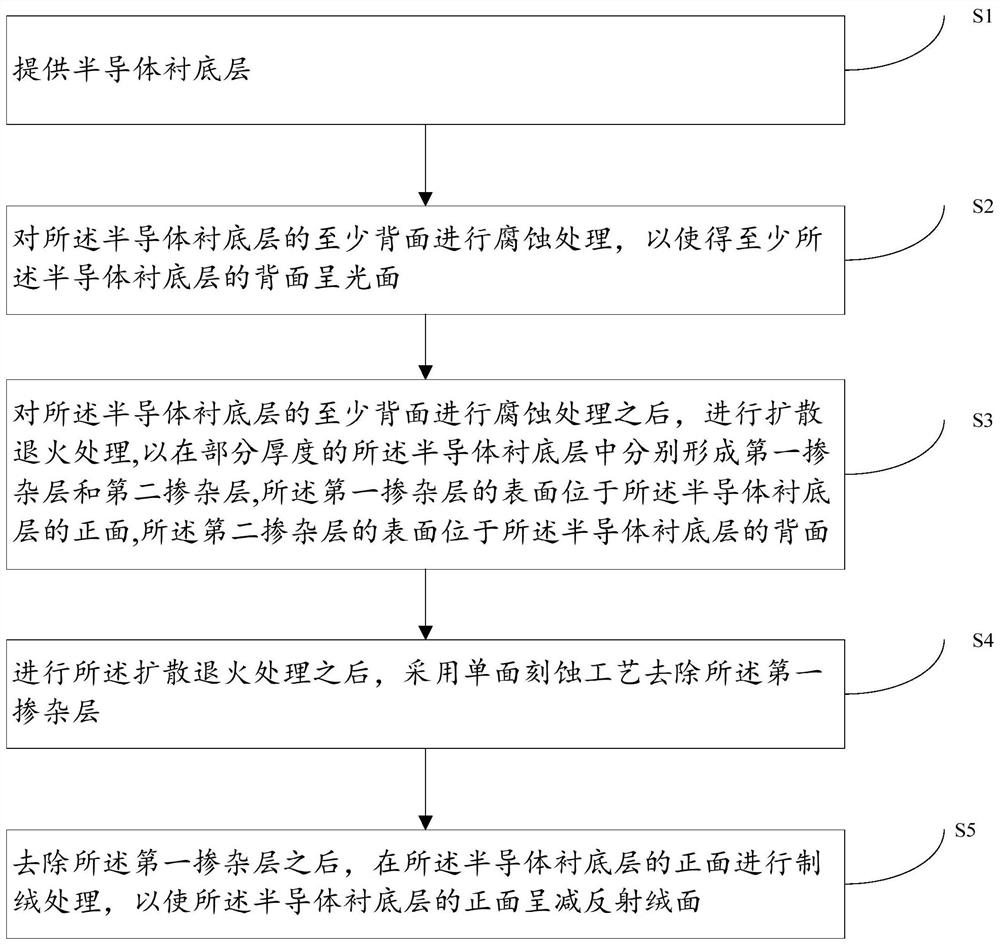

[0046] The embodiment of the present invention provides a preparation method of a heterojunction battery, please refer to figure 1 , including the following steps:

[0047] S1: providing a semiconductor substrate layer;

[0048] S2: performing etching treatment on at least the back side of the semiconductor substrate layer, so that at least the back side of the semiconductor substrate layer is a smooth surface;

[0049] S3: After performing etching treatment on at least the back side of the semiconductor substrate layer, perform diffusion annealing treatment to form a first doped layer and a second doped layer in a partial thickness of the semiconductor substrate layer, the first doped layer The surface of the doped layer is located on the front side of the semiconductor substrate layer, and the surface of the second doped layer is located on the back side of the semiconductor substrate layer;

[0050] S4: After performing the diffusion annealing treatment, remove the first ...

Embodiment 2

[0106] Another embodiment of the present invention also provides a method for preparing a heterojunction battery, which is combined below Figure 10 to Figure 11 Make a detailed introduction.

[0107] refer to Figure 10 , Figure 10 for Figure 7 Based on the schematic diagram, compared with Embodiment 1, this embodiment also removes the second doped layer 112 on the basis of removing the second oxide layer 132 .

[0108] In this embodiment, the second doped layer 112 is removed during the process of removing the second oxide layer 132 . Specifically, after the rounding process is performed, the second oxide layer 132 and the second doped layer 112 are removed.

[0109] The process of removing the second oxide layer 132 and the second doped layer 112 adopts a wet etching process. Specifically, the second oxide layer 132 and the second doped layer 112 are removed by chain cleaning. The method improves the efficiency of removing the second oxide layer 132 and the second do...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com