Method for improving VCSEL exposure uniformity and VCSEL chip

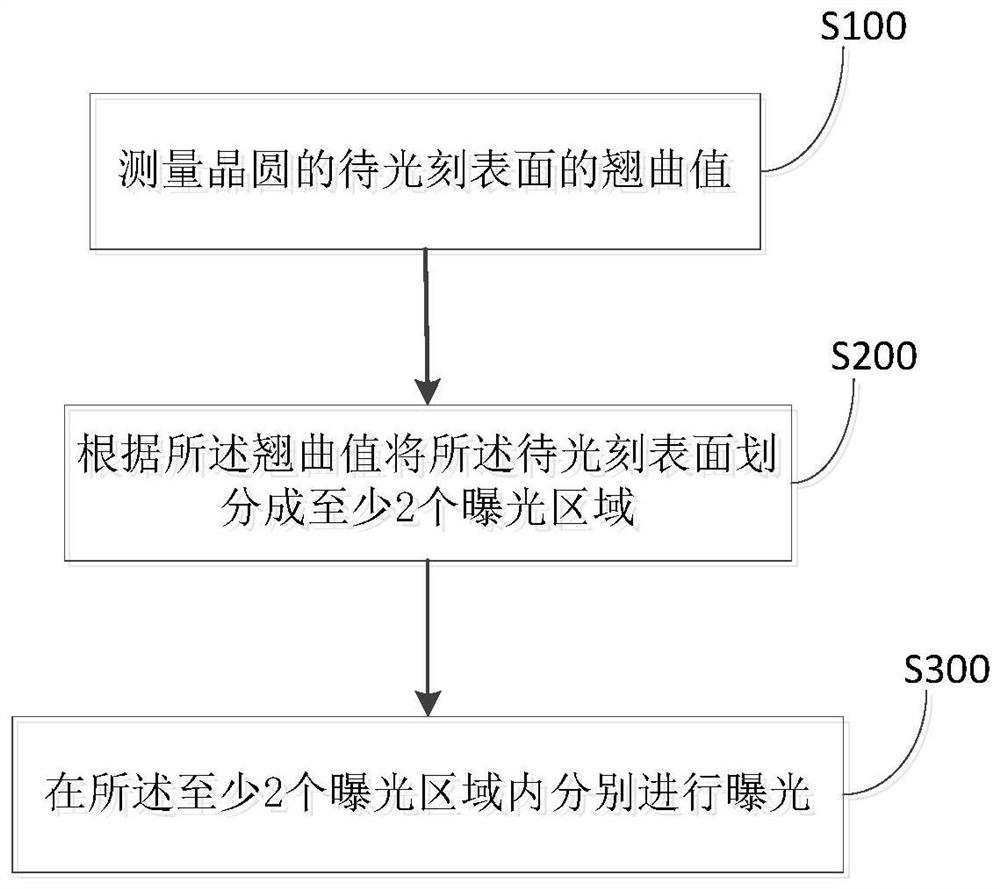

A technology of uniformity and exposure area, which is applied in a method of improving the uniformity of VCSEL exposure and in the field of VCSEL chips, which can solve the problems of affecting the exposure focus of the lithography process, affecting the resolution of graphics, and the inability of light to focus, so as to improve the quality of graphics , Improving exposure uniformity and improving yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0055] During the VCSEL manufacturing process, the wafer (with a thickness of 100mm) will show a certain amount of warpage after undergoing high-temperature processes such as metal process, oxidation process, etc. , the wafer warpage value test method is as follows:

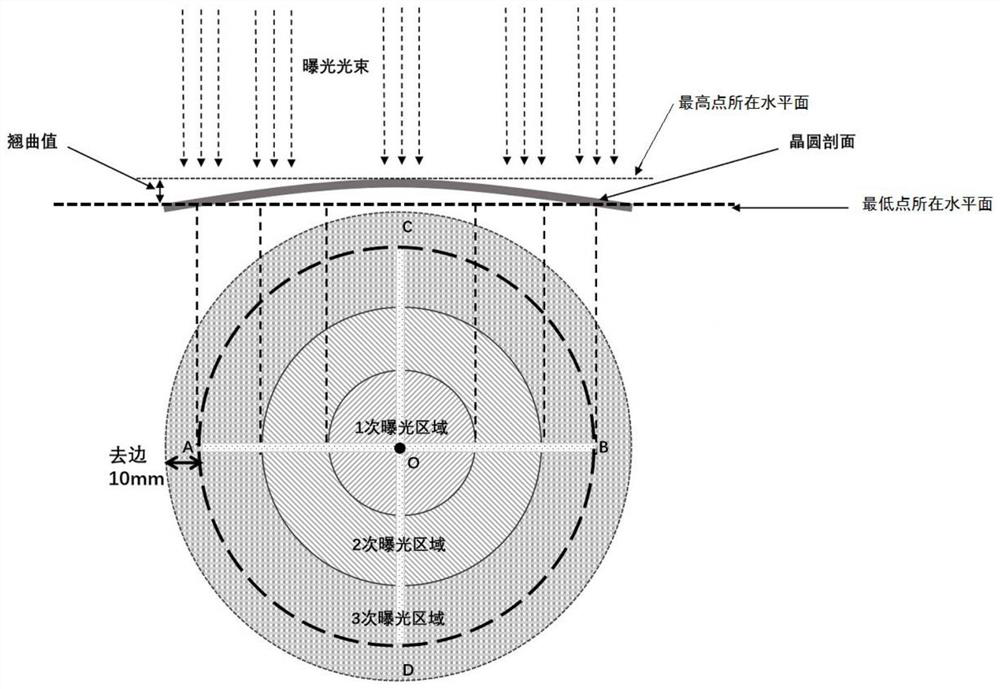

[0056] like figure 2 As shown, the horizontal axis AB and the vertical axis CD are vertically intersected through the point O of the wafer center. The horizontal axis intersects the outer edge of the wafer at points A and B, and the vertical axis intersects the outer edge of the wafer at points C and D. Since edge removal is performed during the actual chip process, points A, B, C, and D are each 10mm away from the edge.

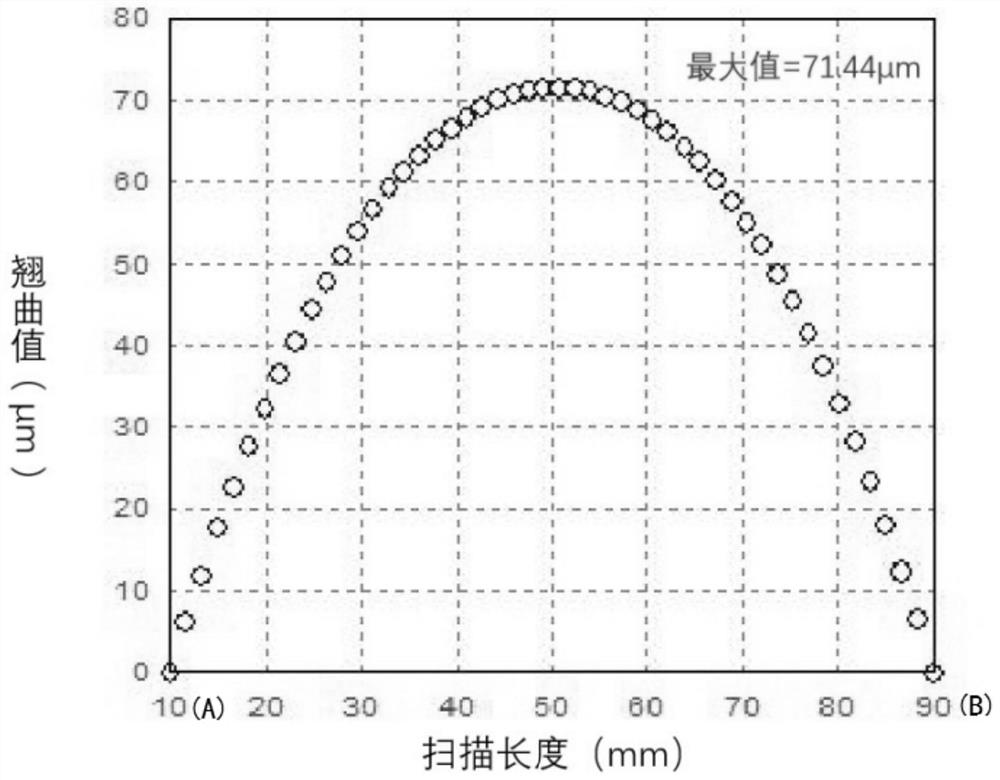

[0057] After the oxidation process is completed, use a film stress tester to scan the warpage value of the test wafer along the horizontal axis AB and the longitudinal axis CD respectively. The results of the AB line scan are shown in the attached image 3 As shown, the maximum warpage value...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More