Clock Synchronization Method for Switching Mode DC Converter

A DC converter, switching technology, applied in the direction of converting DC power input to DC power output, high-efficiency power electronic conversion, output power conversion device, etc. The filter capacitor occupies a large chip area, large chip area and power consumption, etc., to achieve the effect of saving power consumption and area, saving power consumption, and eliminating additional duty cycle errors.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by those of ordinary skill in the art without creative efforts shall fall within the protection scope of the present invention.

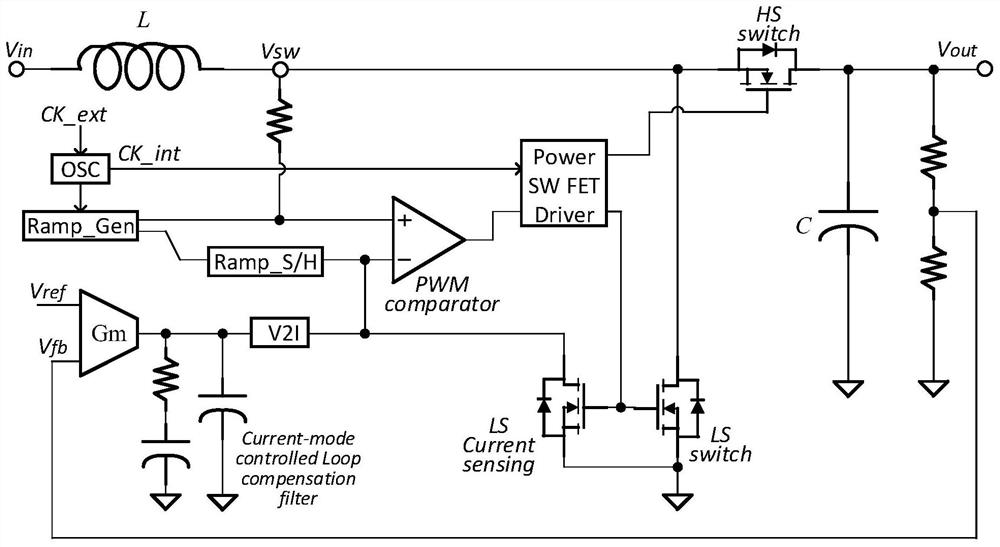

[0041] figure 1 Shown is a typical switching DC converter, a current-controlled mode DC boost converter (Boost). According to the magnitude of the load current, the DC converter works in two states: Pulse Width Modulation (PWM) or Pulse Frequency Modulation (PFM). If the input and output voltages of the Boost are respectively V in and V out , then the duty cycle of the gate drive voltage of the low-side switch in the PWM working state is:

[0042]

[0043] Therefore, according to the application when the minimum input voltage V in with the maximum output...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More