Substrate-free high-power amplitude limiter and preparation method thereof

A substrate-free, high-power technology, which is applied in the fields of diode amplitude limitation, semiconductor/solid-state device manufacturing, and electric solid-state devices, can solve problems such as difficulty in meeting the needs of high-power limiting applications and low thermal conductivity, and achieve improved Withstand power, effect of low series resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

[0028] A substrate-free high-power limiter and a preparation method thereof, comprising the following steps:

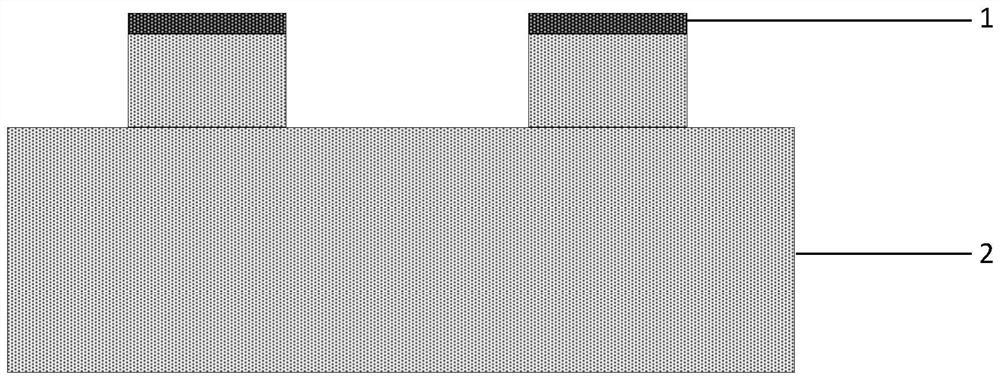

[0029] ① Prepare the PIN limiter tube front process on the surface of the PIN limiter diode 2 material, and etch to expose the P + , I and N + The mesa structure is used to prepare the metal upper electrode 1: wherein the PIN clipping diode material is one of Si and GaAs PIN, and the P + The mesa height of layer I is 0.5-3μm, the height of I-layer mesa is 1μm-20μm, N + The mesa height of the layer is 1-5 μm. The metal upper electrode material includes but not limited to one or a combination of Ti, Pt, Au, Pd, Ni, Al, and the preparation methods include but not limited to evaporation, electroplating, sputtering shoot, etc., such as figure 1 shown.

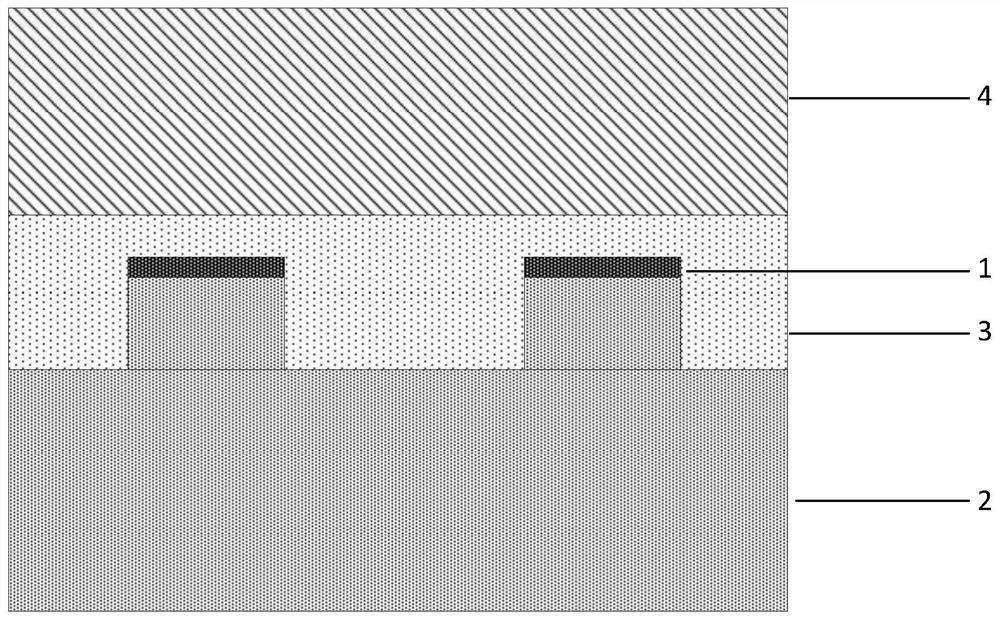

[0030] ② Spin-coat adhesive 3 on the front of the material containing the PIN diode mesa structure: the adhesive 3 is one of polymers such as photoresist, high-temperature wax or BCB, with a thickness of 5-50 μm, and th...

Embodiment

[0036] A substrate-free high-power limiter and a preparation method thereof, comprising the following steps:

[0037] ① Prepare P+, I and N+ mesa structures on Si PIN material wafers, where P + The mesa height of layer I is 1.5 μm, the mesa height of I layer is 8 μm, N + layer mesa height is 3µm, then the P + TiPtAu is evaporated on the layer mesa as the upper electrode metal.

[0038] ② Spin-coat high-temperature wax of about 15 μm on the front surface of the wafer with the PIN mesa structure, the spin-coating speed is 500 rpm, the spin-coating time is 60s, the pre-baking temperature is 155°C, and the time is 5 minutes.

[0039] ③The front side of the wafer containing the PIN mesa structure and the front side of the silicon carrier are relatively bonded together, and put into the chip bonder for temporary bonding. The bonding process parameters are temperature 180°C, bonding time 20 minutes, and bonding pressure 600MPa .

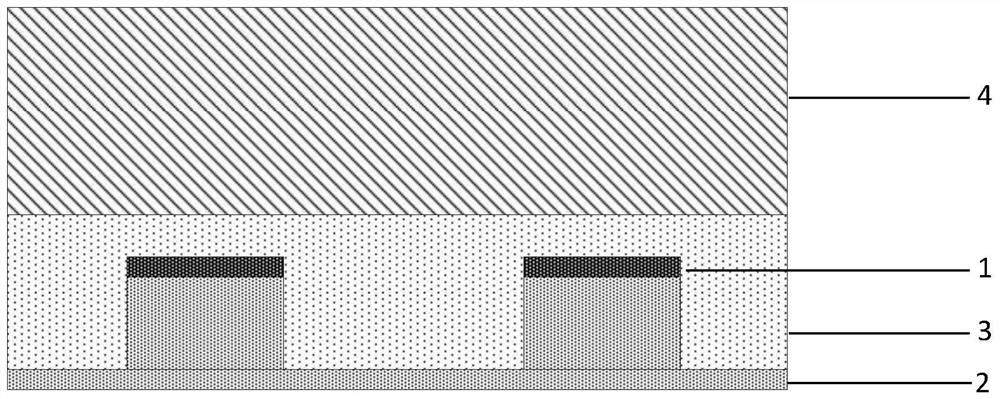

[0040] ④ The Si PIN wafer is ground and thinned...

PUM

| Property | Measurement | Unit |

|---|---|---|

| electrical resistivity | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More