Double-sampling single-refreshing method based on three-phase two-level topological structure

A topology, double sampling technology, applied in electrical components, output power conversion devices, AC power input conversion to AC power output and other directions, can solve problems such as system control impact, system stability impact, system stability margin impact, etc. , to achieve the effect of eliminating digital control delay, easy to implement, and avoid adverse effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The technical solutions of the present invention will be further described below in conjunction with the accompanying drawings and specific embodiments.

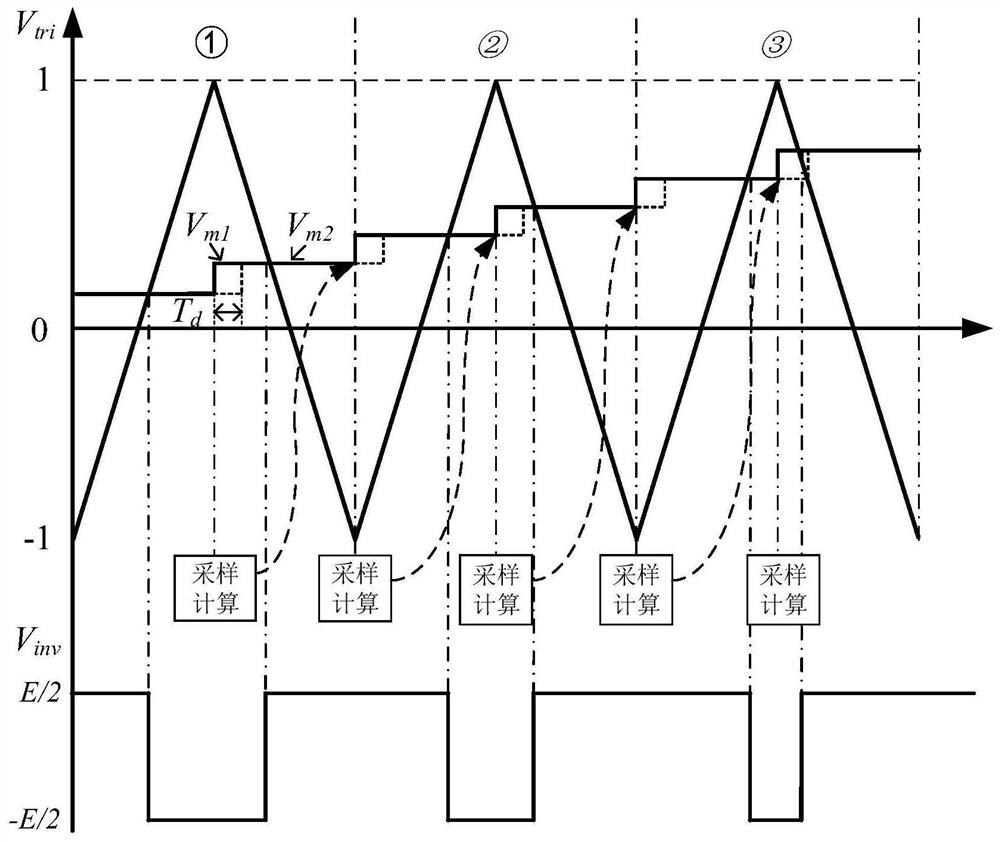

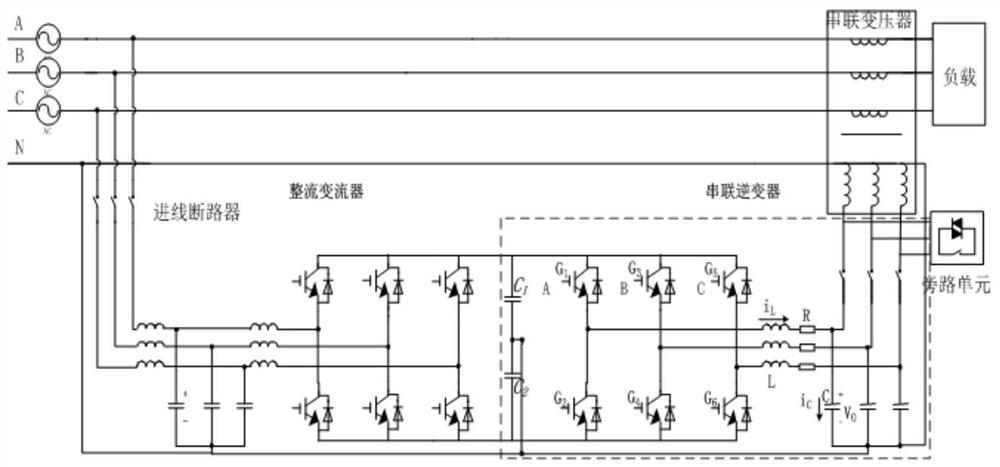

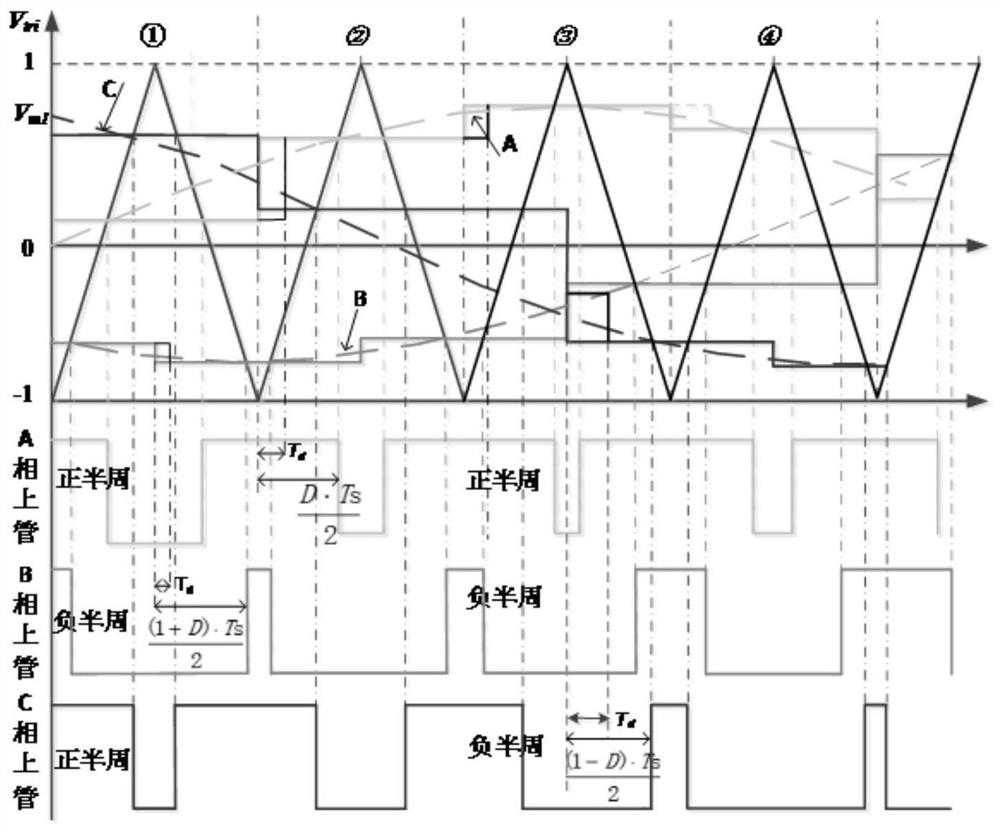

[0019] A double-sampling single-refresh method based on a three-phase two-level topology, see figure 2 As shown, the three-phase two-level topology structure includes a three-phase fully-controlled rectifier bridge, a DC bus capacitor, a three-phase fully-controlled inverter bridge, LCL filter circuits on the rectifier side and inverter side, and a series connection coupled with the grid voltage The transformer and the controller DSP generate modulation waves by calculating and processing the voltage and current signals collected by the actual system. After PWM modulation (that is, after the control loop outputs the modulation wave and compares it with the carrier), a PWM signal is generated to control the switch of the three-phase fully-controlled inverter bridge. state.

[0020] The controller DSP sampling voltage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More