TLB simulator based on SW processor chip architecture and debugging method

A simulator and processor technology, applied in special data processing applications, climate sustainability, energy-saving computing, etc., can solve the problem of accelerating the number of rework, reduce the number of rework, improve speed and quality, and verify high efficiency Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

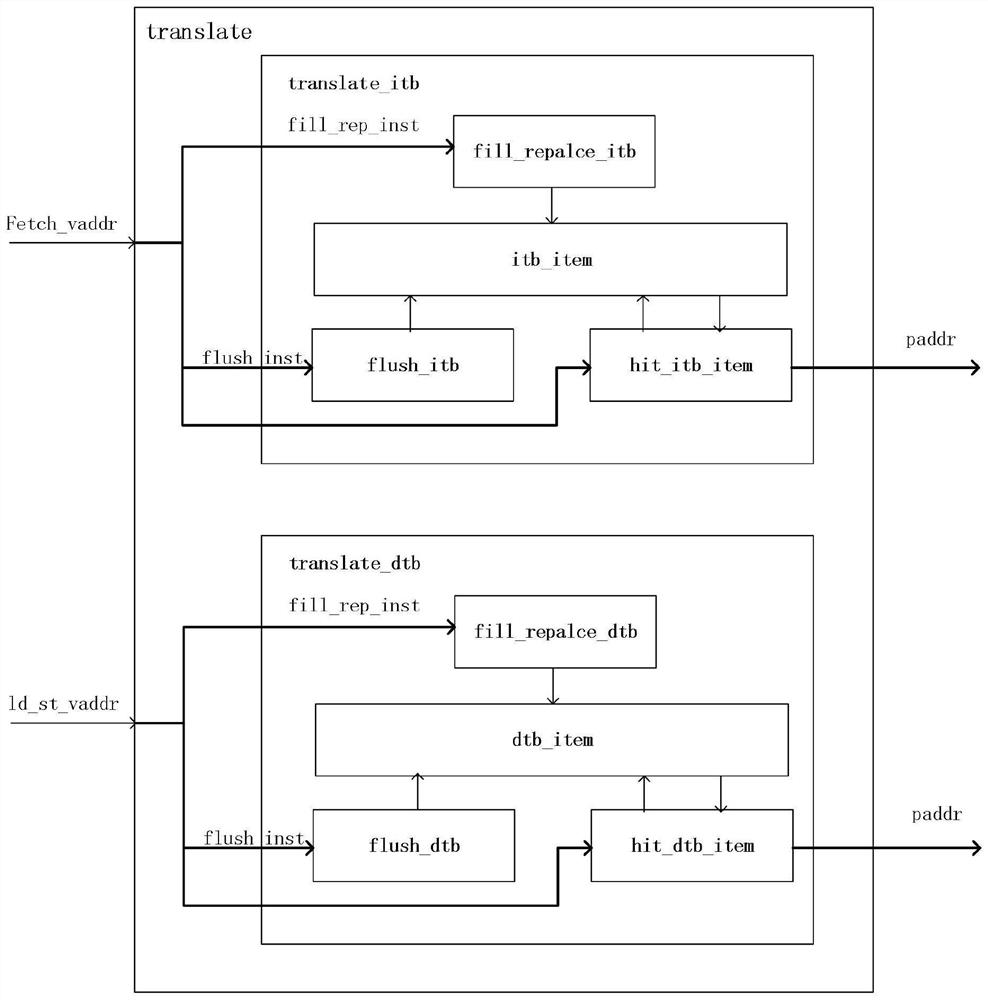

[0022] Such as figure 1 As shown, this embodiment provides a TLB simulator based on the Shenwei processor chip architecture. By using C++ language to perform functional modeling on the TLB module of the Shenwei high-performance processor chip, the correctness of its function is verified. The TLB simulator of Shenwei high-performance processor chip architecture includes:

[0023] The command / data virtual and real address conversion module receives the instruction fetch instruction / storage read instruction virtual address of the upper pipeline, and calls the instruction / data hit judgment module, instruction / data refresh module, and loading replacement module for instruction / data entries The storage module performs processing, and then outputs the substituted physical address;

[0024] The instruction / data hit judgment module judges whether the virtual address of the fetch instruction / storage read instruction hits the entry in the instruction / data entry storage module, and if it...

Embodiment 2

[0033] Such as figure 2 As shown, a debugging method of a TLB simulator based on the Shenwei processor chip architecture is built with the TLB simulator based on the Shenwei high-performance processor chip architecture, including the following steps:

[0034] Step S1: Instruction / data virtual and real address conversion module, call the instruction / address hit judgment, refresh and fill replacement module to obtain the final physical address;

[0035] Step S2: The command / data hit module searches the command / data entry storage module according to the input instruction fetch command to see if it is a hit, and if it hits, it performs virtual and real address replacement, and if it does not hit, it performs memory access processing;

[0036] Step S3: the instruction / data refresh module refreshes the effective bits of the data in the instruction / data entry storage module according to the instruction fetch instruction;

[0037] Step S4: The instruction / data filling replacement mo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More