DMOS transistor containing field plate and manufacturing method thereof

A transistor and field plate technology, applied in the field of DMOS devices and their fabrication, can solve problems such as reducing device performance, and achieve the effects of increasing electric field distribution length, improving performance, and reducing possibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further explained below in conjunction with the accompanying drawings.

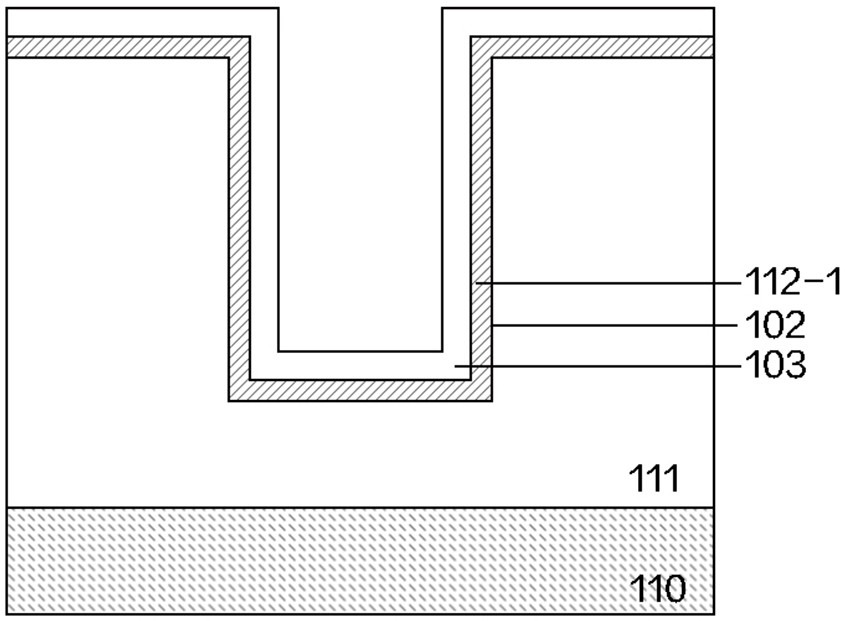

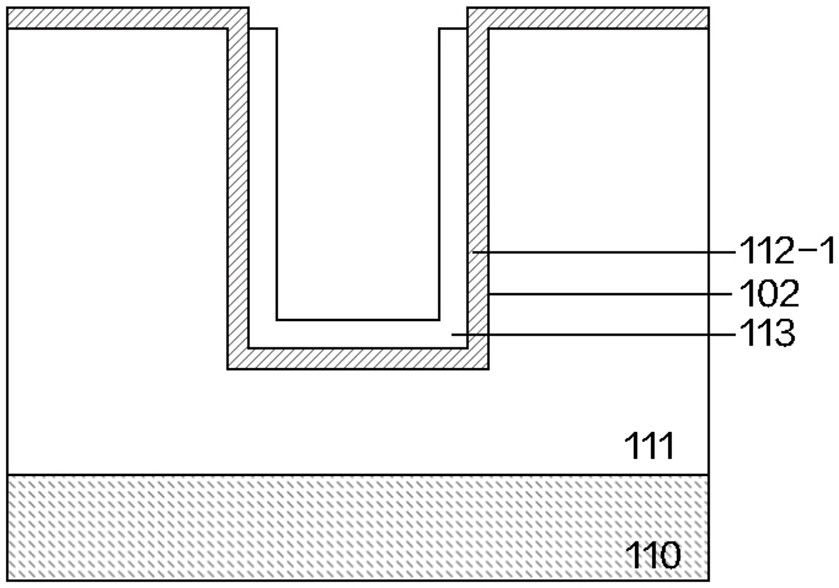

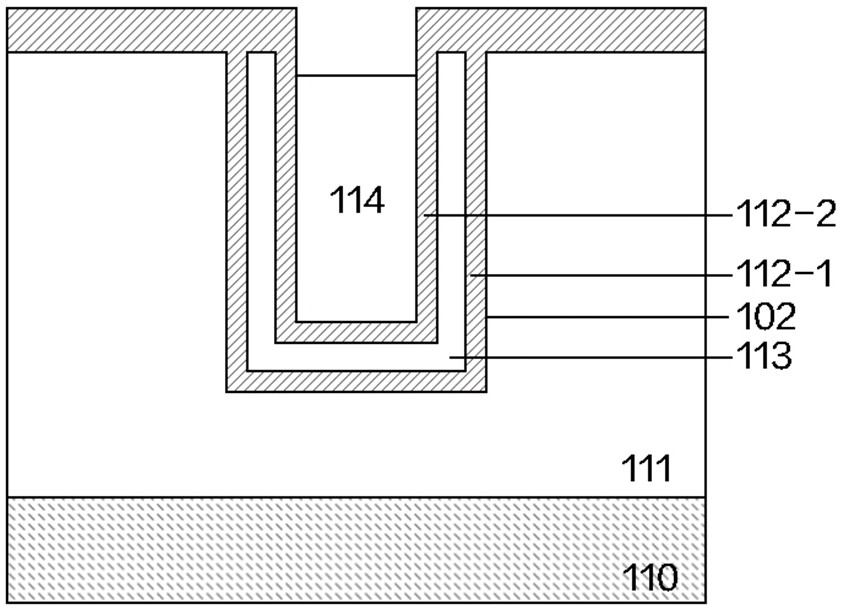

[0027] like figure 1 As shown, a DMOS transistor with a field plate includes a metallized drain 100 , an N-type heavily doped substrate 110 , and an N-type drift region 111 , which are sequentially stacked from bottom to top.

[0028] A deep trench structure 102 is provided in the N-type drift region 111, and the deep trench structure 102 includes a first oxide layer 112-1, a second oxide layer 112-2, a third oxide layer 112-3, and a fourth oxide layer 112-4. The first oxide layer 112 - 1 is a U-shaped structure embedded in the N-type drift region 111 , and the upper surface of the first oxide layer 112 - 1 is flush with the upper surface of the N-type drift region 111 . The second oxide layer 112-2 has a U-shaped structure inside the first oxide layer 112-1, and the first oxide layer 112-1 and the second oxide layer 112-2 are isolated by a U-shaped field plate 113. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More