Formation method of semiconductor structure

A semiconductor and gate structure technology, applied in the field of semiconductor structure formation, can solve problems such as affecting the short-channel effect and affecting the transistor channel mobility, and achieve the effect of suppressing the short-channel effect and improving the stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] It should be noted that "surface" and "upper" in this specification are used to describe the relative positional relationship in space, and are not limited to whether they are in direct contact.

[0030] As described in the background art, the performance of the semiconductor structure formed by the existing FinFET technology needs to be improved. Now combined with a semiconductor structure to illustrate the analysis.

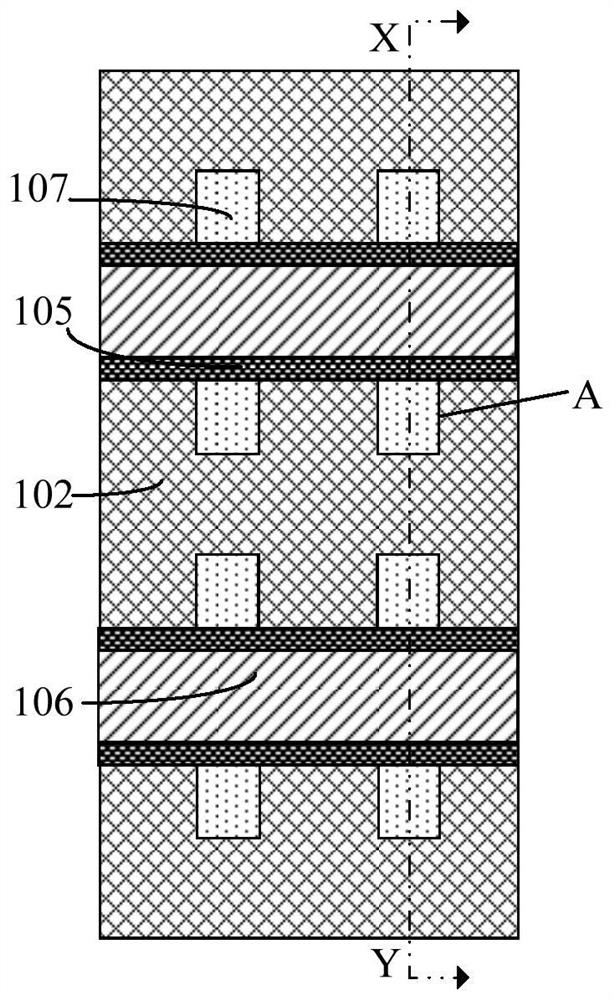

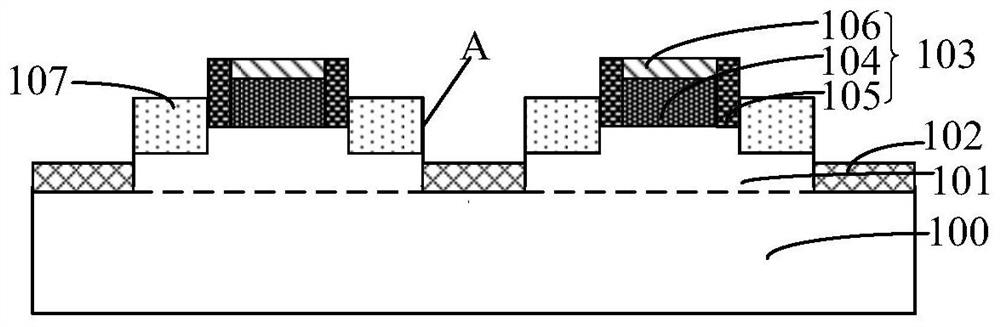

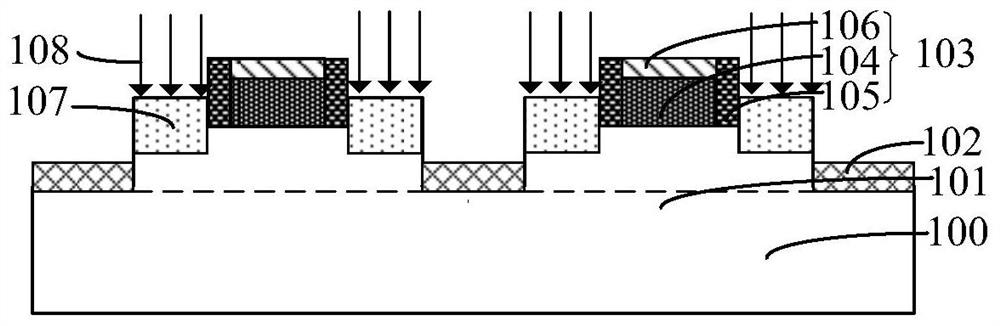

[0031] Figure 1 to Figure 3 It is a cross-sectional schematic diagram of the formation process of a semiconductor structure.

[0032] Please refer to figure 1 and figure 2 , figure 1 is a top view, figure 2 Yes figure 1 A schematic diagram of a cross-sectional structure along the XY direction, a substrate is provided, the substrate includes a base 100 , fins 101 and isolation structures 102 located on the base 100 , and the isolation structures 102 are also located on the sidewalls of the fins 101 , and the top surface of the isolation struct...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More