Preparation method of CMOS phase inverter based on GaOx-NMOS/GaN-PMOS

A channel layer and buffer layer technology, applied in the field of materials, can solve the problems of device performance impact, poor heat dissipation, complex circuit, etc., and achieve the effect of good heat dissipation and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

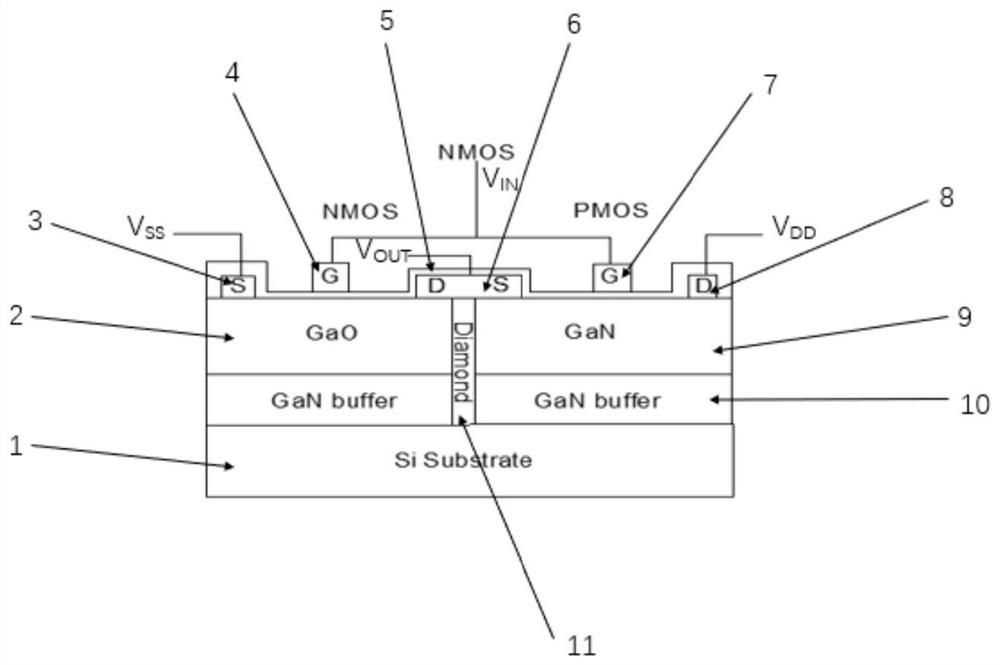

[0023] In order for those skilled in the art to better understand the solutions of the present invention, the technical solutions in the embodiments of the present invention will be clearly and completely described below with reference to the accompanying drawings in the embodiments of the present invention.

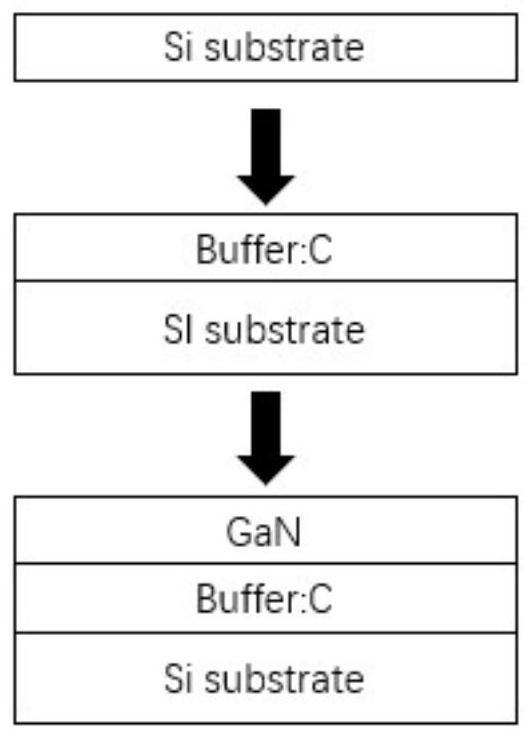

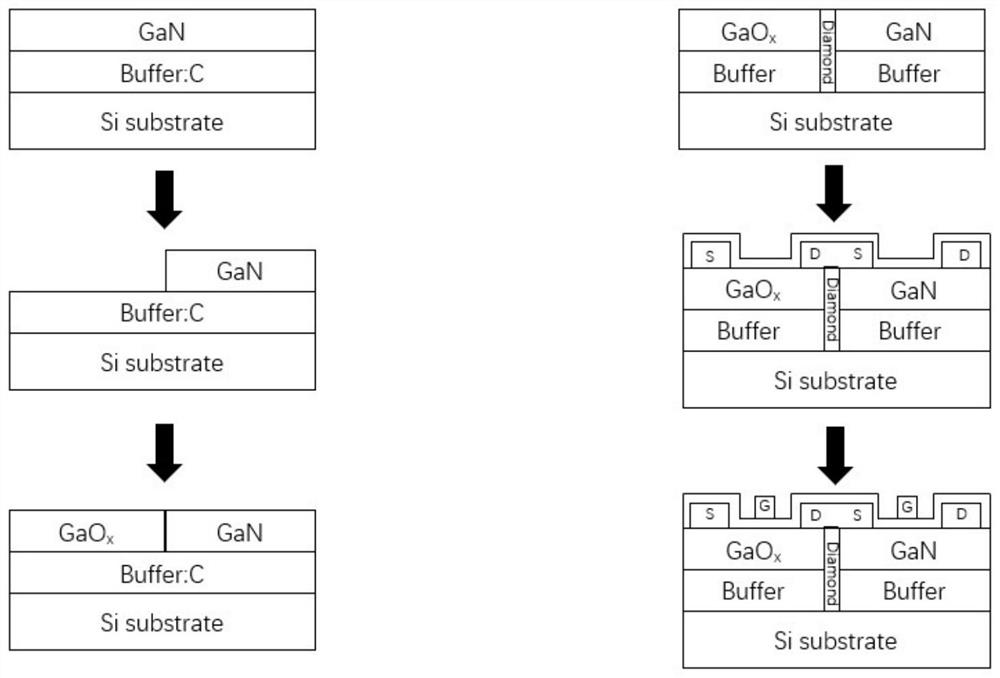

[0024] An embodiment of the present invention provides a GaO-based x -The preparation method of the CMOS inverter of NMOS / GaN-PMOS, comprises the following steps:

[0025] Step 1: Grow a carbon-doped GaN buffer layer on a single crystal Si substrate, block the area on one side of the carbon-doped GaN buffer layer with photoresist, and epitaxially grow Si-GaN on the surface of the carbon-doped GaN buffer layer to form p-MOS The channel layer is etched in part of the surface of the n-MOS channel layer until the carbon-doped GaN buffer layer, using SiO 2 Epitaxial growth of Mg-GaO on the exposed carbon-doped GaN buffer layer as a growth mask x forming an n-MOS channel lay...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More