FDSOI device and manufacturing method thereof

A device and slot filling technology, applied in the field of FDSOI devices and their manufacturing, can solve problems such as poor heat dissipation performance and affect device performance, and achieve the effects of simplifying production processes, improving device performance, and reducing production costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

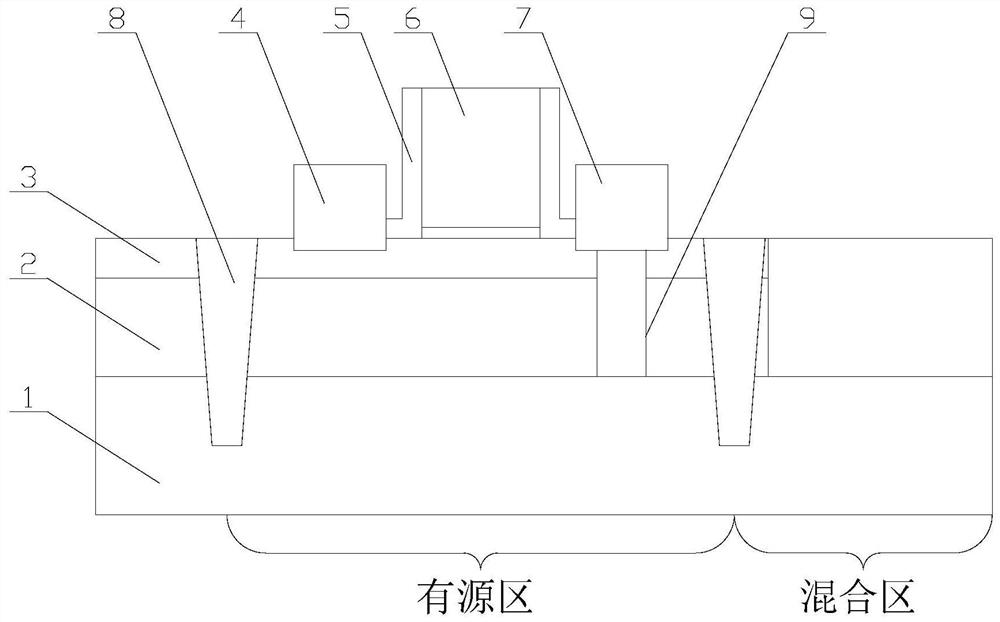

[0025] Example 1: as figure 1 As shown, an FDSOI device includes a substrate 1, a buried oxide layer 2 and a silicon-on-insulator layer 3 arranged in sequence from bottom to top, and a source electrode 4, a drain electrode 7 and a gate electrode 6 are provided on the top of the silicon-on-insulator layer 3 , the gate 6 is located between the source 4 and the drain 7, the sidewall of the gate 6 is provided with a sidewall 5, the gate 6 dielectric is silicon oxide, and the drain 7 is provided with a filling groove 9 with a width of 20nm, The filling trench 9 extends to the substrate 1 and is filled with silicon inside the filling trench 9 .

[0026] In this embodiment, since the thermal conductivity of silicon is better than that of silicon oxide in the buried oxide layer 2, the rate of heat transfer to the substrate 1 can be accelerated, and the rate of heat dissipation due to the hot carrier effect near the drain can be accelerated. Effectively improve the self-heating effect...

Embodiment 2

[0027] Embodiment 2: an FDSOI device, comprising a substrate 1, a buried oxide layer 2 and a silicon-on-insulator layer 3 arranged sequentially from bottom to top, and a source electrode 4, a drain electrode 7 and a gate electrode are provided on the top of the silicon-on-insulator layer 3 6. The gate 6 is located between the source 4 and the drain 7, a sidewall 5 is provided on the side wall of the gate 6, and the dielectric of the gate 6 is silicon oxide and high-K metal oxide arranged alternately from bottom to top. , the silicon oxide and the high-K metal oxide form a stacked structure, the drain 7 is provided with a filling groove 9 with a width of 100 nm, the filling groove 9 extends to the substrate 1, and the filling groove 9 is filled with silicon. High-K oxide has a high dielectric constant, which can increase the physical thickness of the gate dielectric while keeping the gate capacitance unchanged, so as to achieve the dual purpose of reducing gate leakage current a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More