Method for crystallizing silicon layer

A technology of crystalline silicon and amorphous silicon layers, applied in transistors, optics, instruments, etc., can solve problems such as the deterioration of electron mobility and uniformity of the silicon layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0054] 8a to 8g are schematic diagrams of the manufacturing process of TFT after crystallization of amorphous silicon according to the present invention.

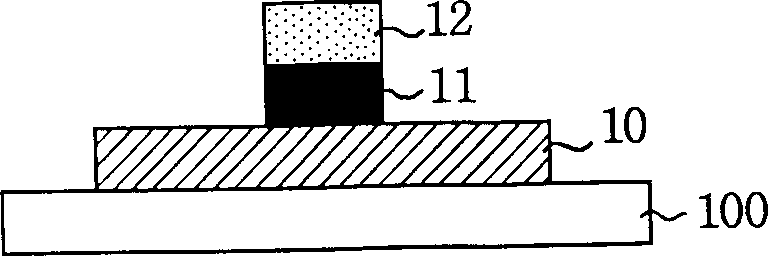

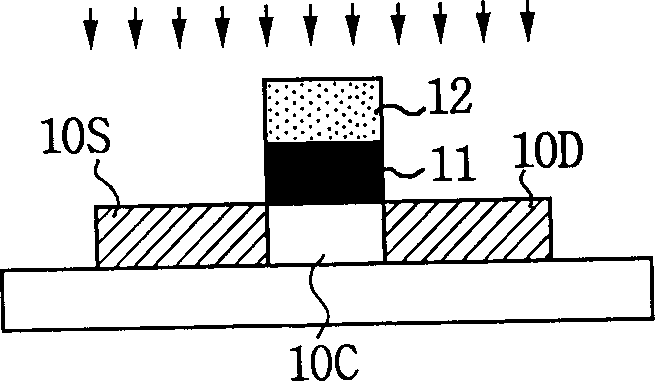

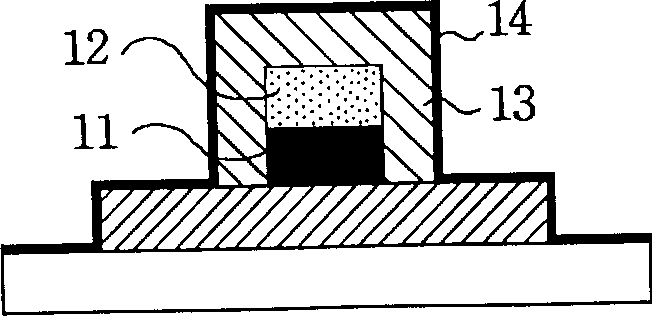

[0055] 8a and 8a are respectively a cross-sectional view and an explanatory state view. A bottom insulating layer 81 and an amorphous silicon layer 82 of appropriate thickness are formed on a glass substrate, and a layout of a desired shape is formed. The purpose of forming the bottom insulating layer is to avoid diffusion contamination of the silicon layer when forming the TFT active layer. However, depending on circumstances, a thin layer of amorphous silicon may be directly formed on the substrate without the bottom insulating layer 81 . Amorphous silicon is formed using methods such as low-pressure CVD (Chemical Vapor Deposition), high-pressure CVD, and plasma-enhanced CVD, and the like. The amorphous silicon layer 82 is formed on the substrate by means of the use of a masked photoresist to form a crystalline source la...

Embodiment 2

[0068] Figure 9 is a partial cross-sectional view describing another method of manufacturing a TFT according to the present invention. In the previous embodiment described with reference to Figures 8a-8g, the polysilicon source region 83, the crystalline filter channel 84 and the active layer 85 were formed using a pattern on the polysilicon layer 82, and the MIC source metal layer 87 was It is formed to cover part of the crystalline source region 83, as shown in FIG. 8a and FIG. 8a'. However, in Figure 9 In an embodiment of the present invention, the MIC source metal 94 is first formed on the bottom insulating layer 81, and the amorphous layer 82 is deposited thereon. The amorphous silicon layer is then patterned to create crystalline source regions 95, crystalline filter channels 96 and active regions 97, respectively.

[0069] Obviously, if Figure 9 If the structure is thermally crystallized as described in Embodiment 1, the same effect as described in Embodiment 1 a...

Embodiment 3

[0071] Although Embodiment 1 deposits the MIC source metal 87 on the MIC region 86 of the crystalline source region 83, it is also possible to implant the MIC source metal into the MIC region. By using a photoresist mask to form a source metal implant in the crystalline source region exposing only the MIC region 86, the MIC source metal such as Ni can be implanted only in the MIC region. After metal implantation, the photoresist mask is removed. Then, a TFT having a crystalline active layer can be fabricated by the same process as in the above-mentioned related embodiment 1.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More