Method for providing dopant level for polysilicon for flash memory devices

A technology for writing memory and doping, which is applied in the field of flash memory devices and can solve the problems of charge gain and loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

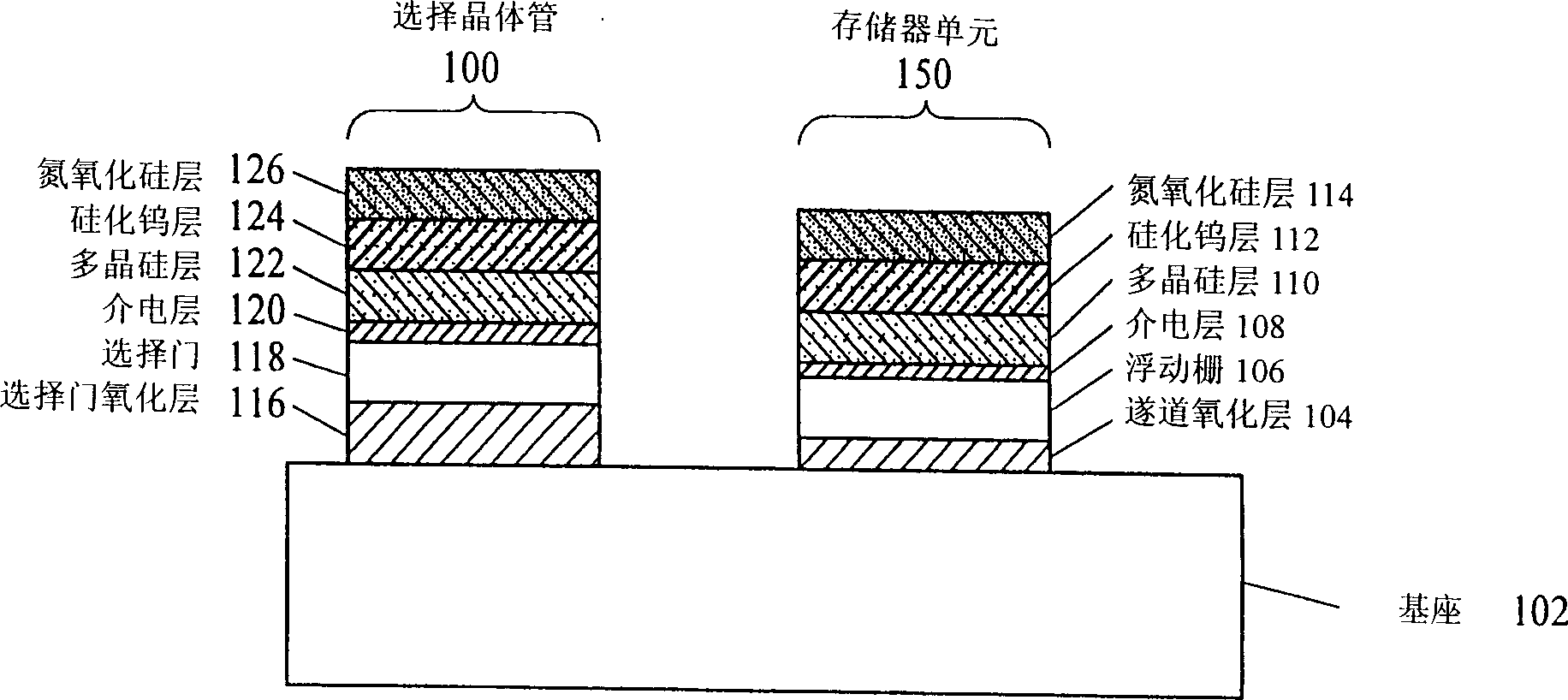

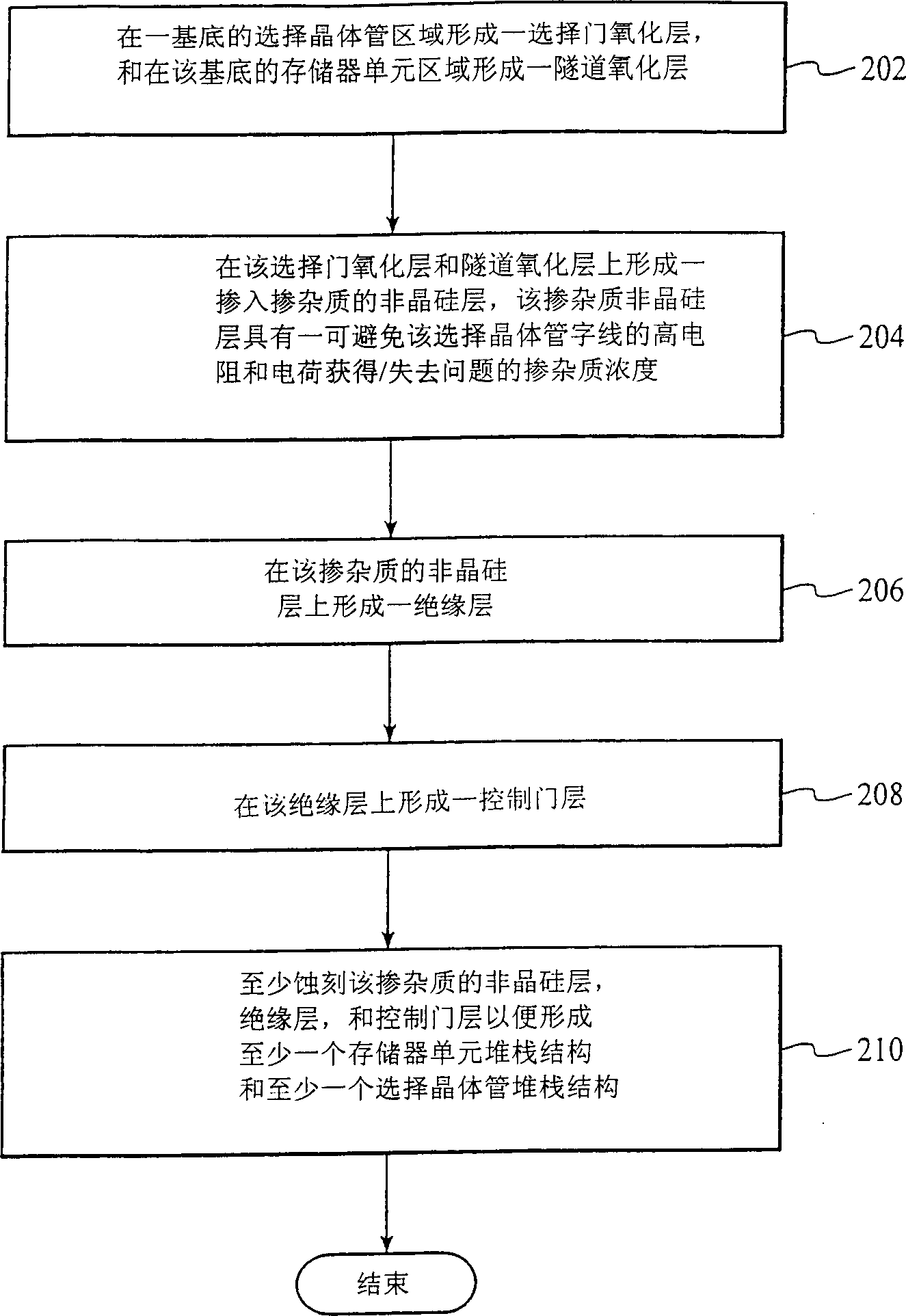

[0013] The present invention provides a method and NAND type flash memory device that provides a polysilicon dopant concentration that avoids high resistance and charge gain / loss problems of select transistor word lines. The description presented below will enable a person skilled in the art to make and use the invention and is provided in a patent application and its required text. Various modifications of this preferred embodiment will be clear to those skilled in the art and the general principles here will be applied to other embodiments. Therefore, the present invention is not limited to the scope disclosed by this embodiment, but is suitable for use with The broadest category in which the principles and characteristics described are consistent.

[0014] The method according to the invention will avoid the select transistor word line high resistance problem and charge gain / loss problem by providing the dopant concentration of the polysilicon layer, which is phosphorus dop...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More