Method of reducing microparticle residue and defect

A technology of manufacturing method and rinsing method, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., and can solve the problems of changing the overall dielectric properties of the ONO dielectric layer 30 and prolonging the soaking time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

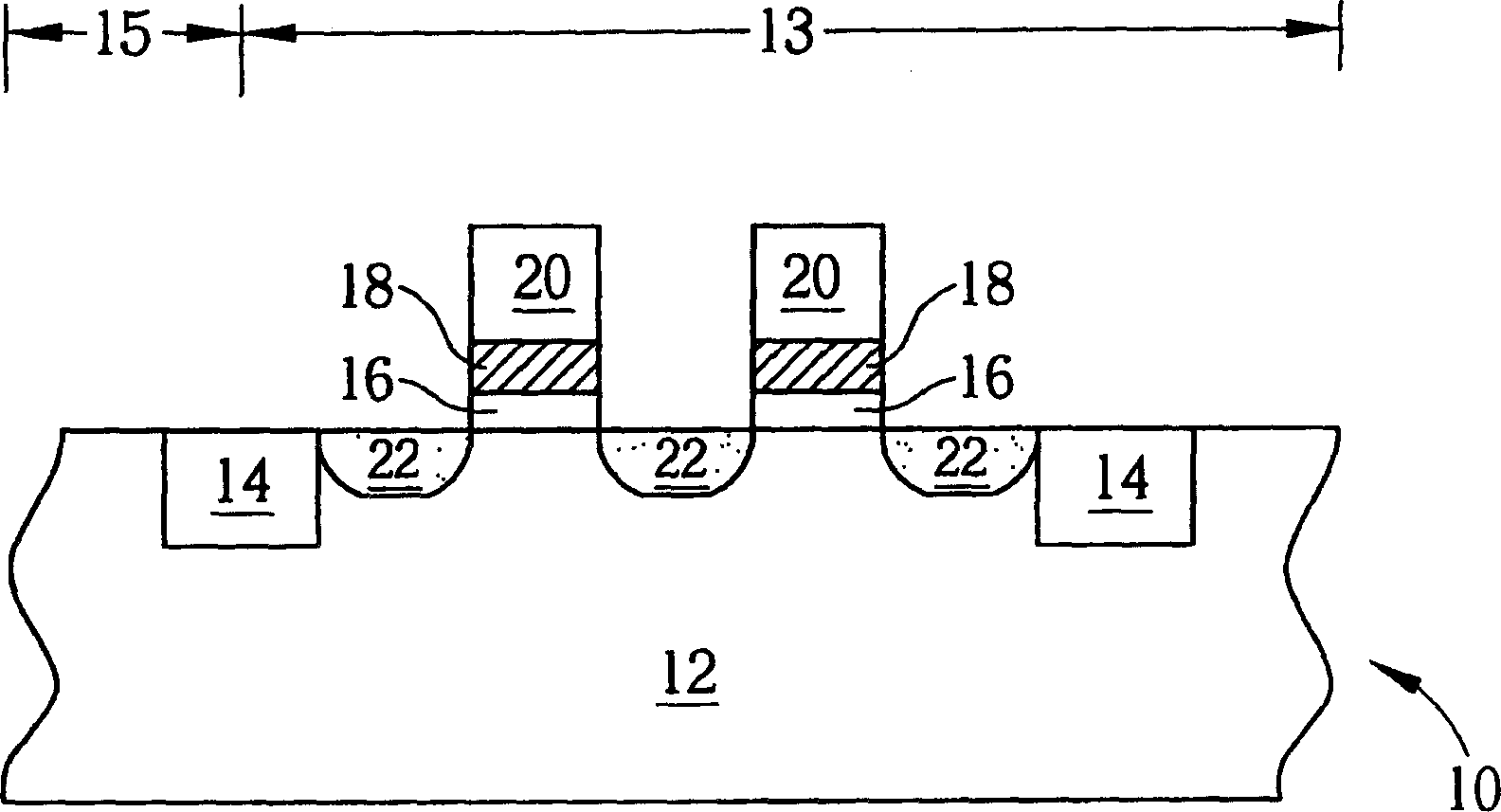

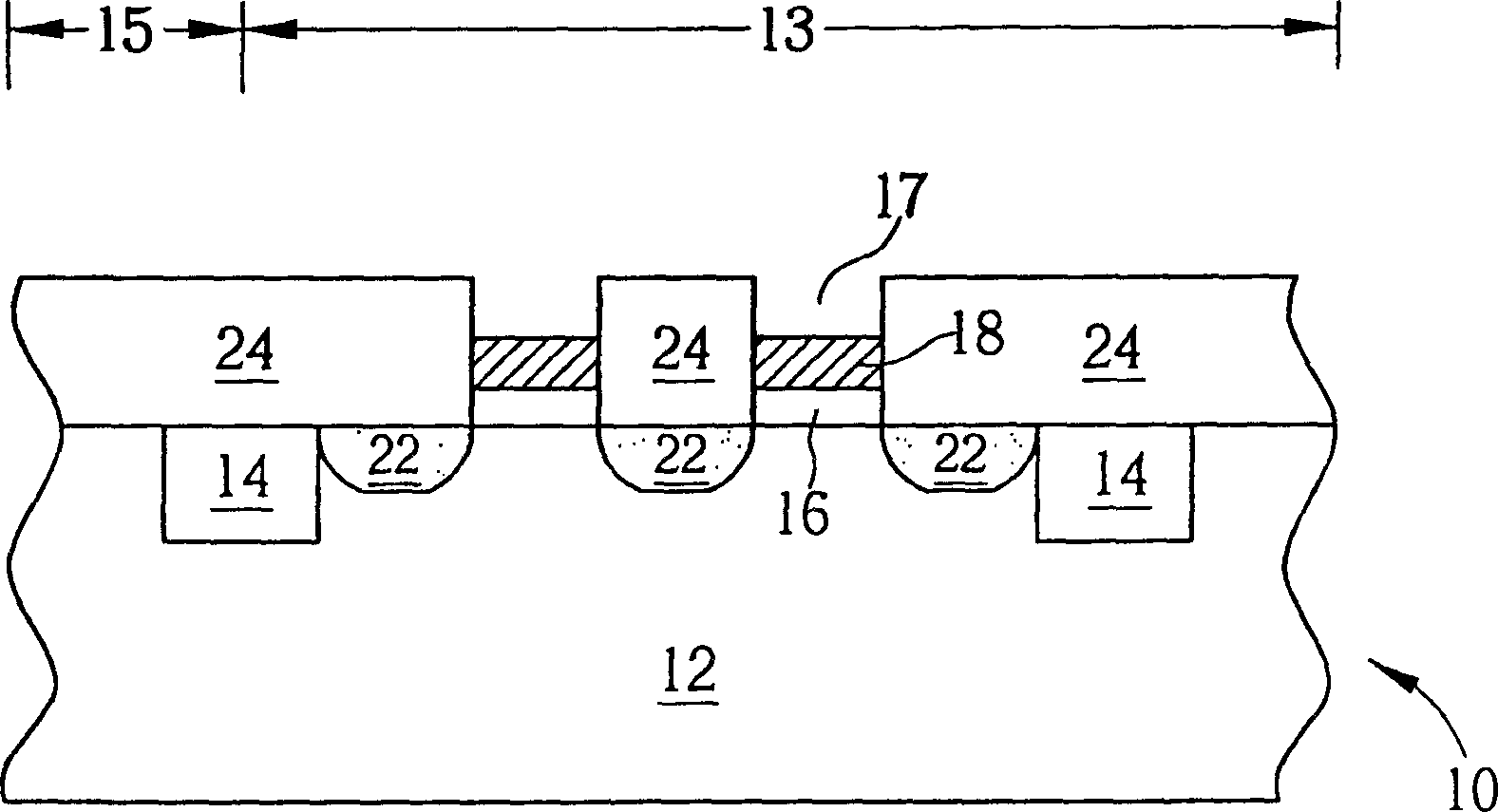

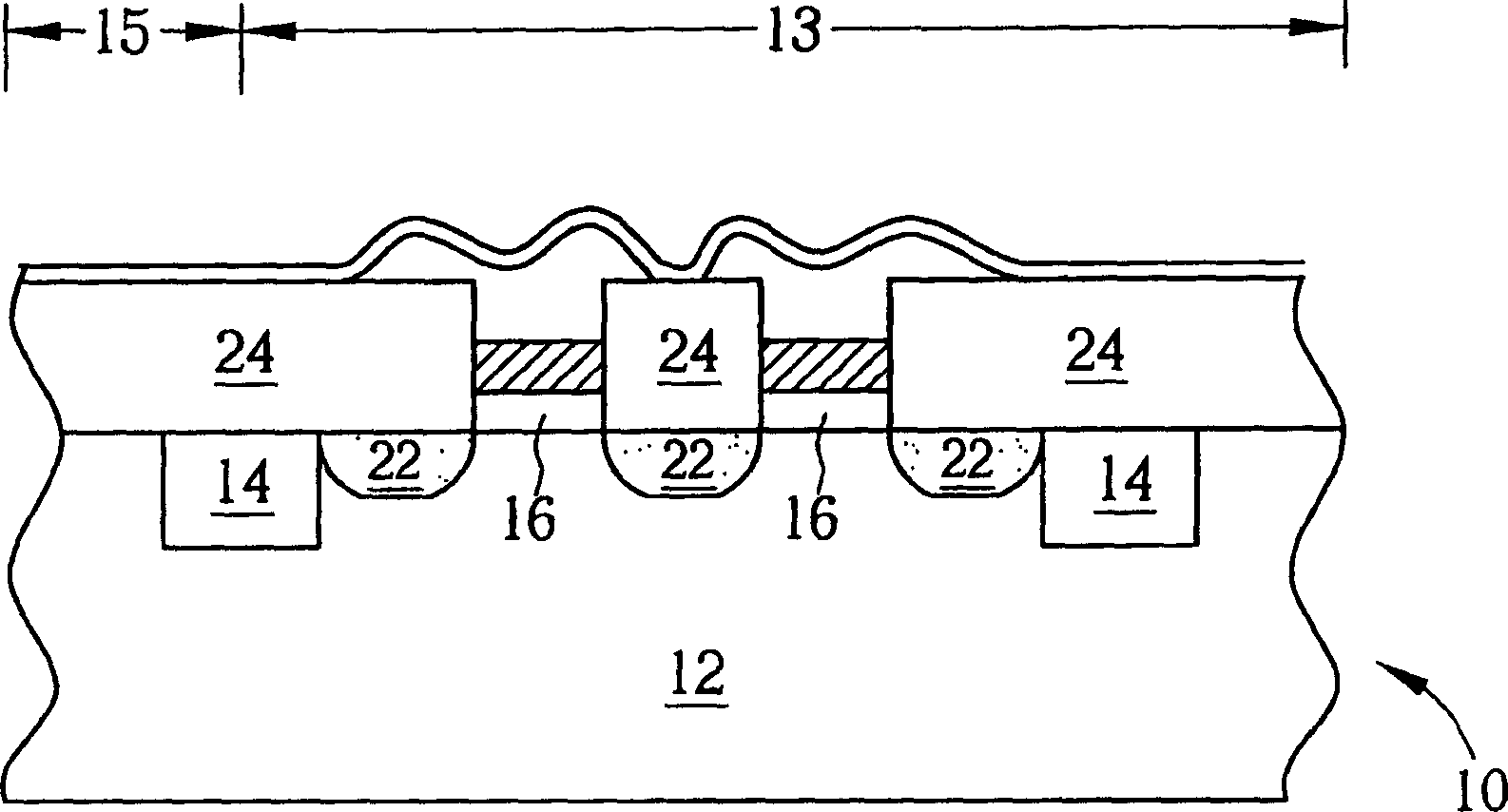

[0030] Please refer to Figure 6 to Figure 12 , Figure 6 to Figure 12 It is a schematic diagram of the method for making a semiconductor chip with an ONO structure according to the present invention. Such as Image 6 As shown, a semiconductor chip 50 includes a silicon substrate 52, wherein the silicon substrate 52 includes an N-type well 56, and a P-type well 58 located in the N-type well 56, and another buffer oxide layer 54 is located on the substrate 52 , and the semiconductor chip 50 is divided into a first area 60 intended to form a memory array area (array area) and a second area 62 intended to form a peripheral area (peripheral area) by a shallow trench isolation area 57 .

[0031] Such as Figure 7 As shown, a chemical vapor deposition (CVD) process is then performed to sequentially form a polysilicon layer 64 and a silicon nitride layer 66 covering the buffer oxide layer 54 . In a preferred embodiment of the present invention, polysilicon layer 64 has a thicknes...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More