Double gate memory cell with improved tunnel oxide

A technology of memory cell and tunnel oxide layer, which is applied in the direction of electrical components, transistors, electric solid-state devices, etc., to achieve the effect of increasing the Fermi energy level difference and reducing the barrier height

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

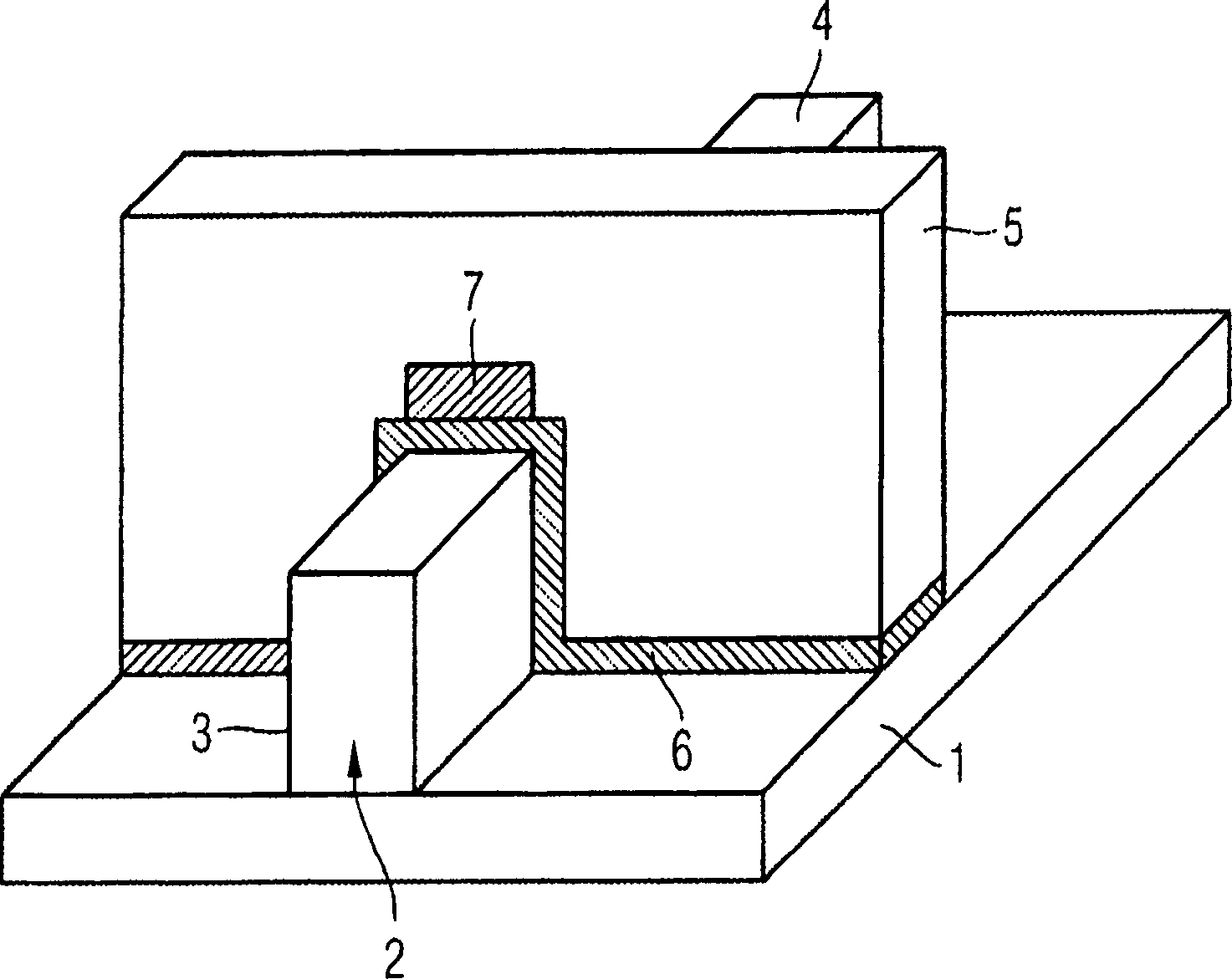

[0023] schematically showing a perspective view of a conventional FinFET transistor structure figure 1 This has already been explained at the beginning, so further description can be omitted here.

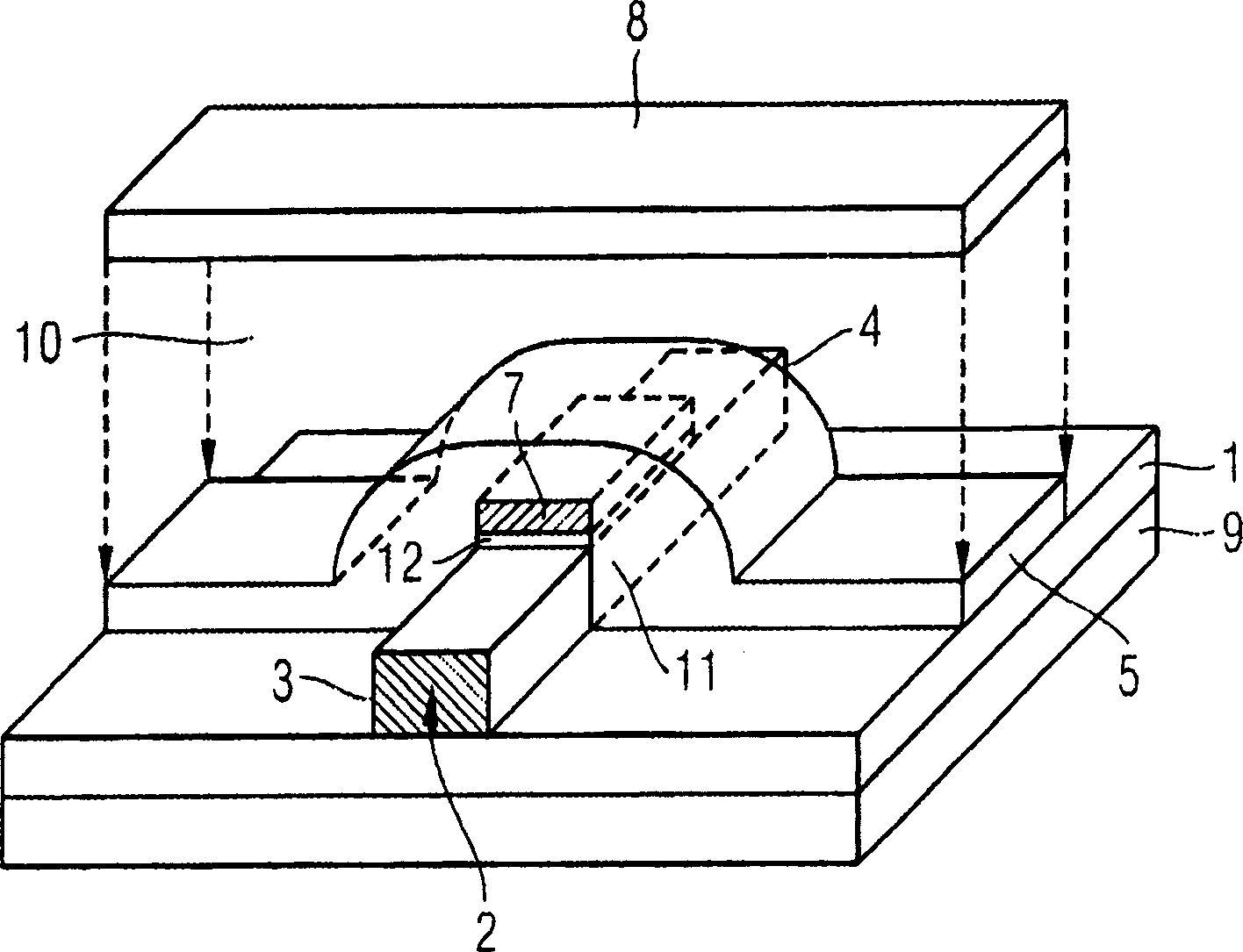

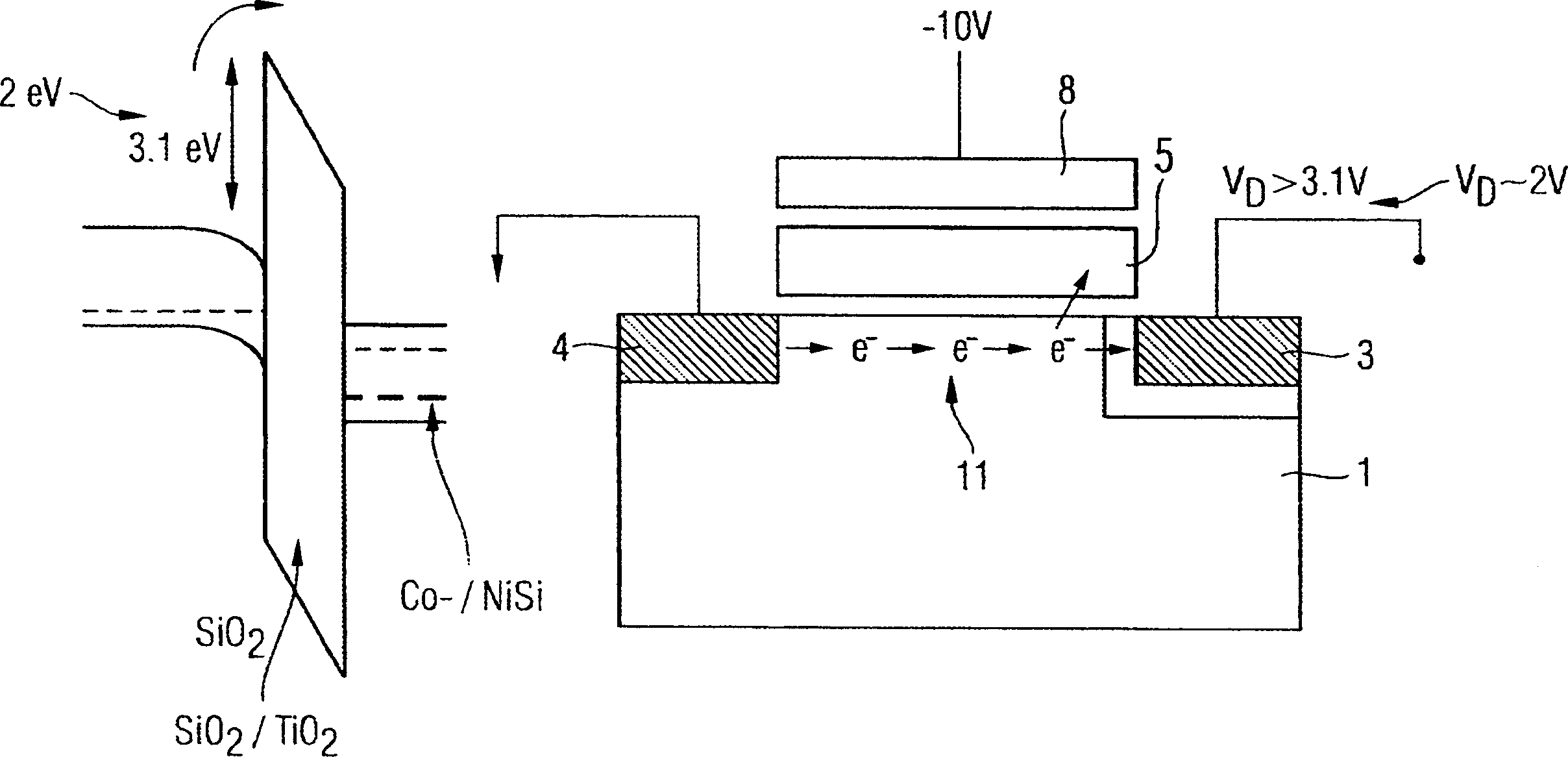

[0024] exist figure 2 The dual-gate memory cell of the present invention is schematically illustrated in . Thus, on the n-type silicon substrate 1 supported by the insulating material 9 ridged wings 2 are formed, within which ridged wings constitute the active region. The active region includes a drain region 3 and a source region 4, and a channel region 11 therebetween. The channel region 11 is surrounded by the floating gate 5 on the side parallel to the substrate surface and on both sides perpendicular to the substrate surface. A tunnel oxide layer 7 is formed between the floating gate 5 and the channel region 11 on the side parallel to the substrate surface, and electrons can tunnel through the tunnel oxide layer 7 to charge or discharge the floating gate 5 . An insulating...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More