Novel UMOS-like gate-controlled thyristor structure for ESD protection

a thyristor structure and gate control technology, applied in the direction of thyristor, electric devices, transistors, etc., can solve the problems of not being functional in lvtscr's with shallow trench isolation (sti), especially on epi, and achieve the effect of adding any process complexity and cos

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

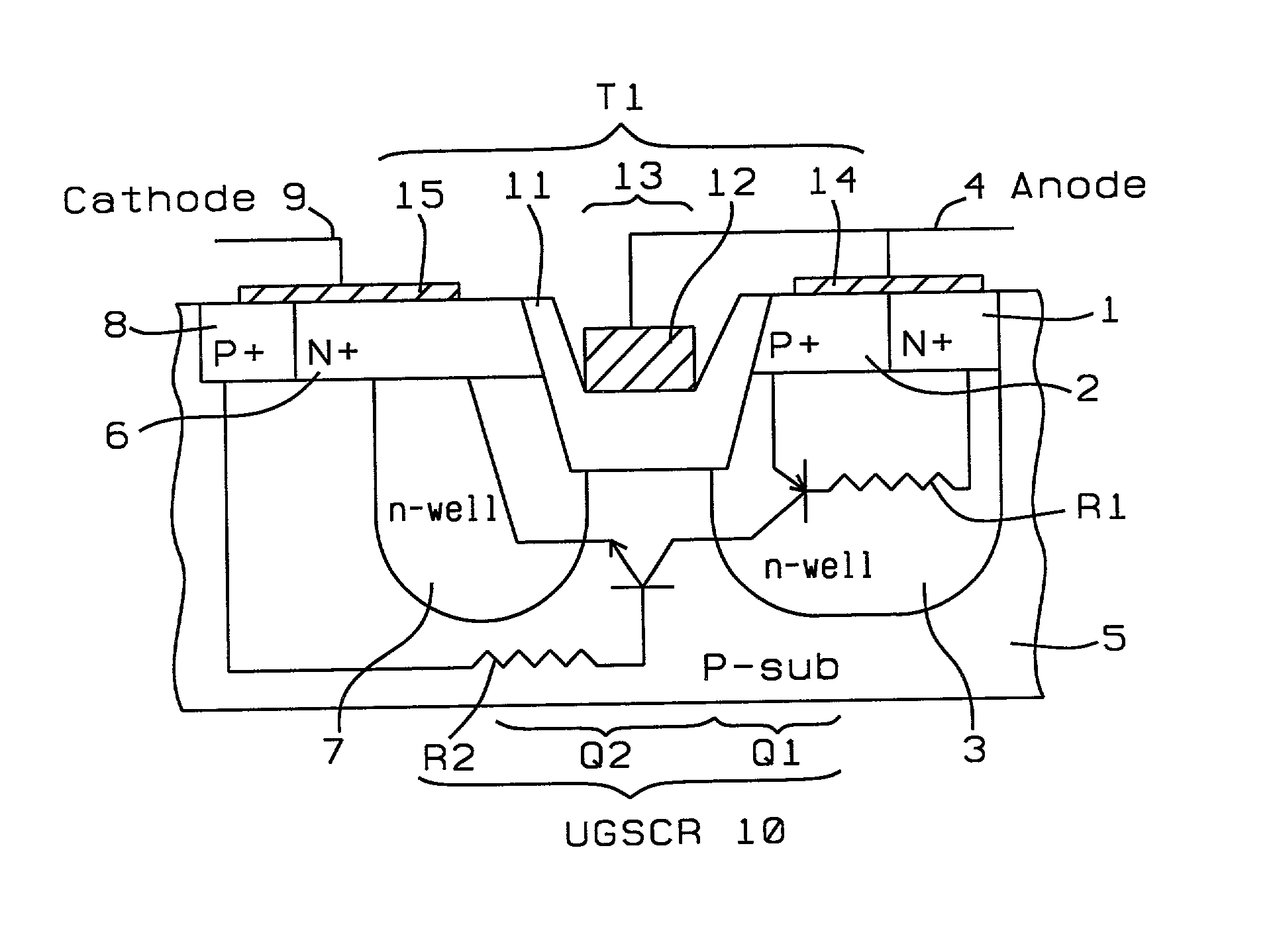

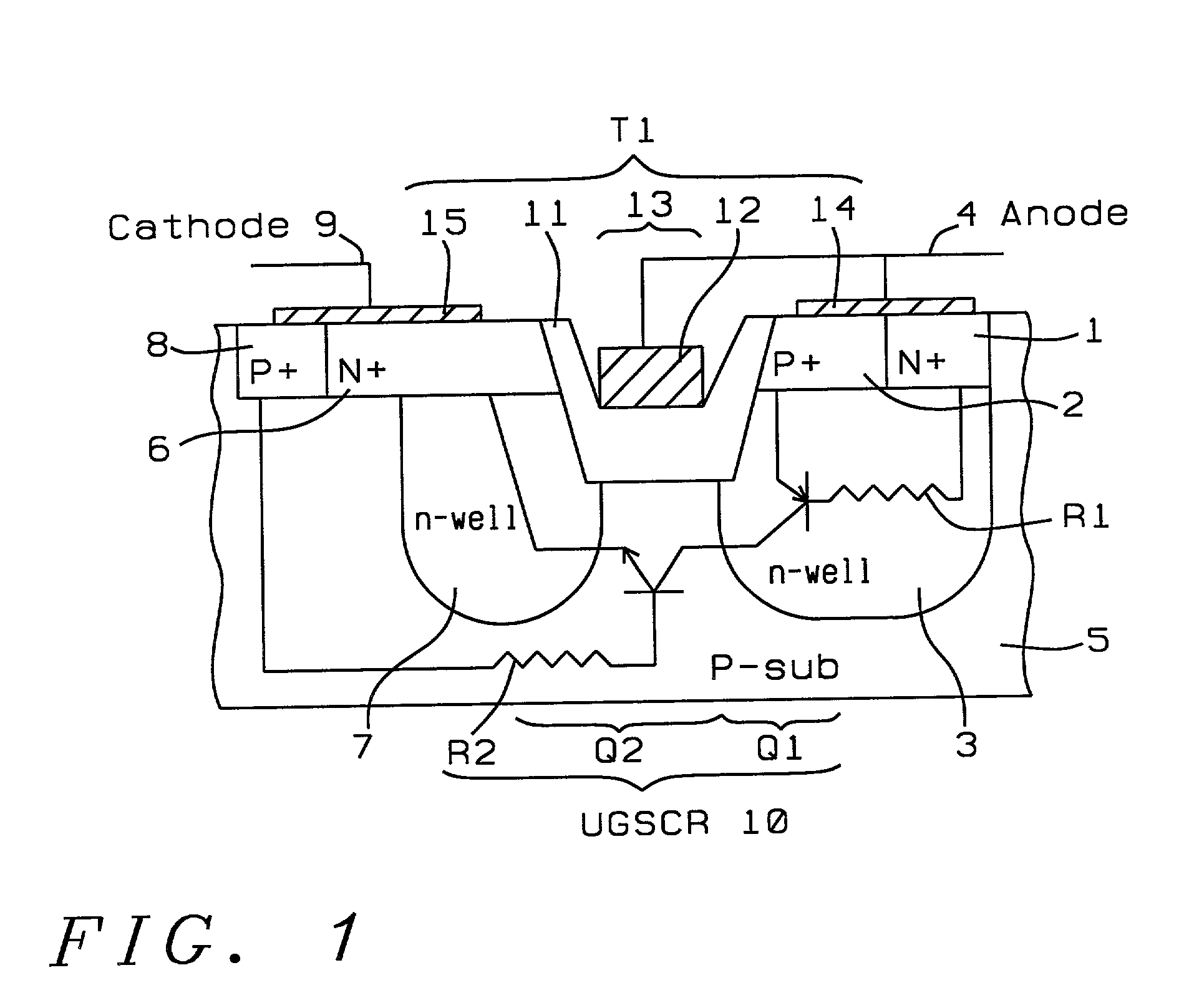

[0018] In the invention, a novel U-gate MOS (UMOS)-like gate-controlled SCR structure (UGSCR) is provided, see FIG. 1. The adjacent n+ (1) and p+ (2) diffusions in the n-well (3) are connected to the input terminal (4). A vertical parasitic pnp device (transistor) is formed with the p-substrate (5) as the collector, n-well (3) as the base, and input p+ (2) diffusion as the emitter. The n+ (6) diffusion partially on the n-well (7) located in the p-substrate (5), along with a p+ pick-up (8), is connected to the ground (9) or substrate bus and forms the emitter of the parasitic npn transistor. The base of the parasitic npn transistor is formed by the p-substrate (5) and the collector is the n-well (3) and the n-well contact (1). A UMOS-like MOS gate structure (13), comprised of a layer of silicon dioxide (11) and polysilicon gate (12) is formed between the two n-wells (3 and 7) and its gate (12) is connected to the input terminal (4).

[0019] The UGSCR structure is compatible with the se...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More