Thin-film transistor, method of producing thin-film transistor, electronic circuit, display, and electronic device

a thin-film transistor and organic semiconductor technology, applied in thermoelectric devices, instruments, optics, etc., can solve the problems of insufficient investigation on the optimum layer structure, loss of semiconductor properties, and difficulty in realizing a thin-film transistor using an organic semiconductor layer with high performance and operable with a small driving voltage, etc., to achieve low driving voltage, easy and highly reliable manner, and good transistor characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

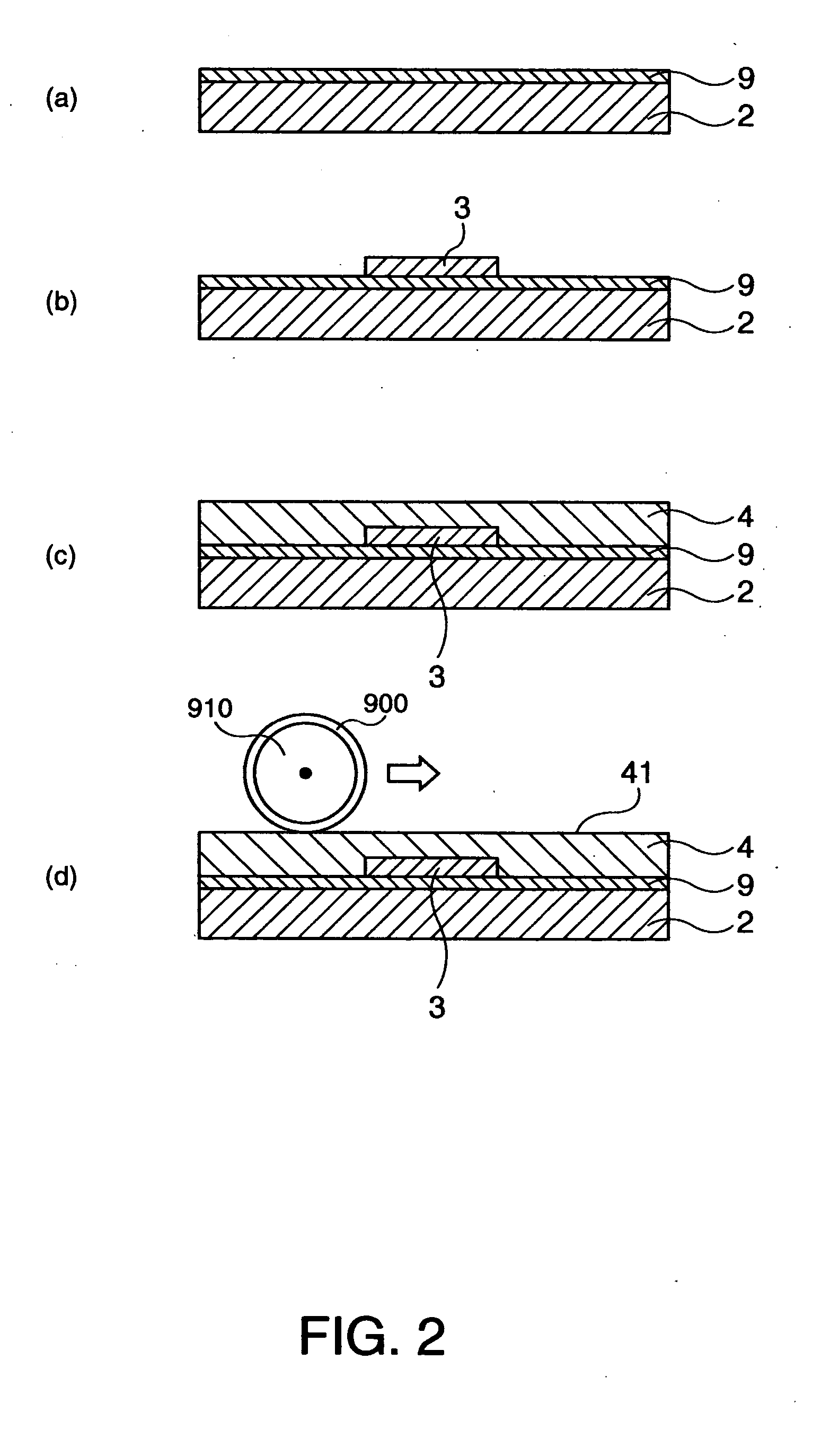

[0180] I-1: First, an underlying layer with an average thickness of 100 nm was formed by depositing SiO2 on a glass substrate by means of CVD process.

[0181] I-2: Thereafter, a Au film with an average thickness of 50 nm was formed on the underlying layer by means of vacuum evaporation, and the Au film was patterned using photolithography process so as to form a gate electrode and an interconnection line extending from the gate electrode.

[0182] I-3: A solution of a precursor of polyimide was coated by means of spin coating on the underlying layer such that the gate electrode was covered. Thereafter, heat treatment was performed at 200° C. for 1 hour thereby forming a gate insulating layer with an average thickness of 200 nm.

[0183] I-4: The upper surface of the gate insulating layer was rubbed using a rubbing apparatus to align the upper surface and a neighboring portion of the gate insulating layer into a predetermined direction. The rubbing conditions were set as follows. The push...

example 2

[0189] II-1: A step similar to step I-1 was performed.

[0190] II-2: A step similar to step 1-2 was performed.

[0191] II-3: A solution of a precursor of polyimide in the form of diallyl ketone was coated by means of spin coating on an underlying layer such that a gate electrode was covered. Thereafter, heat treatment was performed at 200° C. for 1 hour thereby forming a gate insulating layer with an average thickness of 200 nm.

[0192] II-4: Thereafter, a Au film with an average thickness of 50 nm was formed on the gate insulating layer by means of vacuum evaporation, and the Au film was patterned using photolithography process so as to form a source electrode, a drain electrode, and interconnection lines connected respectively with the source electrode and the drain electrode.

[0193] II-5: While heating the gate insulating layer at 180° C., the gate insulating layer was illuminated with polarized light emitted from a polarized light source, thereby aligning the upper surface and a ne...

example 3

[0197] III-1: A step similar to step I-1 was performed.

[0198] III-2: A step similar to step I-2 was performed.

[0199] III-3: Thereafter, SiO2 was deposited on an underlying layer by means of CVD process using TEOS (tetraethoxysilane) as a source material such that a gate electrode was covered, thereby forming an inorganic layer with an average thickness of 200 nm. A solution of a precursor of polyimide was coated by means of spin coating on the inorganic layer. Thereafter, heat treatment was performed at 200° C. for 1 hour thereby forming an organic layer with an average thickness of 20 nm.

[0200] III-4: A step similar to step I-4 was performed.

[0201] III-5: A step similar to step I-5 was performed.

[0202] III-6: A step similar to step I-6 was performed.

[0203] III-7: A step similar to step 1-7 was performed.

[0204] Thus, a thin-film transistor such as that shown in FIG. 6 was obtained.

[0205] 2. Evaluation

[0206] The carrier mobility in the channel region of the organic semicondu...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Temperature | aaaaa | aaaaa |

| Electrical conductivity | aaaaa | aaaaa |

| Semiconductor properties | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More