Patents

Literature

238 results about "Device aspects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

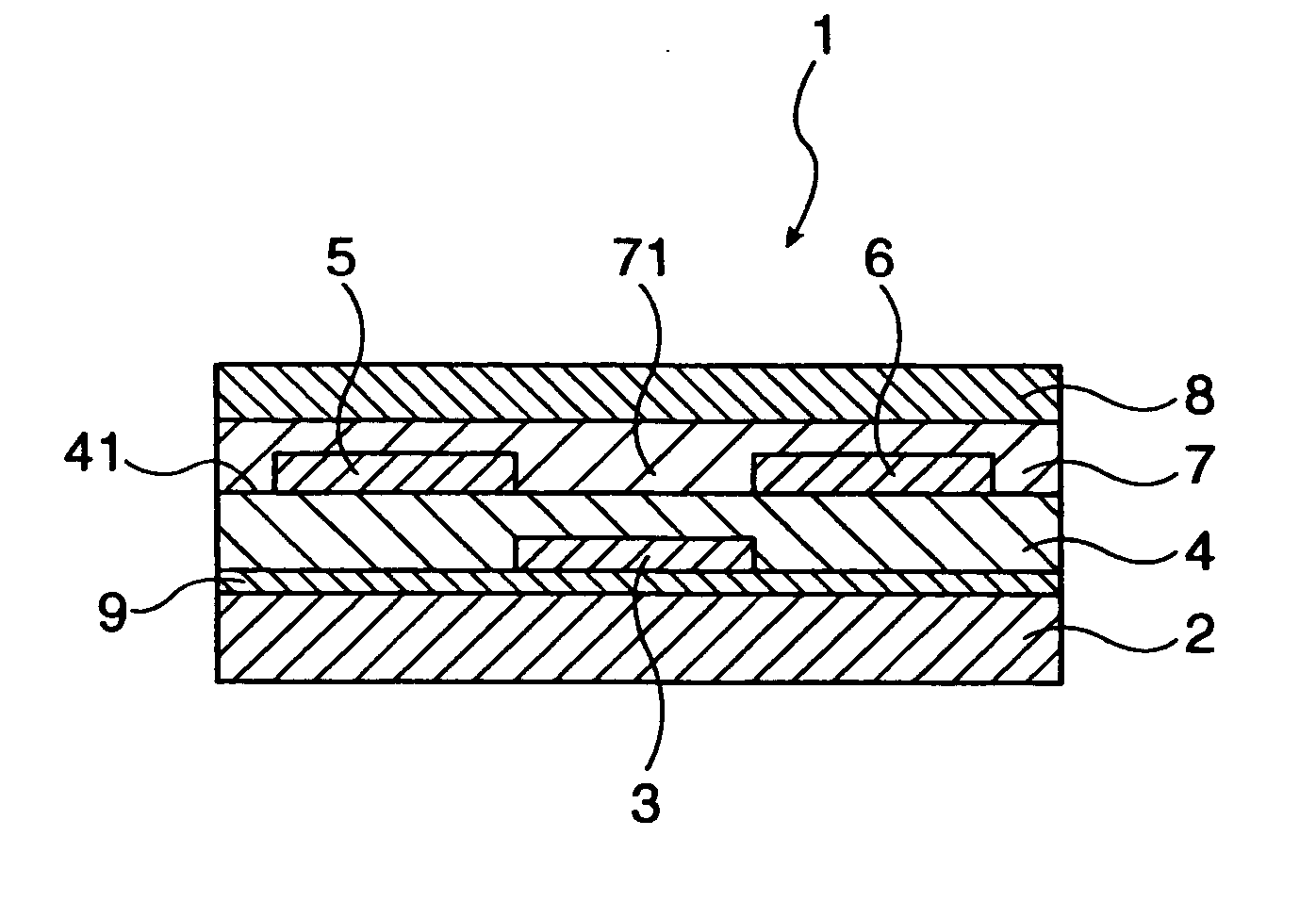

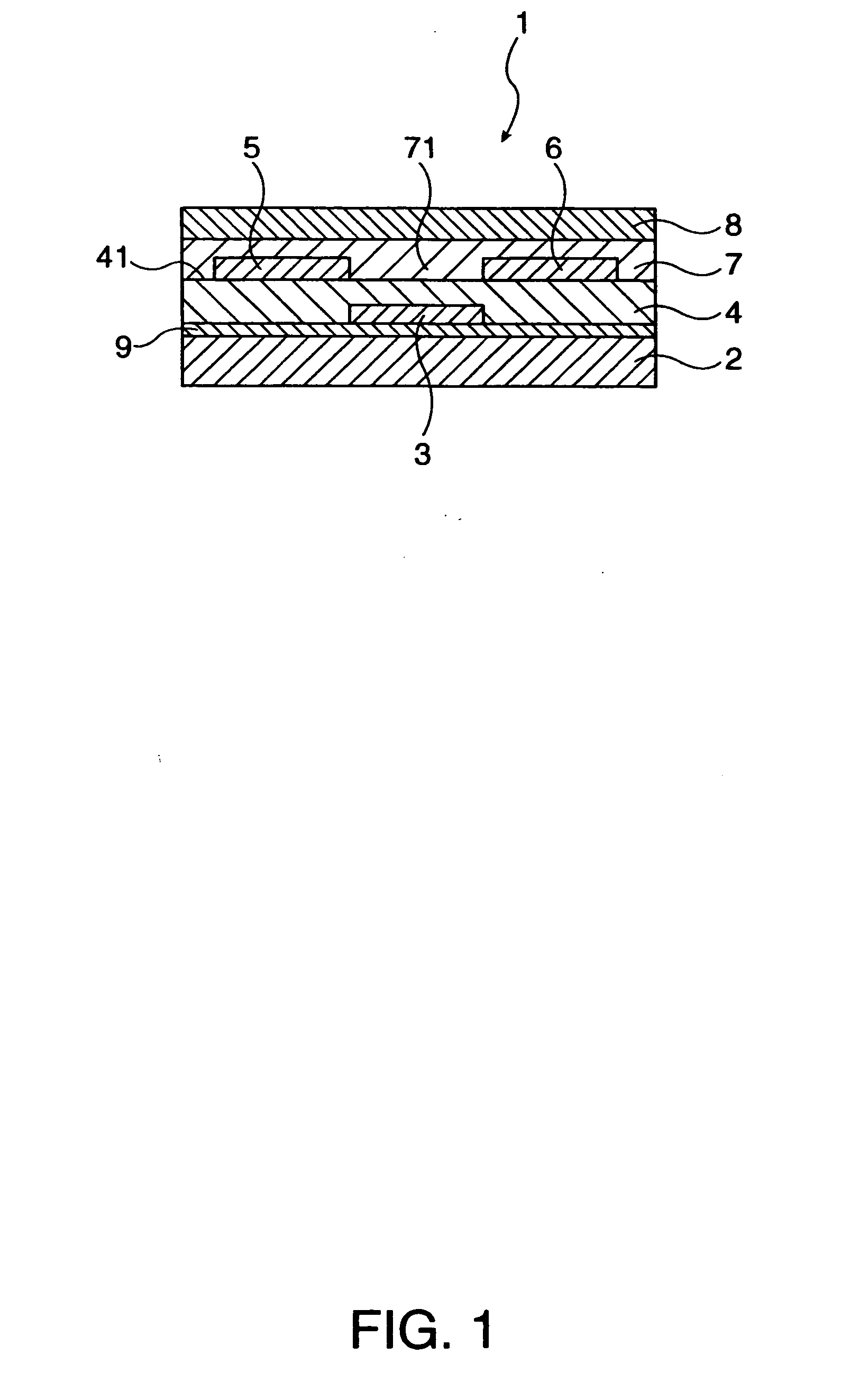

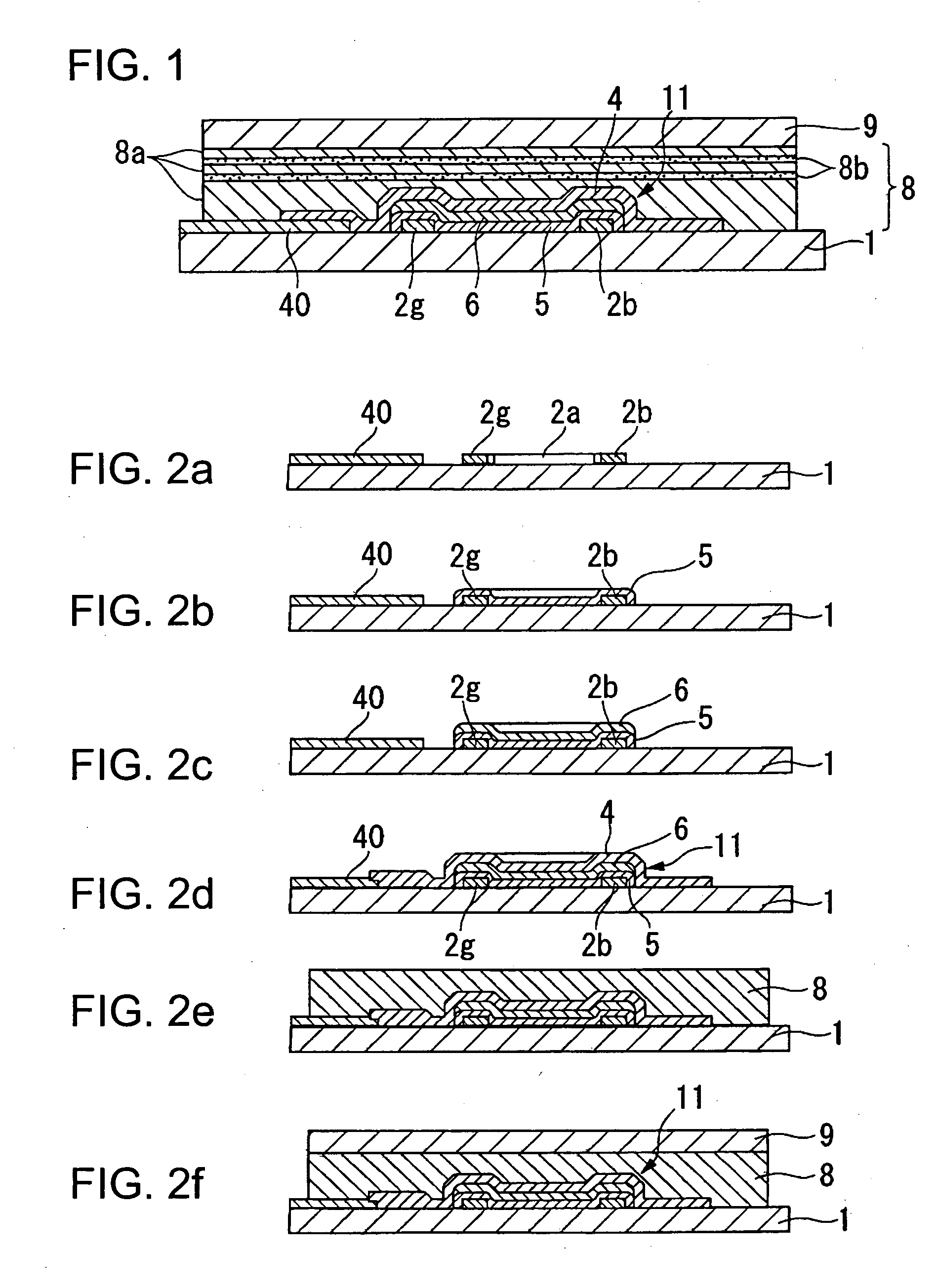

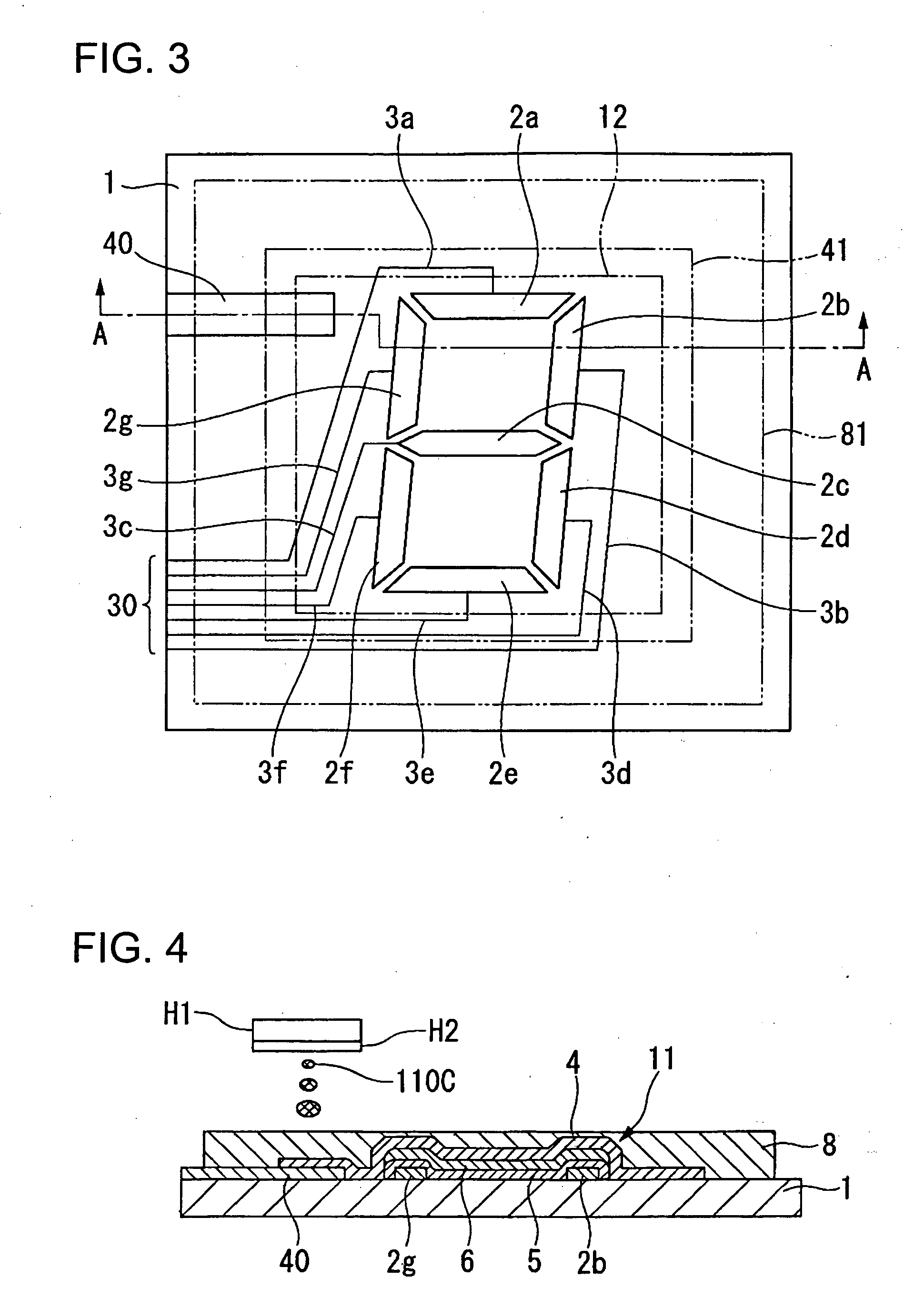

Thin-film transistor, method of producing thin-film transistor, electronic circuit, display, and electronic device

InactiveUS20050029514A1Easy and highly reliable mannerReduce the driving voltageTransistorSolid-state devicesDisplay deviceEngineering

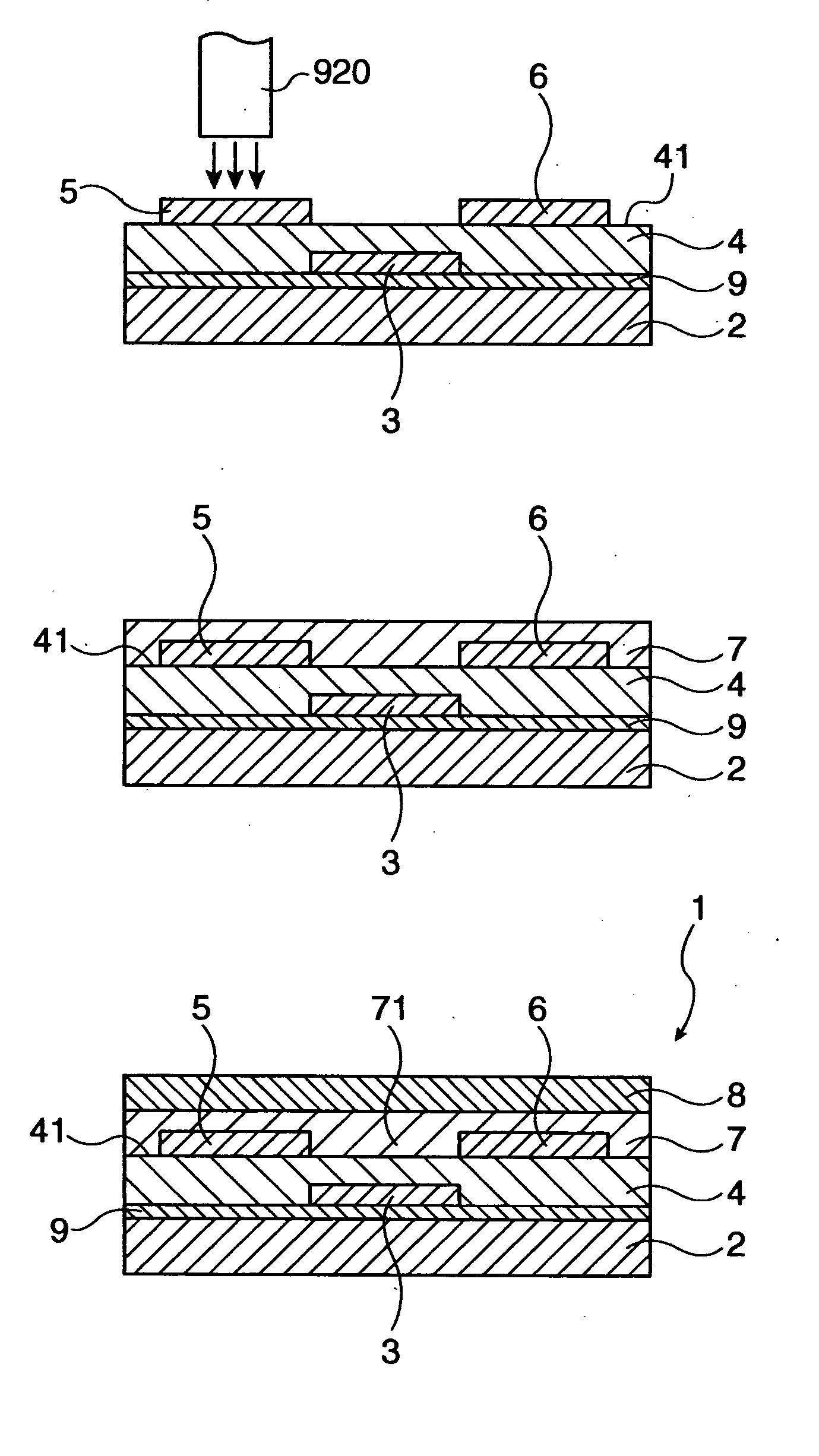

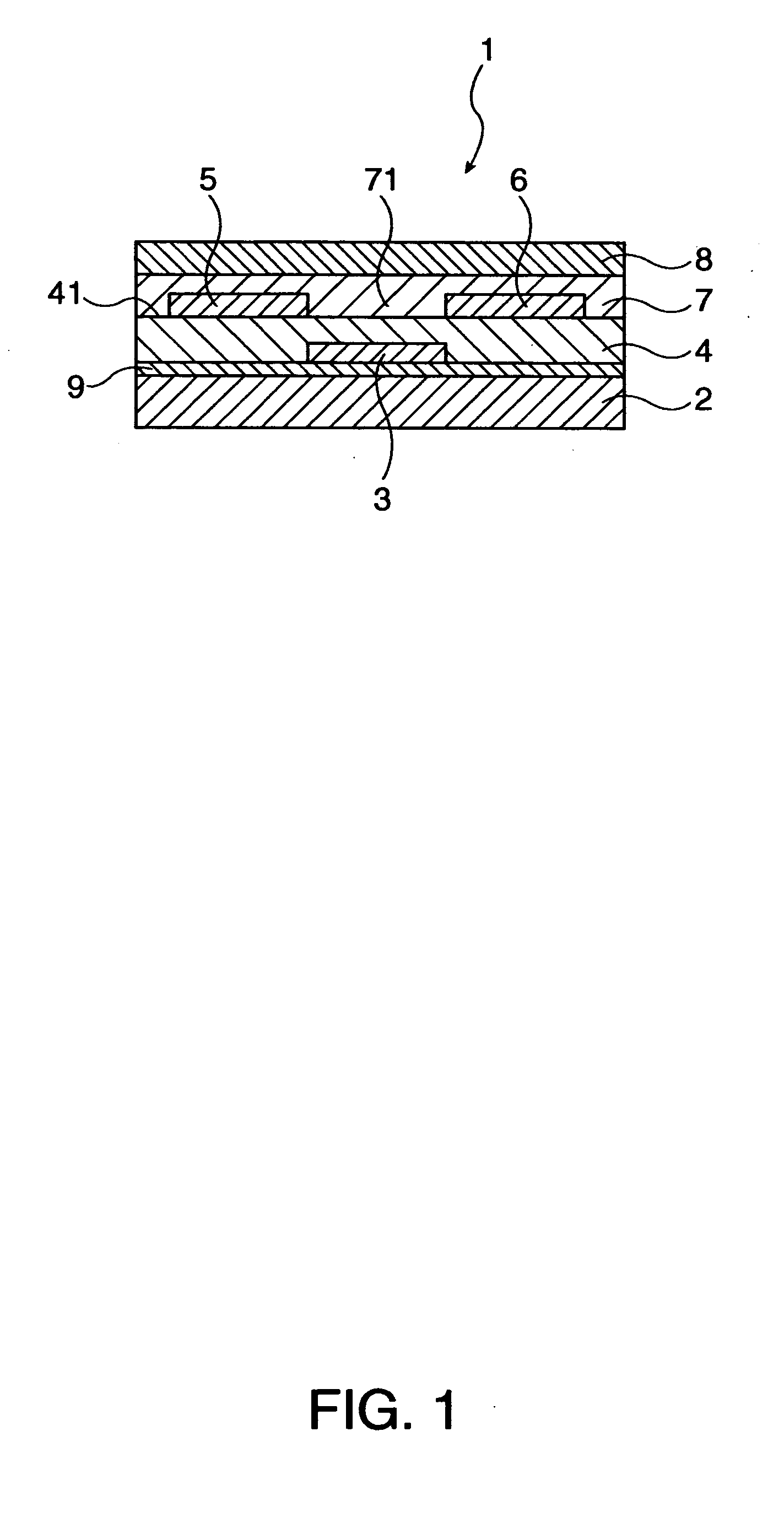

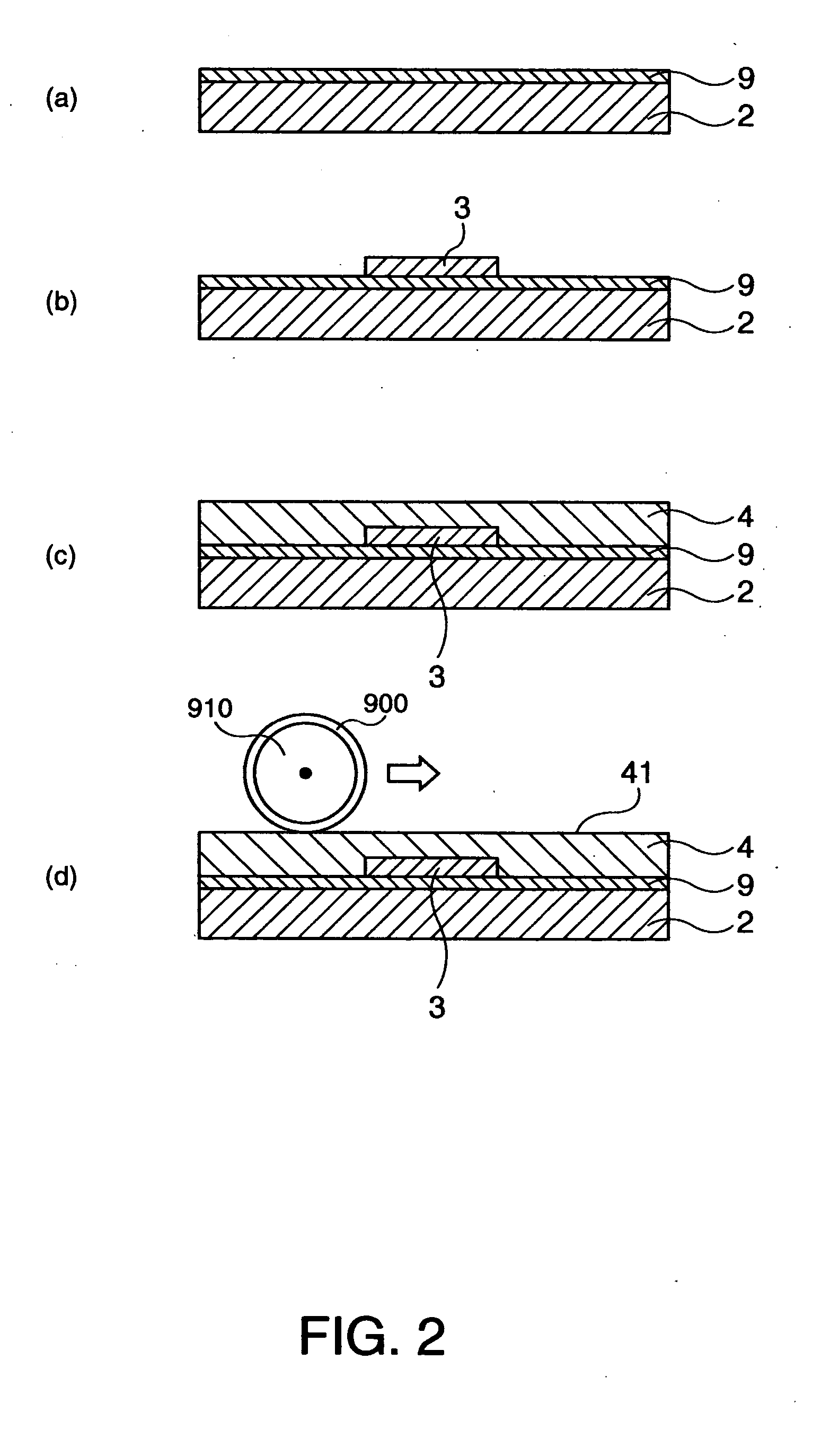

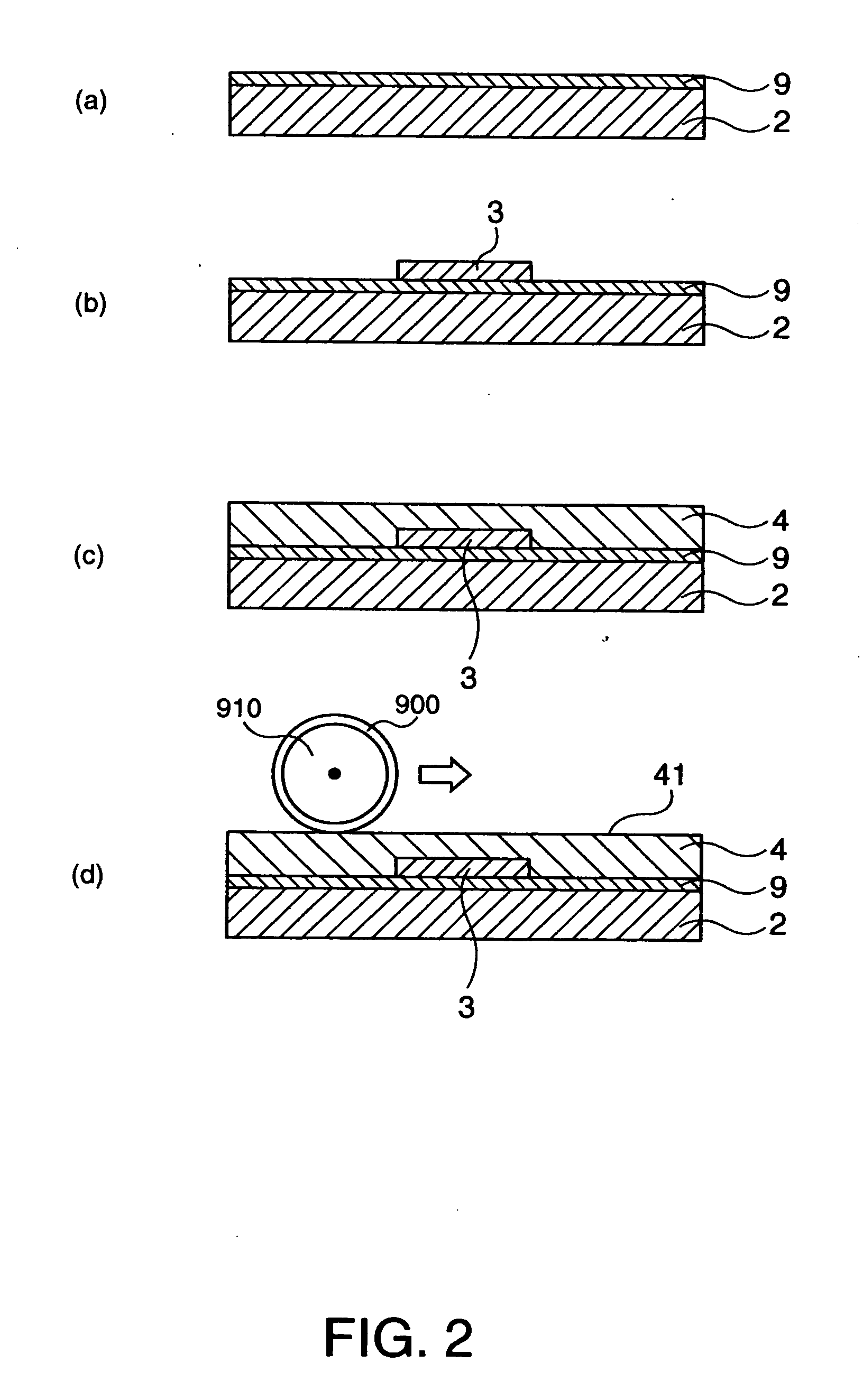

Aspects of the invention can provide a thin-film transistor having good transistor characteristics and operable with a low driving voltage, a method of producing such a thin-film transistor, a high-reliability electronic circuit, a display, and an electronic device. In an exemplary thin-film transistor according to the invention, a gate electrode can be formed on a substrate via an underlying layer, and a gate insulating layer can be formed on the substrate such that the gate electrode is covered with the gate insulating layer. A source electrode and a drain electrode are formed on the gate insulating layer such that they are separated from each other by a gap formed just above the gate electrode. An organic semiconductor layer can be formed thereon such that the electrodes are covered with the organic semiconductor layer. A region between the electrodes of the organic semiconductor layer functions as a channel region. A protective layer can be arranged on the organic semiconductor layer. This thin-film transistor is characterized in that the organic semiconductor layer is formed after the gate insulating layer is formed, and the gate insulating layer has the capability of causing the organic semiconductor layer to be aligned.

Owner:SEIKO EPSON CORP

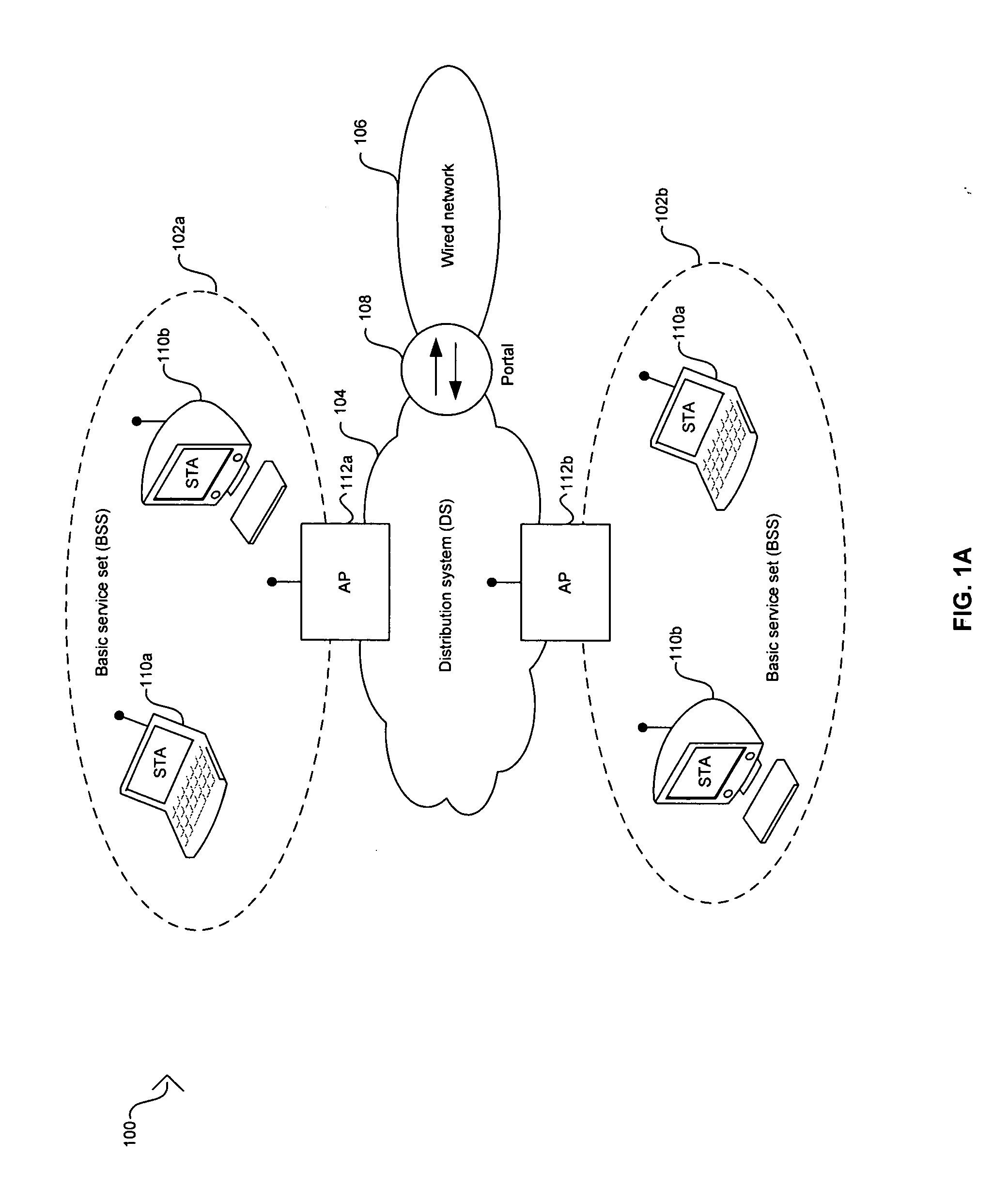

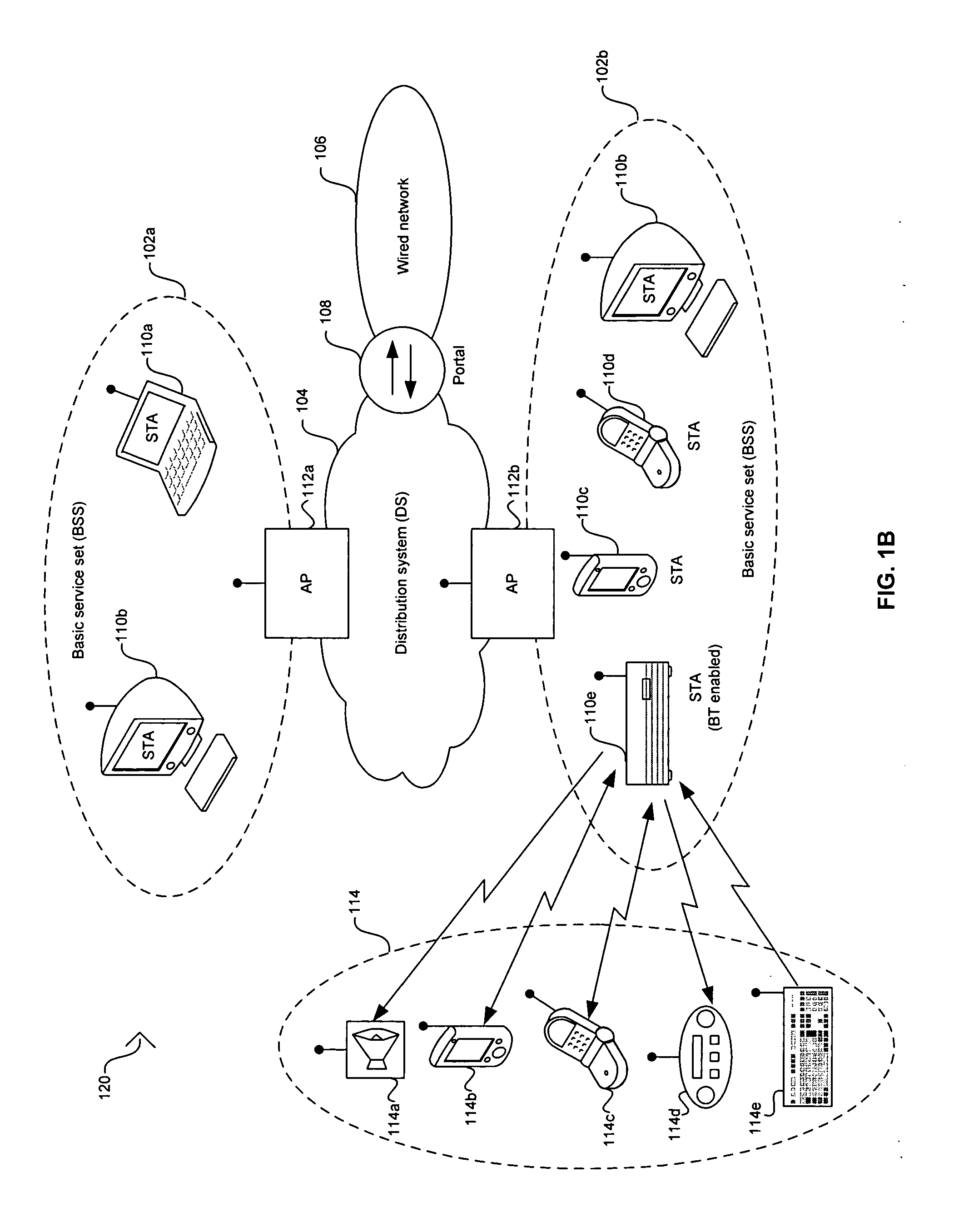

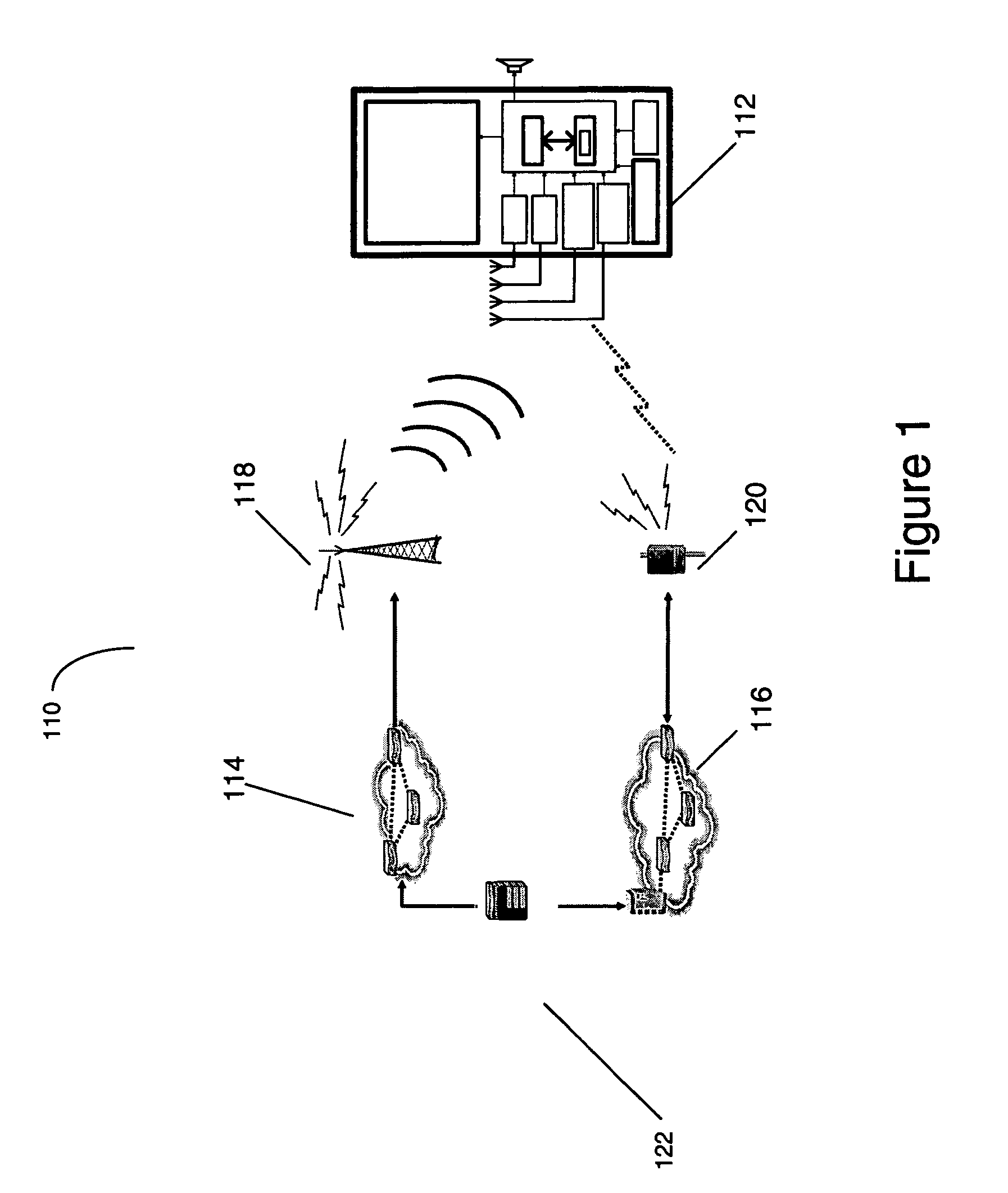

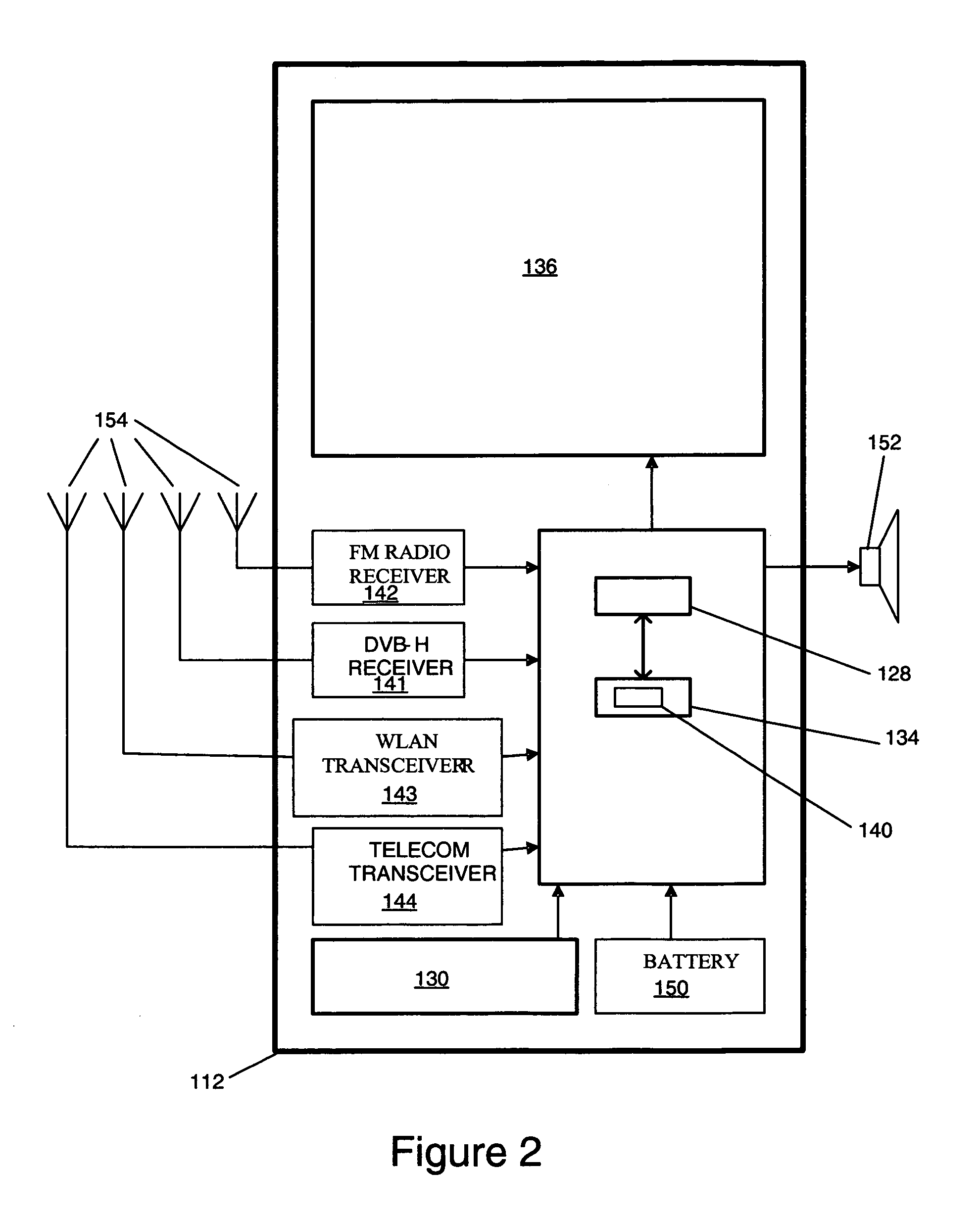

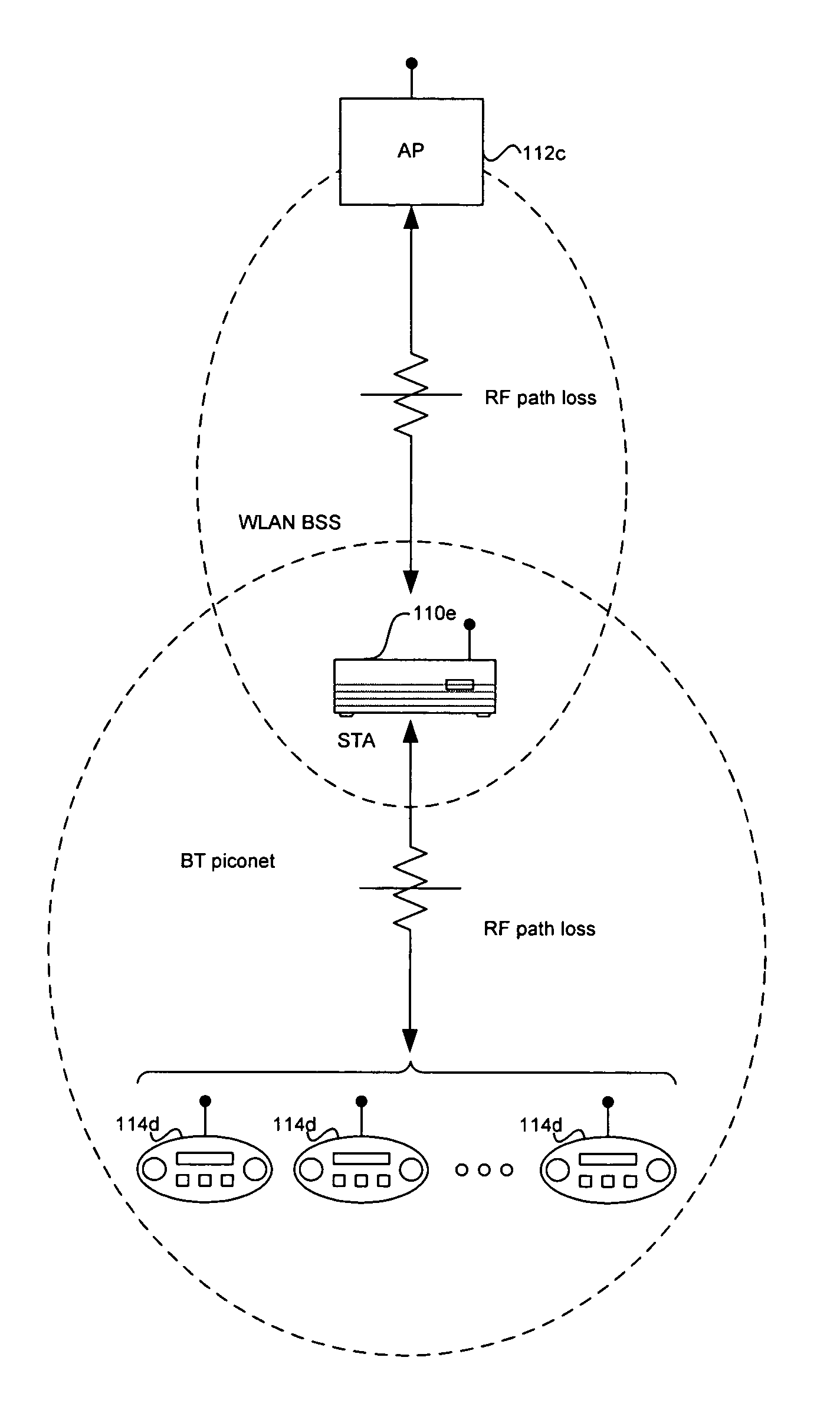

Method and system for transmit power control techniques to reduce mutual interference between coexistent wireless networks device

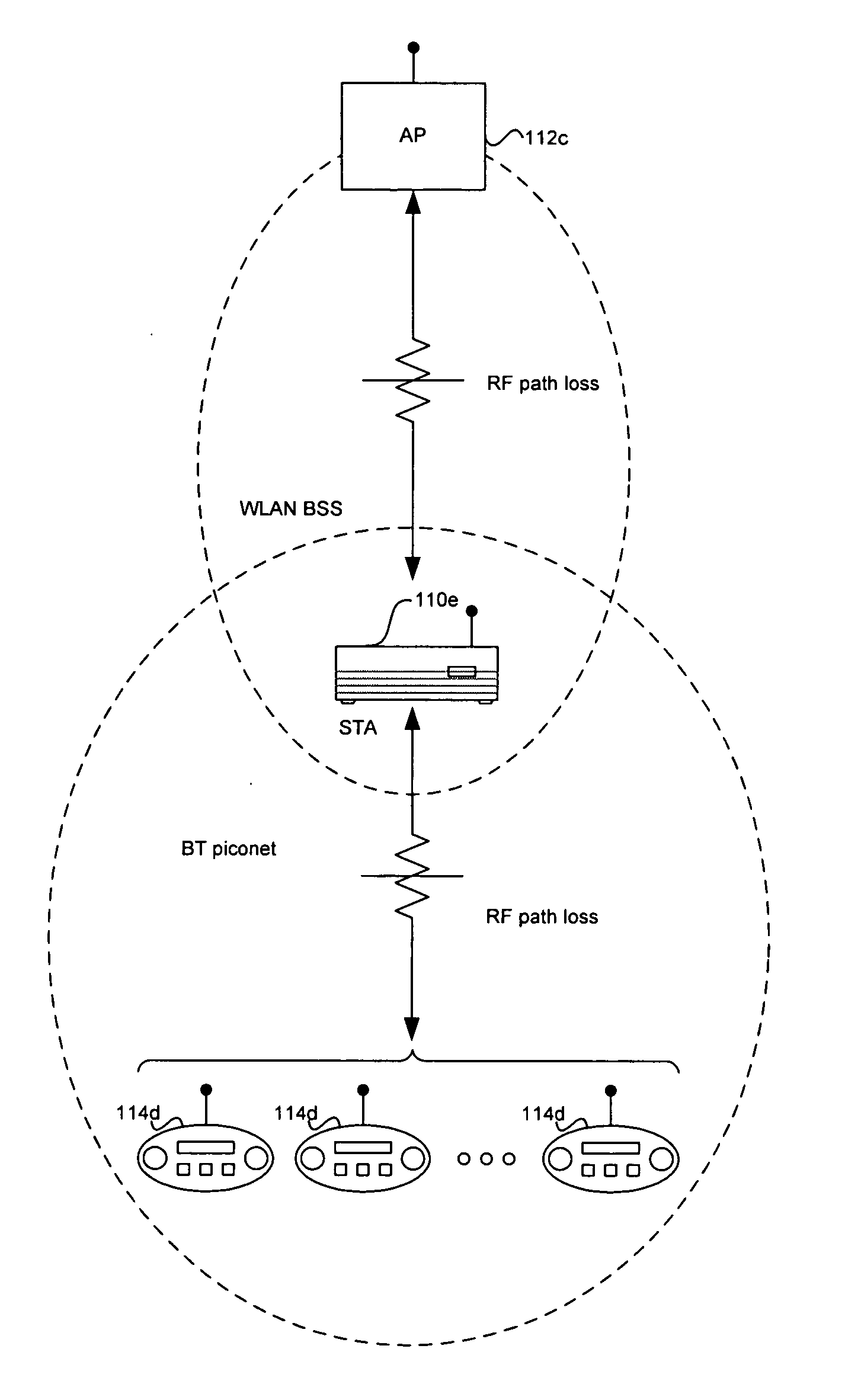

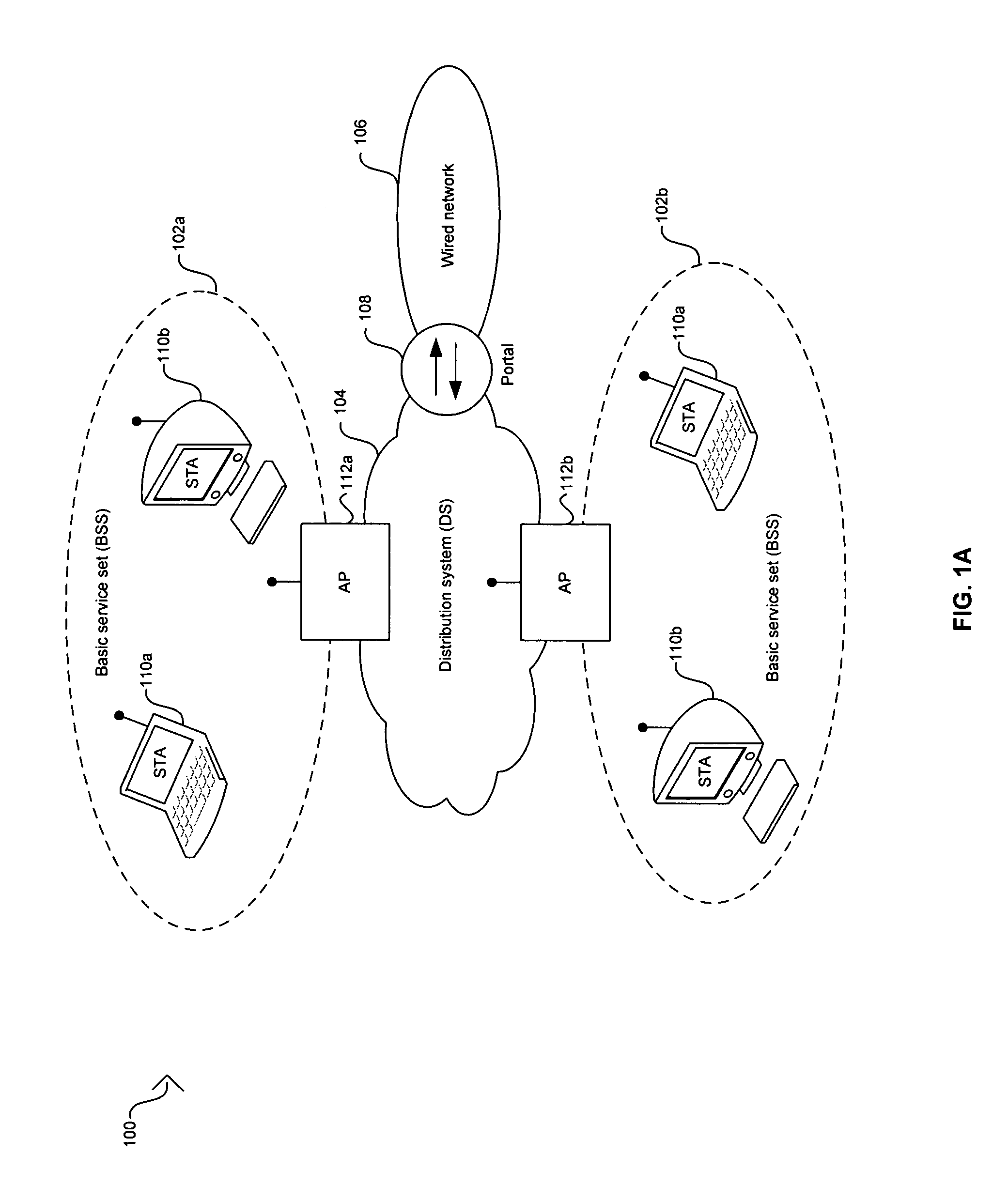

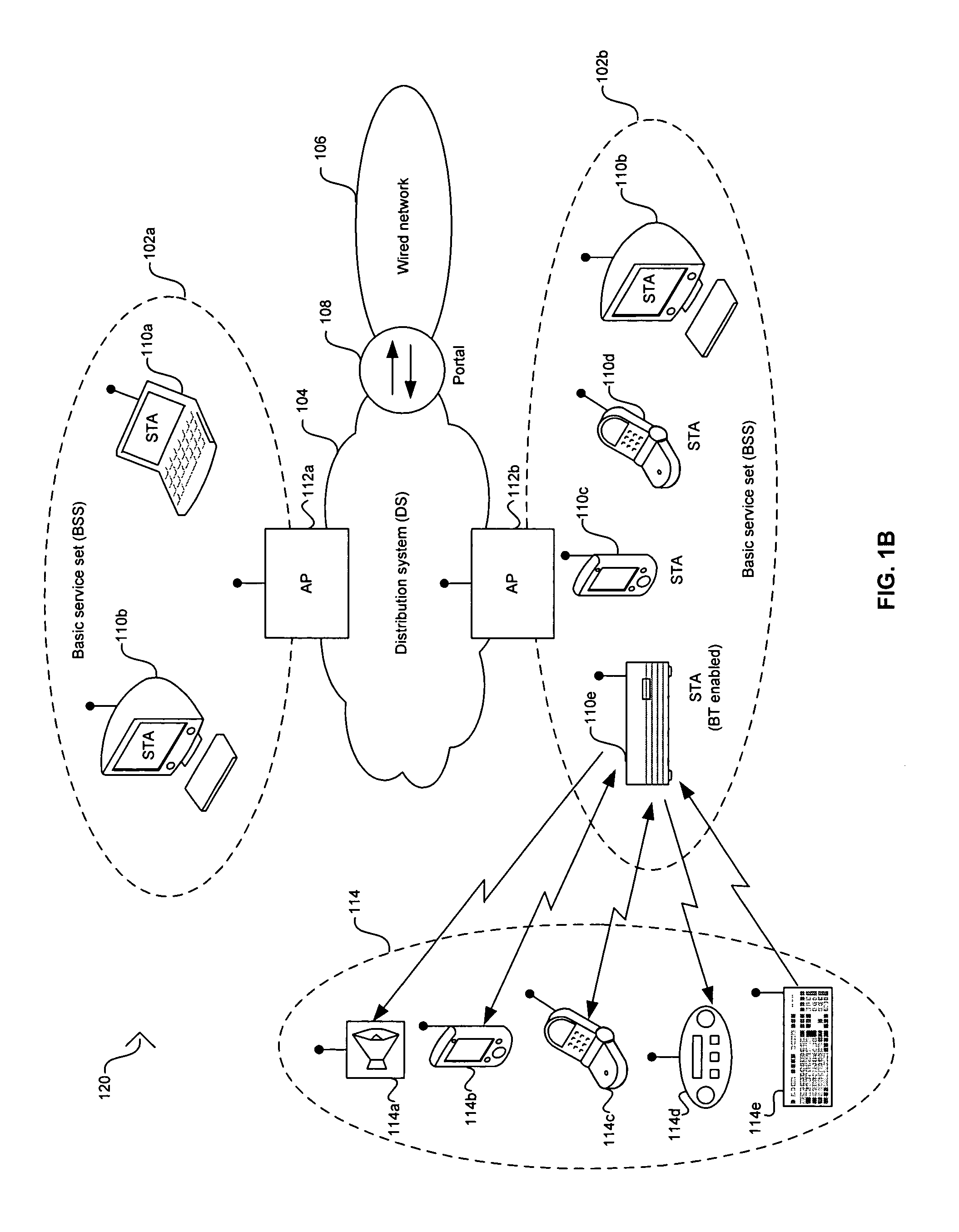

Aspects of a method and system for transmit power control techniques to reduce mutual interference between coexistent wireless networks are provided. A coexistence terminal comprising a WLAN radio and a Bluetooth radio operating as a master device may transmit signals to one or more remote controllers comprising a slave Bluetooth radio to increase transmission power when the isolation between the coexistence terminal's WLAN and Bluetooth radios is below a threshold. Link manager protocol (LMP) signals may be utilized for changing the transmission power. When the isolation increases above the threshold, signals may be generated to reduce the remote controllers' transmission power. In some instances, in addition to increasing the transmission power of remote controllers, the transmission power of the Bluetooth radio or the WLAN radio may be reduced. The reduced Bluetooth or WLAN radio transmission power may be increased when the radio isolation in the coexistence terminal increases.

Owner:AVAGO TECH INT SALES PTE LTD

Thin-film transistor, method of producing thin-film transistor, electronic circuit, display, and electronic device

InactiveUS20070099333A1Improve transistor characteristicsReduce the driving voltageTransistorSolid-state devicesDisplay deviceEngineering

Aspects of the invention can provide a thin-film transistor having good transistor characteristics and operable with a low driving voltage, a method of producing such a thin-film transistor, a high-reliability electronic circuit, a display, and an electronic device. In an exemplary thin-film transistor according to the invention, a gate electrode can be formed on a substrate via an underlying layer, and a gate insulating layer can be formed on the substrate such that the gate electrode is covered with the gate insulating layer. A source electrode and a drain electrode are formed on the gate insulating layer such that they are separated from each other by a gap formed just above the gate electrode. An organic semiconductor layer can be formed thereon such that the electrodes are covered with the organic semiconductor layer. A region between the electrodes of the organic semiconductor layer functions as a channel region. A protective layer can be arranged on the organic semiconductor layer. This thin-film transistor is characterized in that the organic semiconductor layer is formed after the gate insulating layer is formed, and the gate insulating layer has the capability of causing the organic semiconductor layer to be aligned.

Owner:SEIKO EPSON CORP

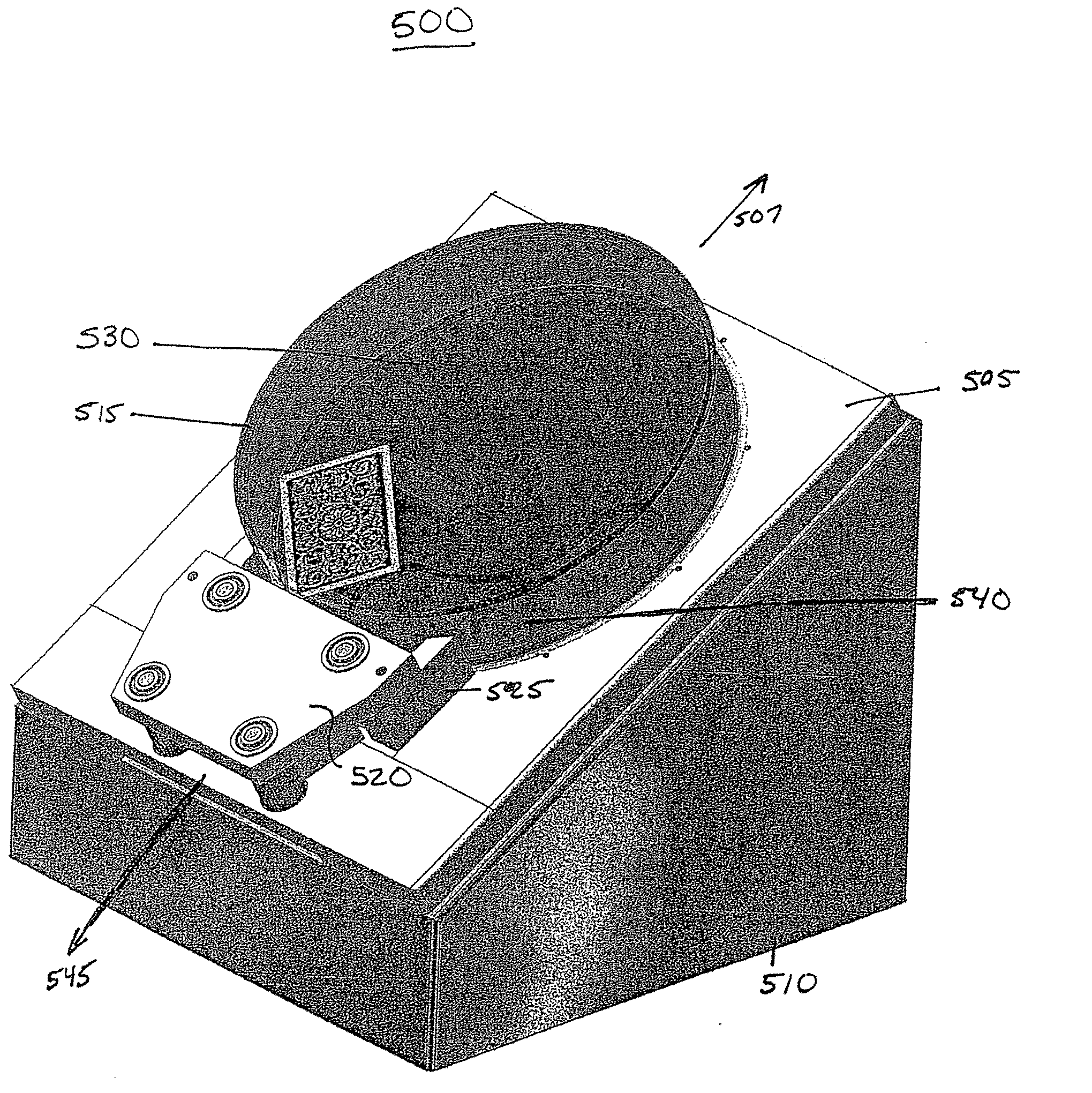

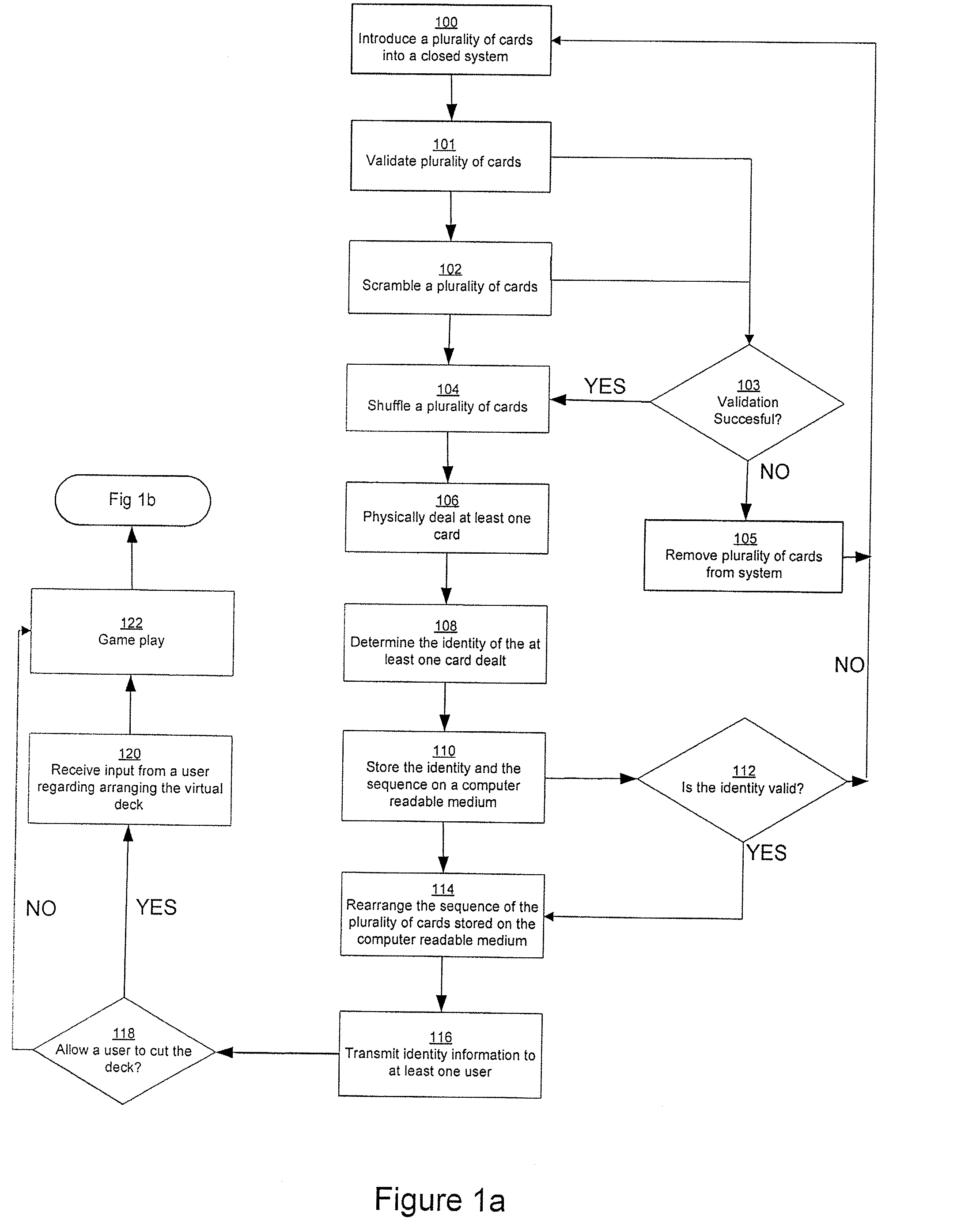

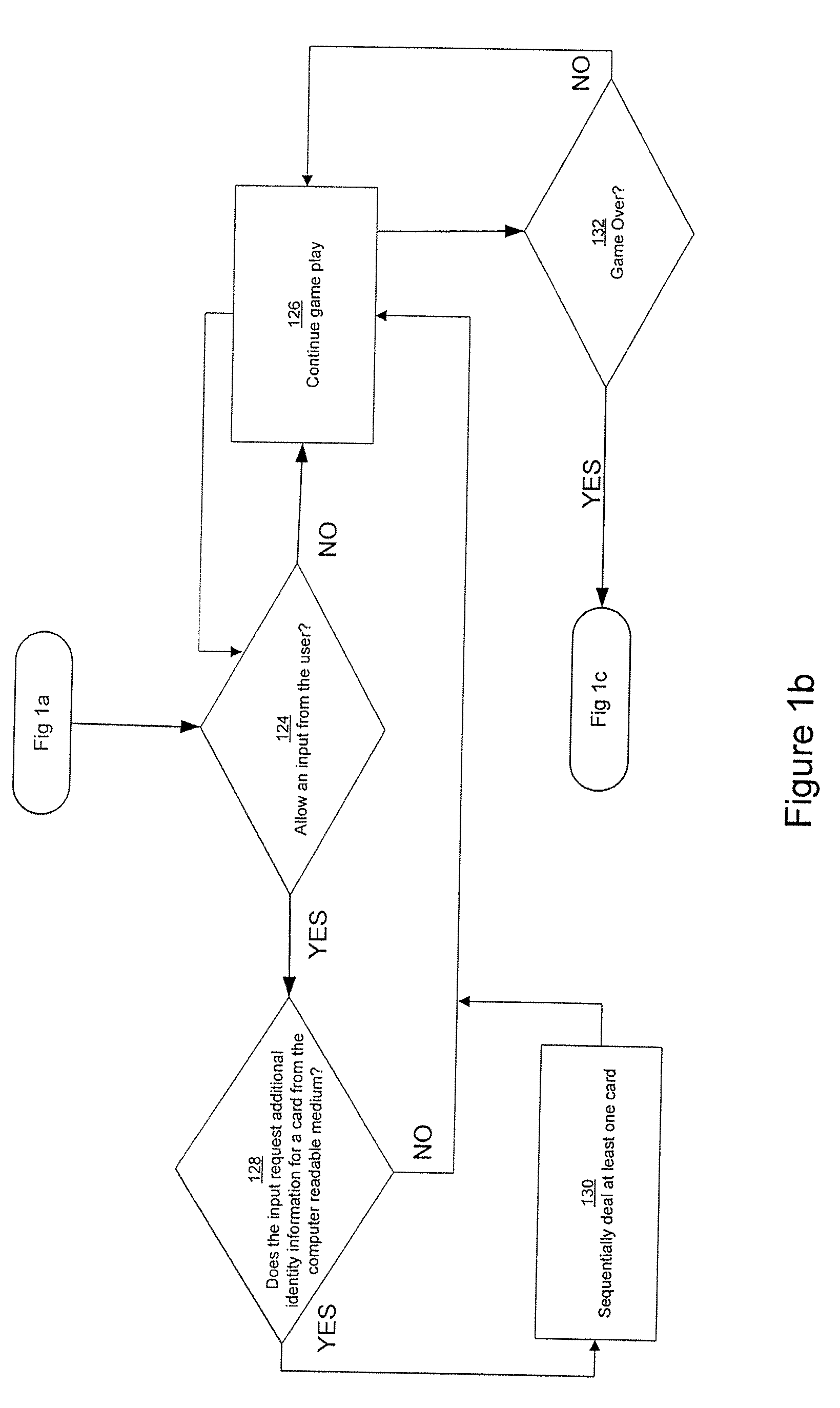

Card scrambling device

InactiveUS20070001395A1Card gamesApparatus for meter-controlled dispensingComputer hardwarePlaying card

Aspects of the invention relate to fully automated systems and methods for shuffling and scrambling playing instruments, such as cards, before being dealt to one or more players. In one embodiment, a rotating device is utilized to scramble playing instruments. In yet a further embodiment, the rotating device is coupled with air, vacuum, or combinations thereof to further scramble the cards. The scrambling device may be coupled to an aligning device for realigning the playing instruments upon being adequately shuffled. According to another aspect of the invention, physical cards are utilized in a gaming environment that may be scrambled, shuffled, and / or played remotely over a network. In one embodiment, the physical cards are traditional poker-style gaming cards. The cards include at least one identifier that may be read upon the card being dealt. The identifier may contain information that is remotely communicated to a player.

Owner:MGT INTERACTIVE

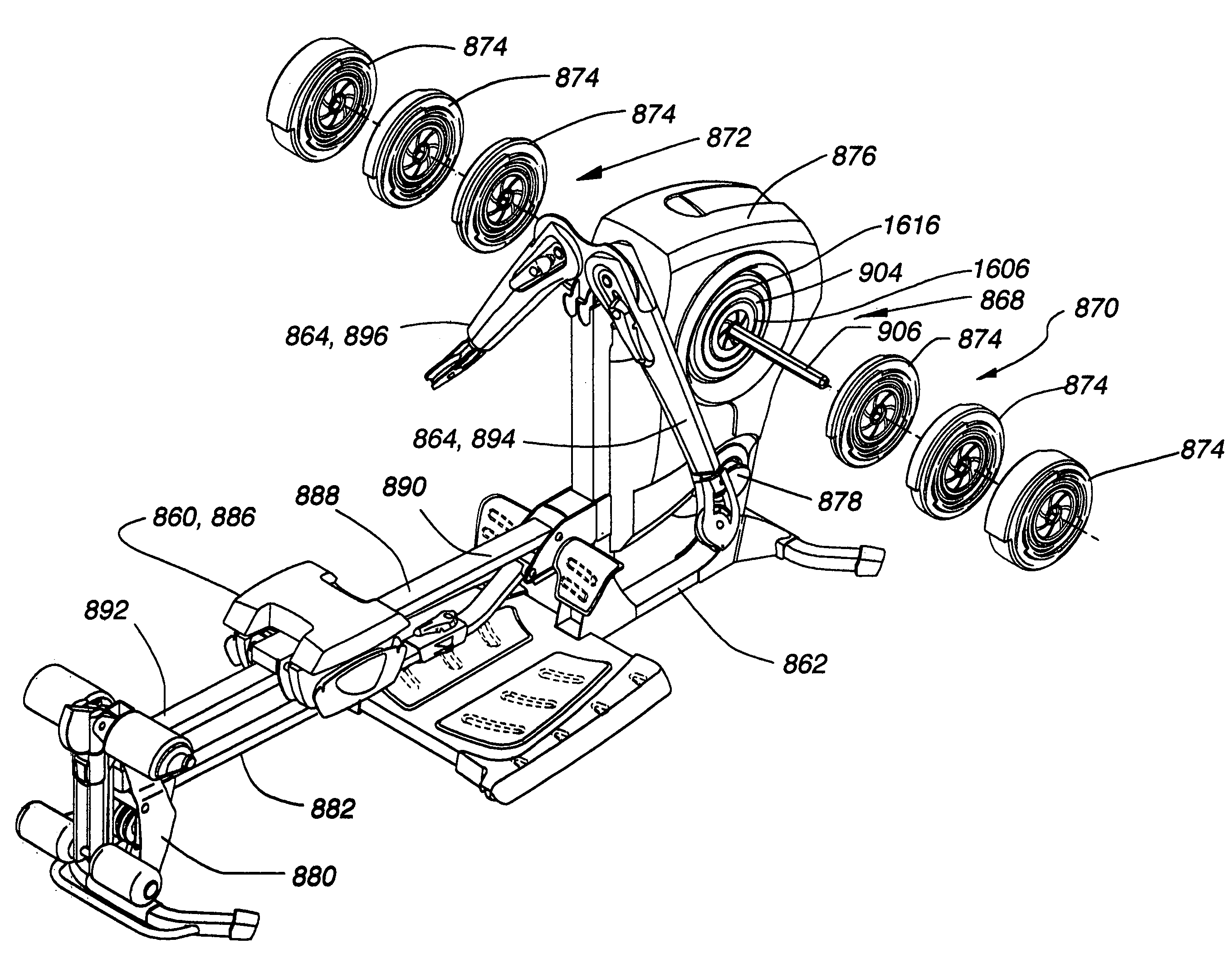

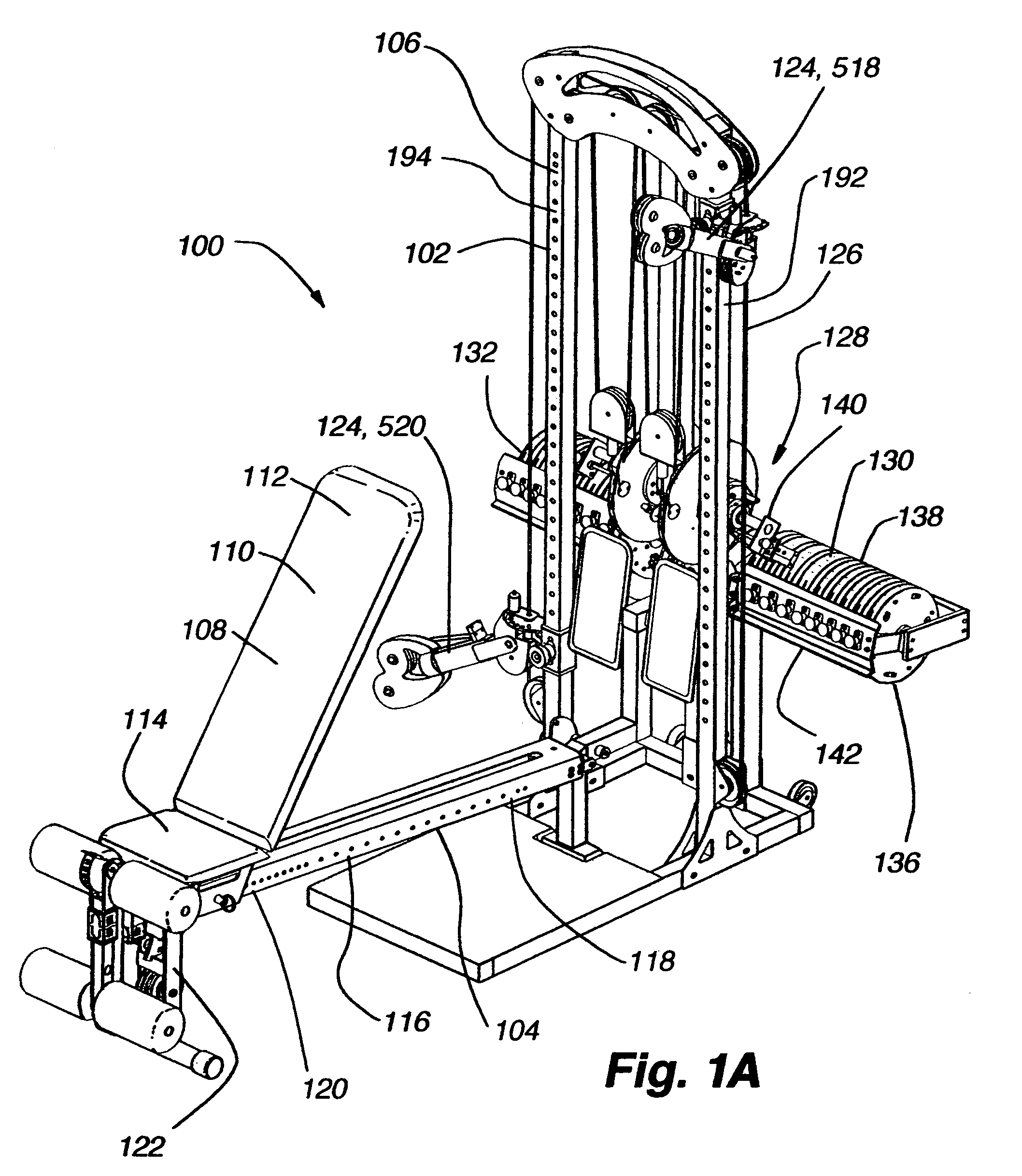

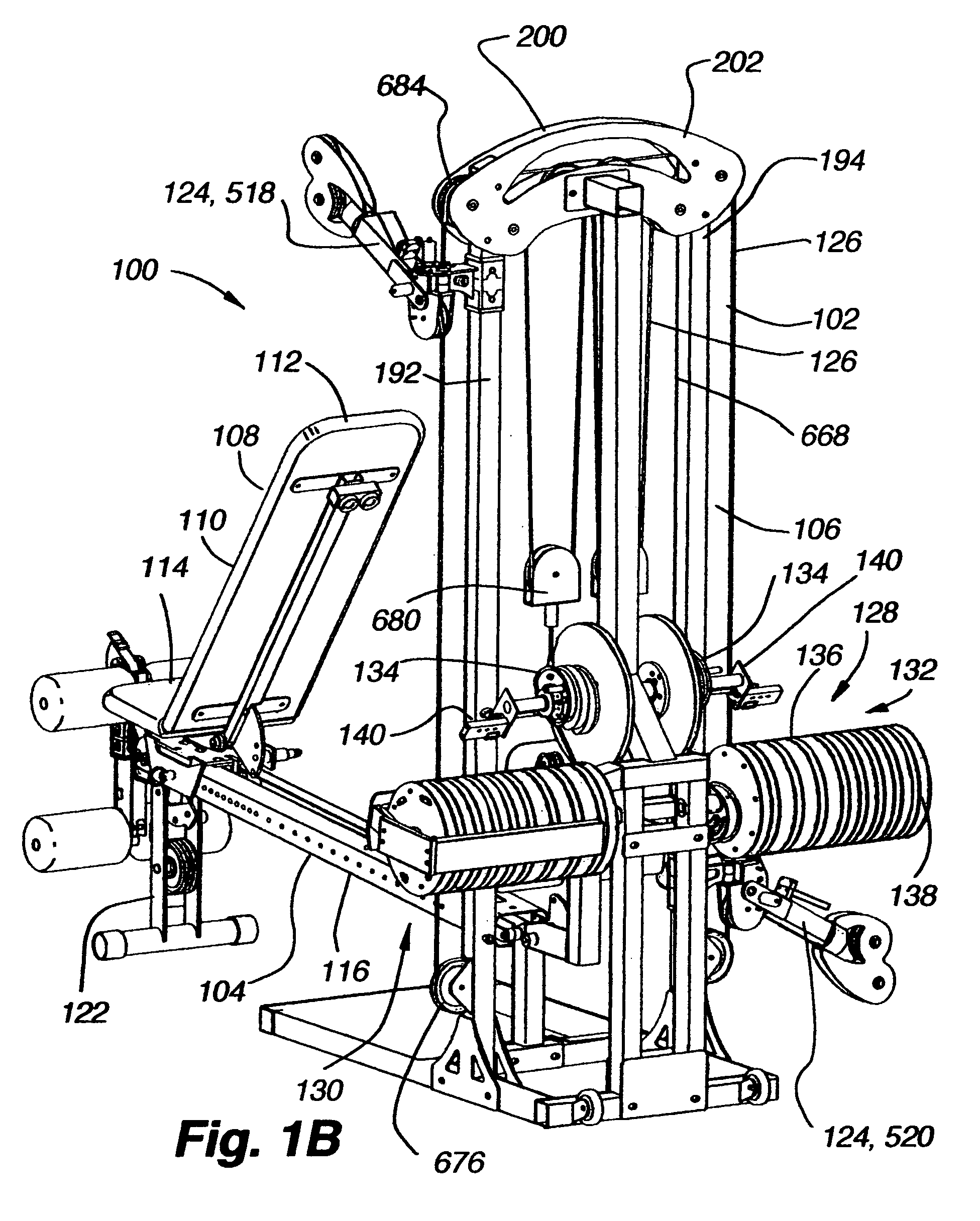

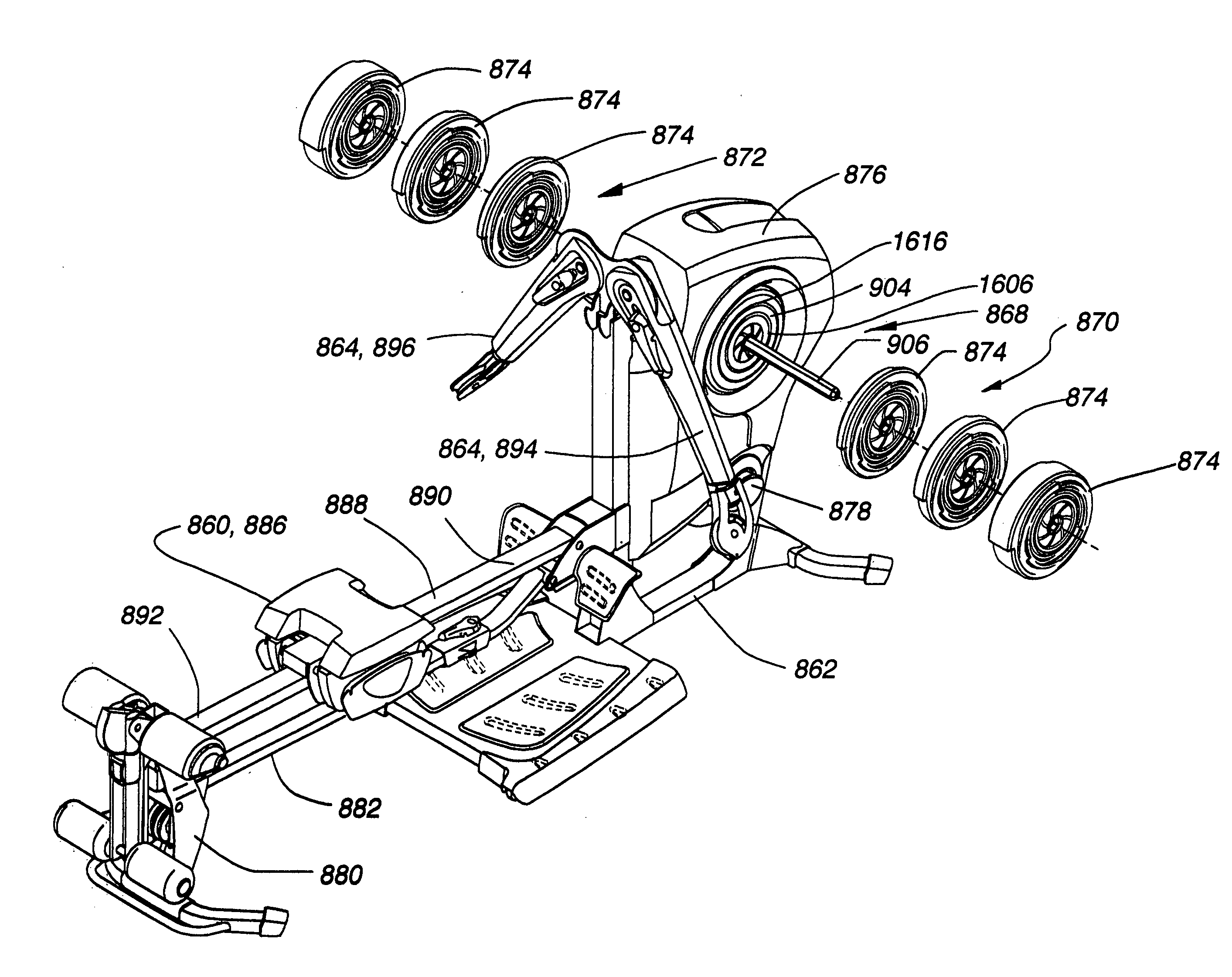

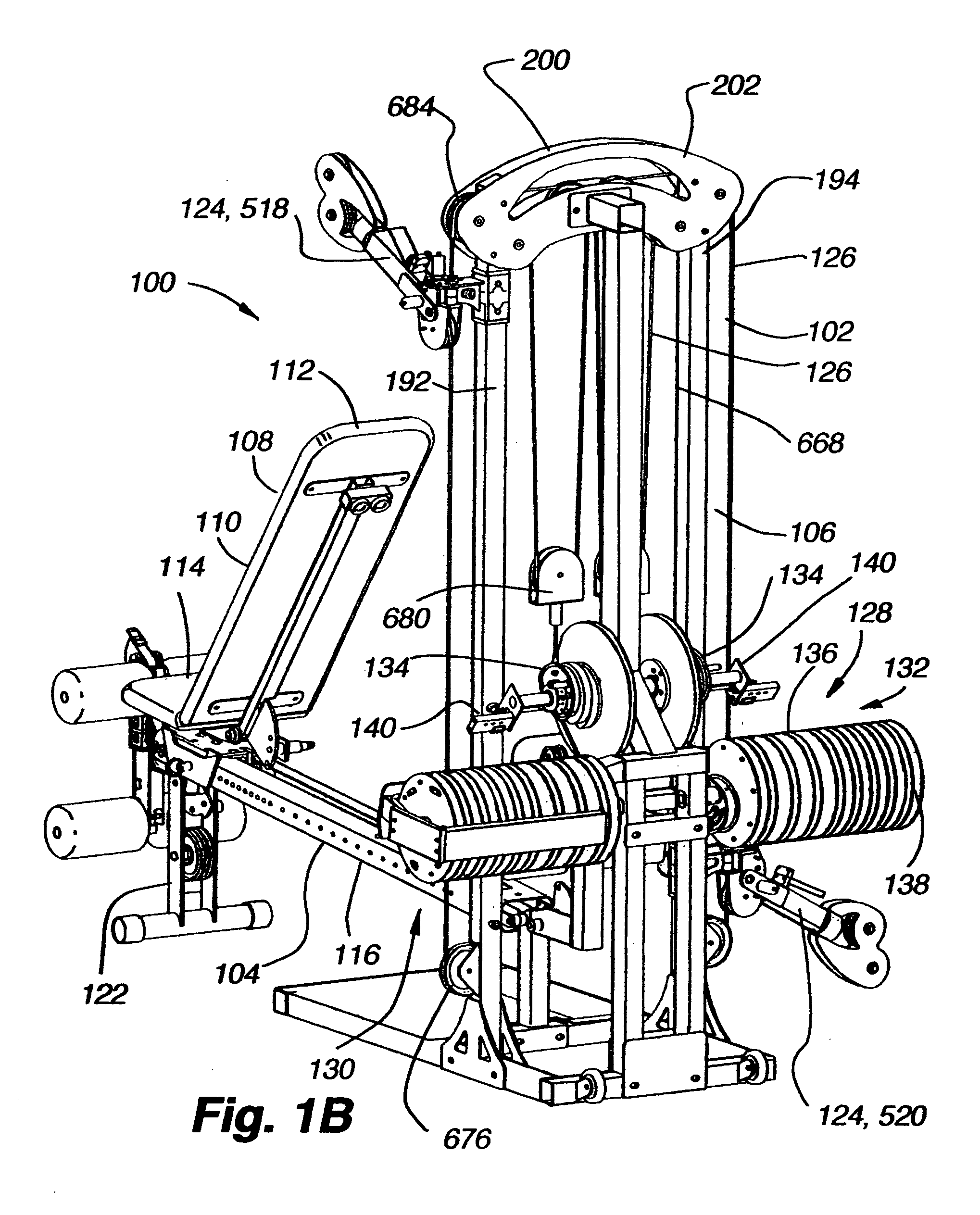

Exercise device

ActiveUS20060100069A1Conveniently engagedTherapy exerciseMuscle exercising devicesEngineeringBody size

Aspects of the present invention involve an exercise device configurable to allow a user to perform various exercises. The exercise devices include an adjustable bench assembly connected with a frame supporting adjustable arm and cable-pulley assemblies providing a user interface with a resistance system. In some embodiments of the invention, the adjustable bench assembly includes a bench seat and a pivotal back support supported on an adjustable bench frame. The exercise devices also utilize various configurations of adjustable arm assemblies that are selectively positionable for numerous exercises and to suit a user's particular body size and shape. Other embodiments of the exercise devices include a resistance system with a transmission supporting a plurality of resistance packs. The transmission allows a user to conveniently engage any number of resistance packs to change the resistance level for a particular exercise.

Owner:NAUTILUS INC

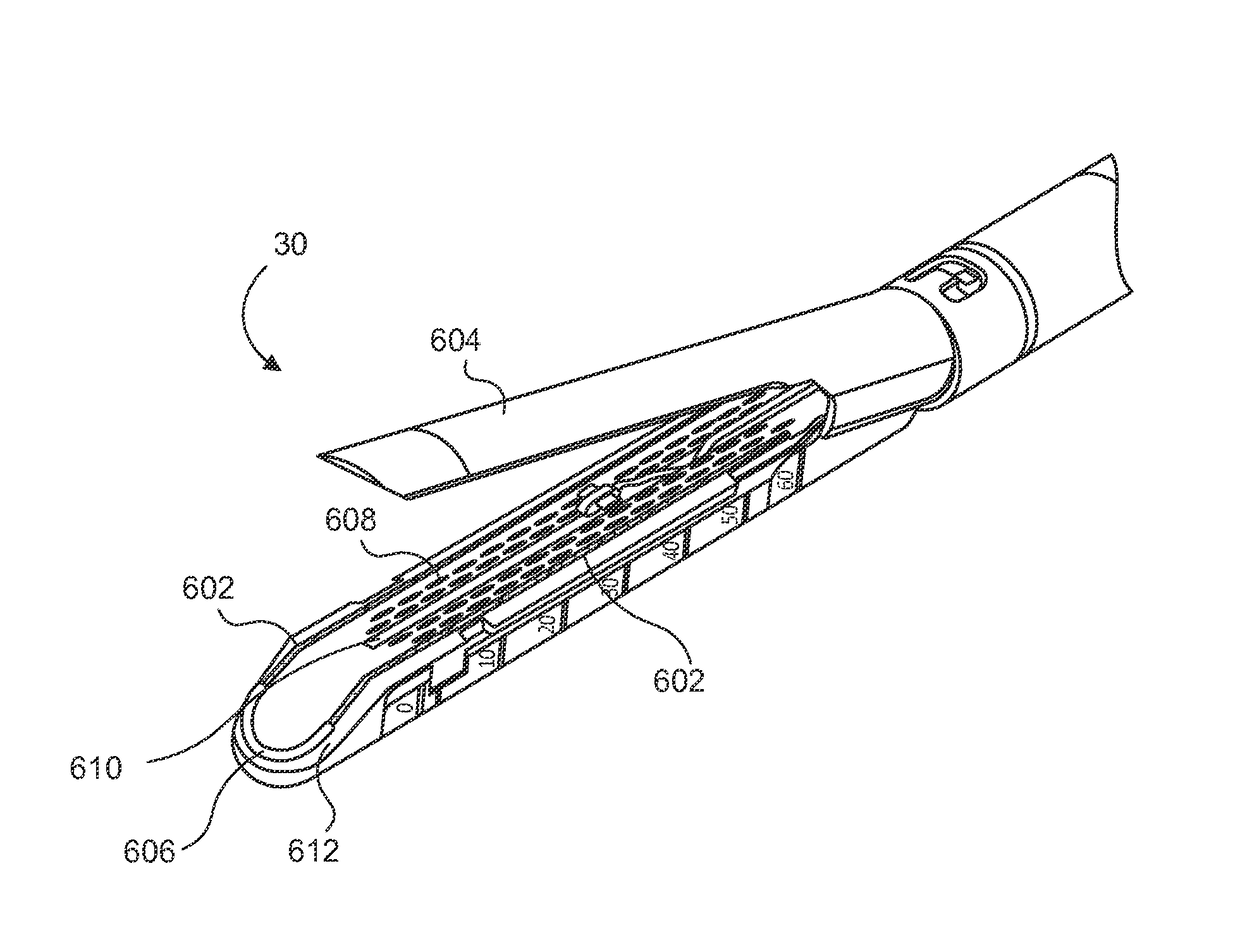

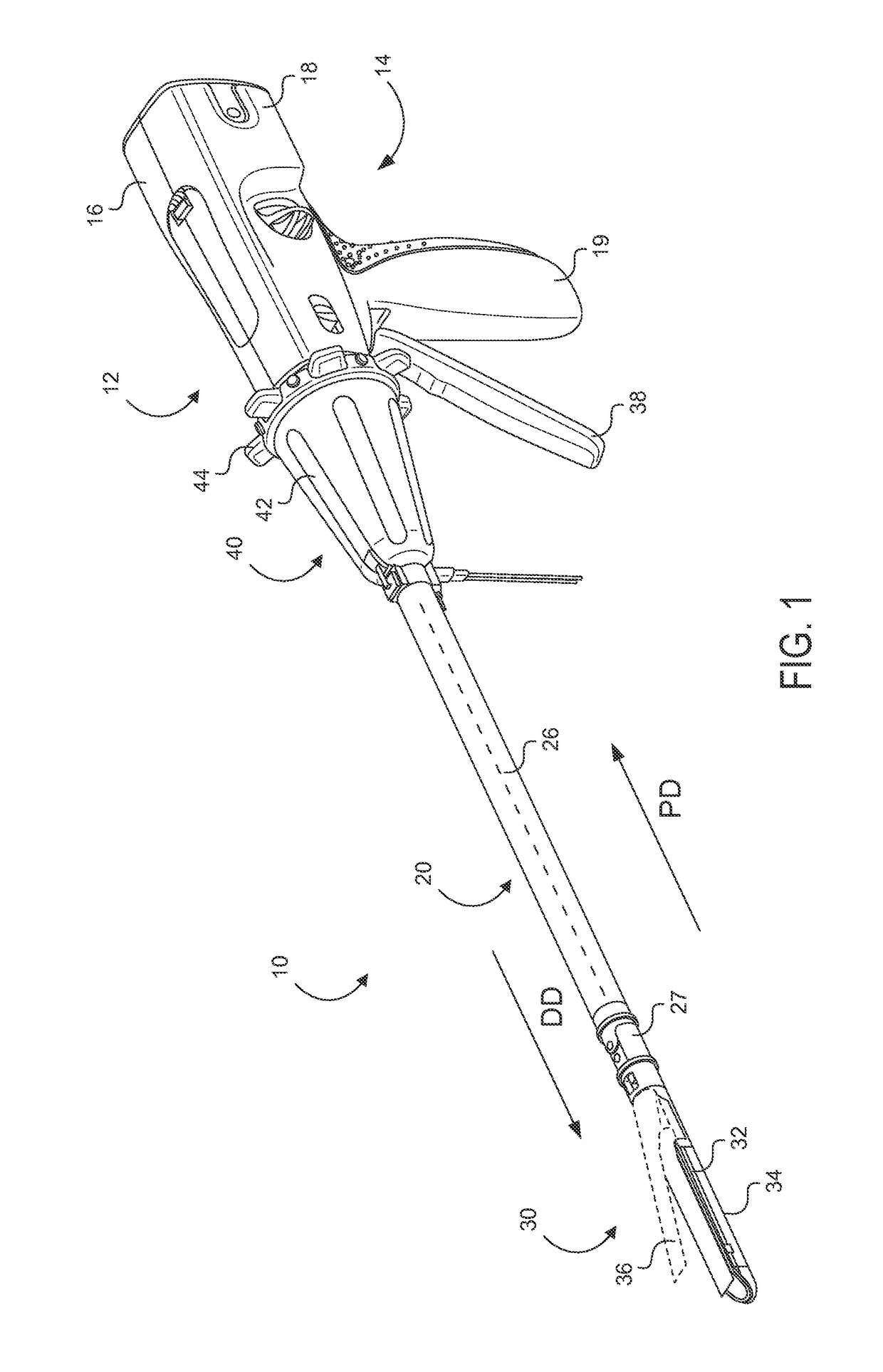

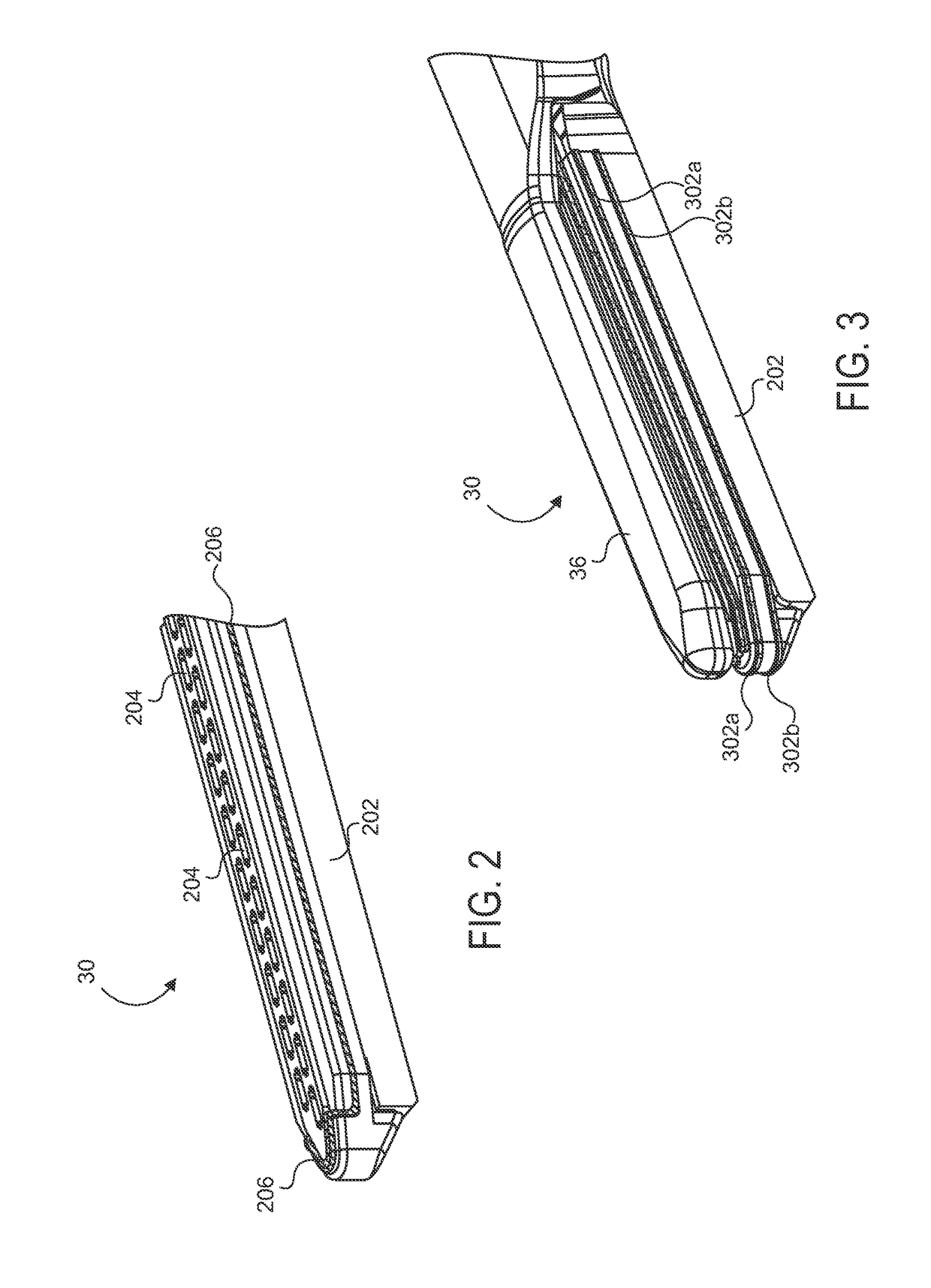

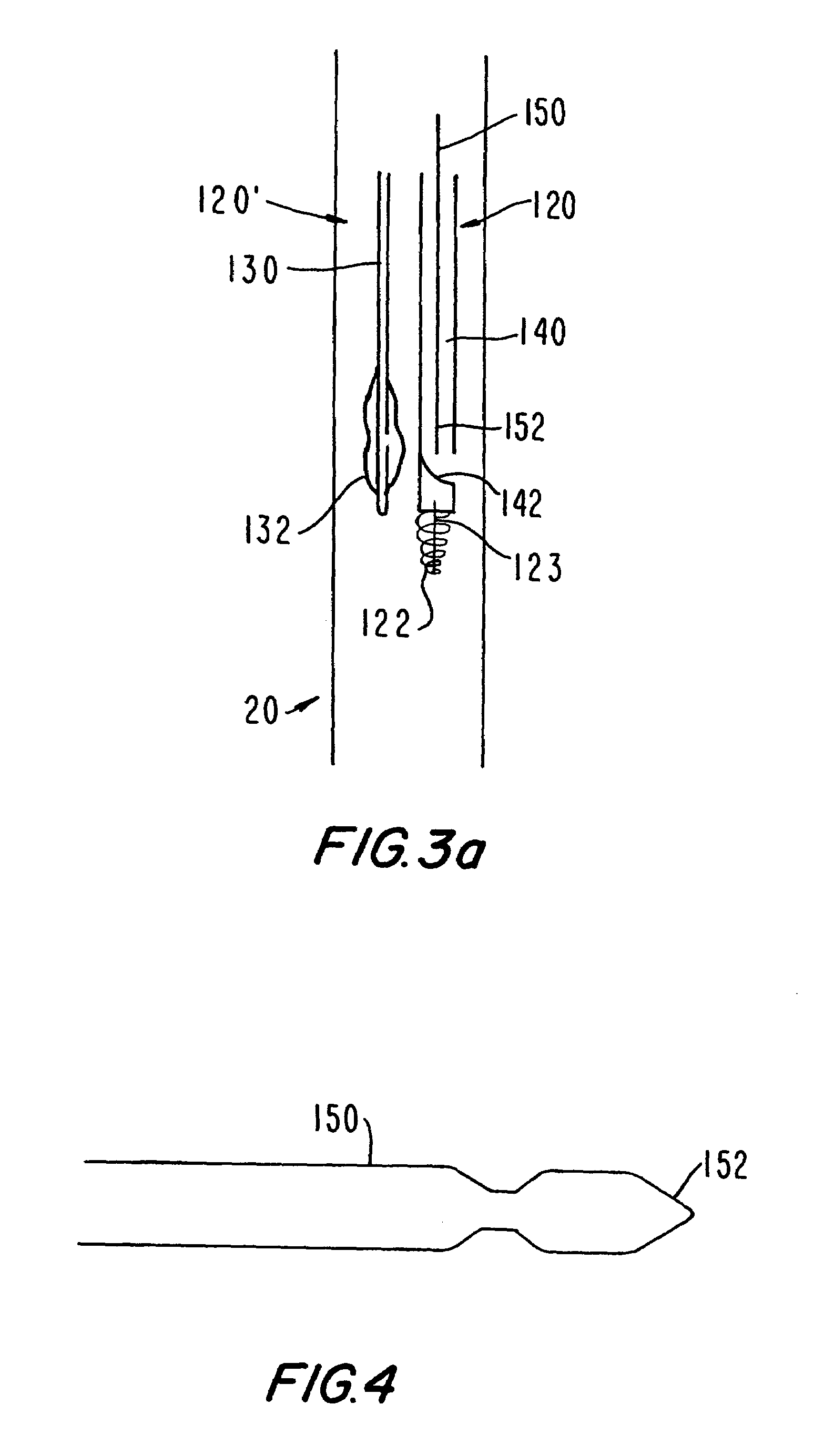

Control and electrical connections for electrode endocutter device

Aspects of the present disclosure include an attachable power and control system to supply energy to electrodes of a wiping electrode coagulation system of a surgical device. A surgical device includes electrodes at an end of effector to aide in sealing during various surgical procedures. During the procedure, the surgeon may wipe the surgical site with the end effector, causing the electrodes to touch the fractured area. Electrosurgical energy may be applied to the electrodes during the wiping, causing coagulation of smaller vessels. The attachable power and control system may be configured to slide over the shaft of the surgical device. The power and control system also may be configured to supply power to the electrodes and to control when energy is applied to the electrodes, based in part, for example, on measuring a distance or angle of the opening of the jaws at the end effector.

Owner:CILAG GMBH INT

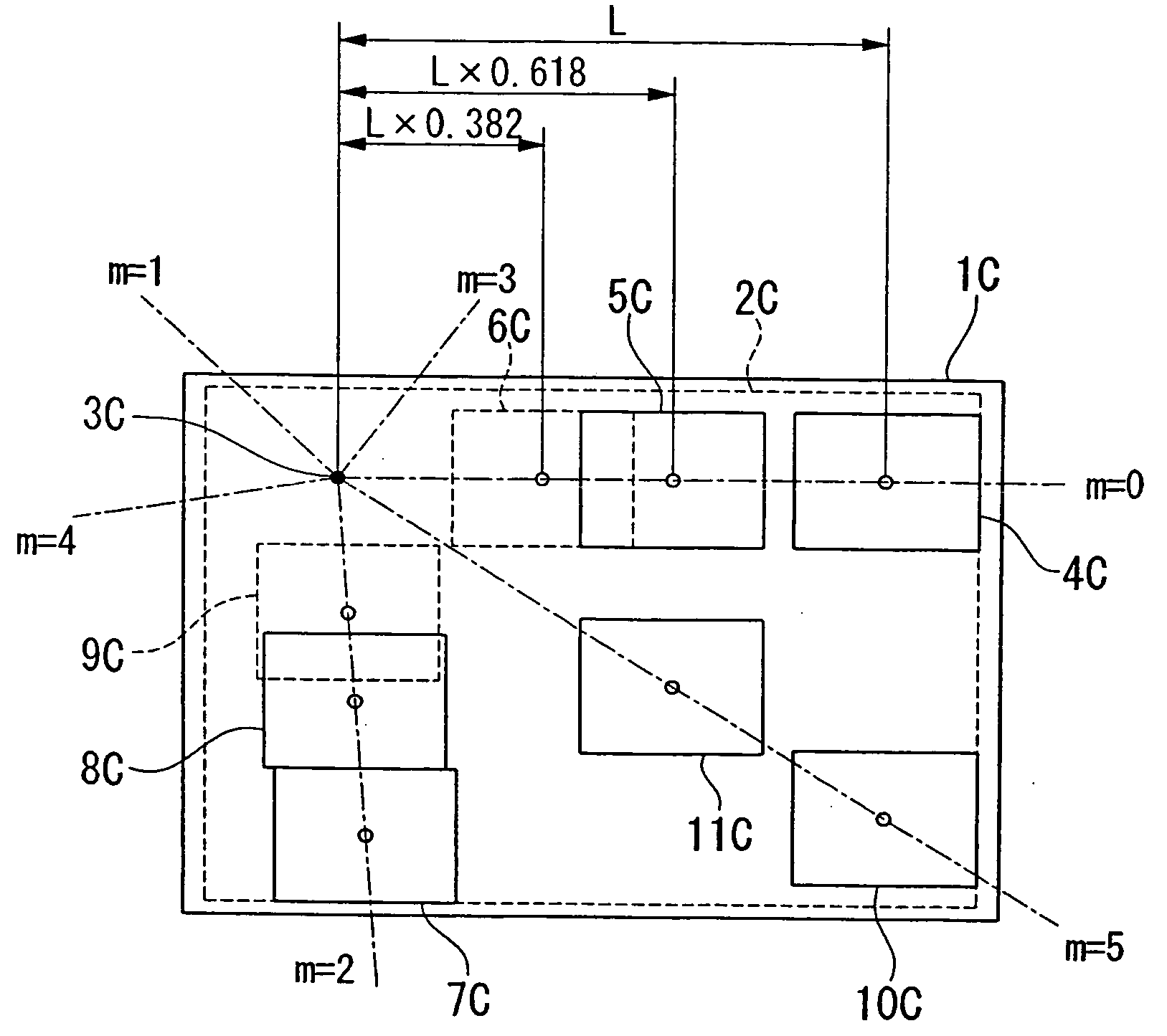

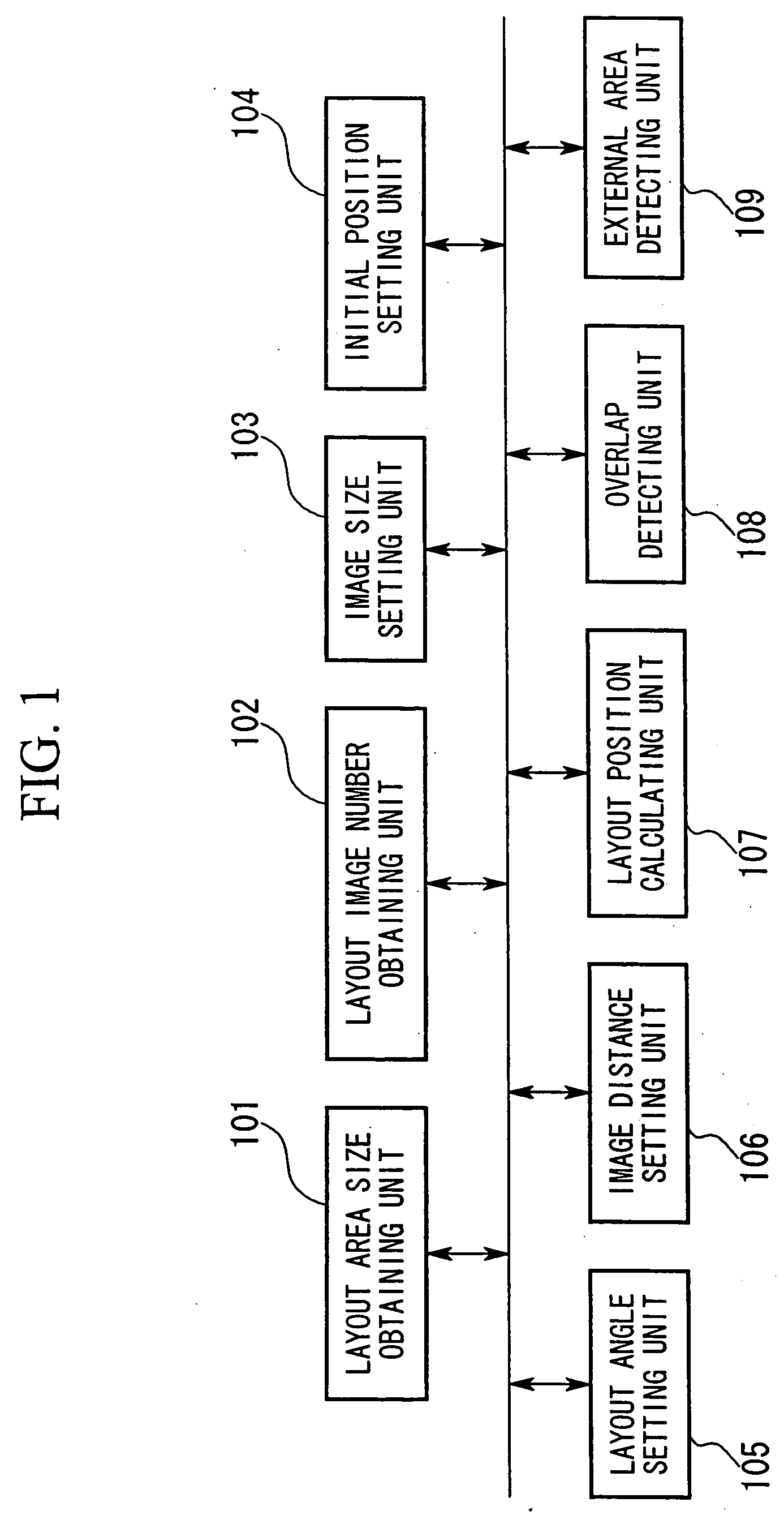

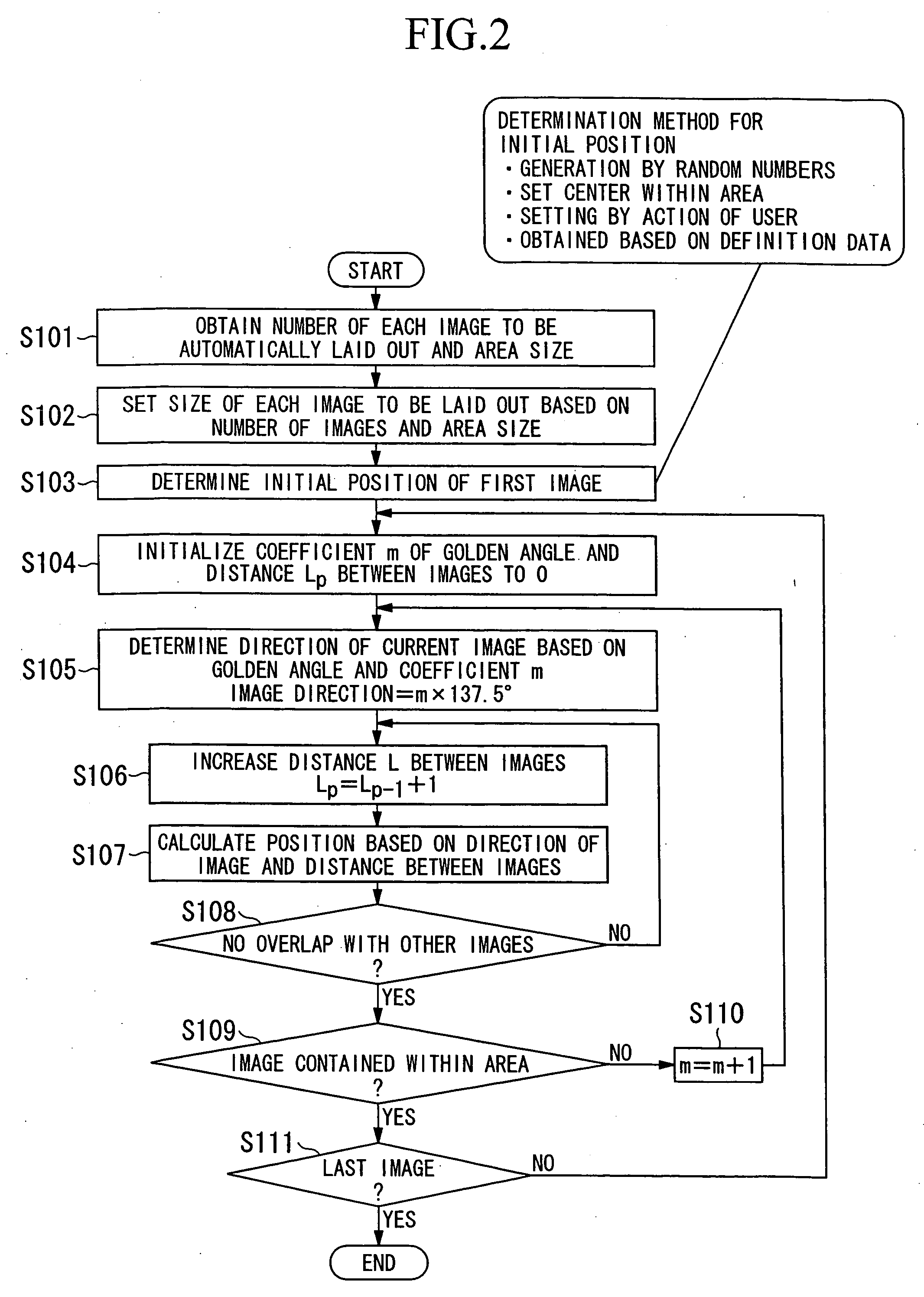

Image layout device

InactiveUS20050091599A1Simple calculationImprove efficiencyCharacter and pattern recognitionCathode-ray tube indicatorsComputer graphics (images)Golden angle

Aspects of the invention can relate to an image layout device and an image layout method. The image layout device of the invention can be a device that automatically arranges a plurality of images within a particular area, and can include a layout angle determining device that determines the layout angle for each of the images based on an angle that is an integer multiple of a golden angle, and a layout position determining device that determines the layout position for each of the images depending on the overlap between each of the images due to the angle determined by the layout angle determining device.

Owner:SEIKO EPSON CORP

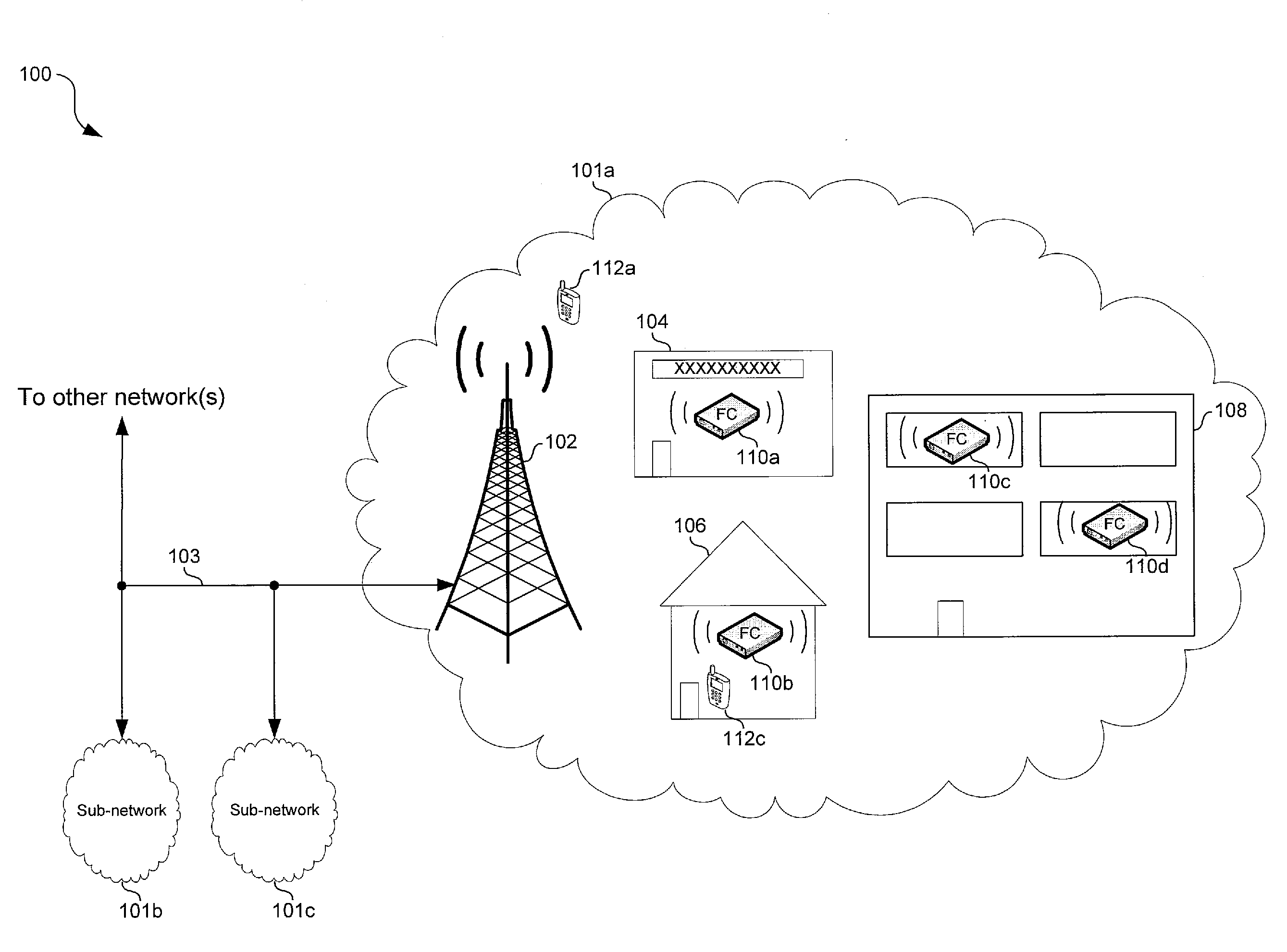

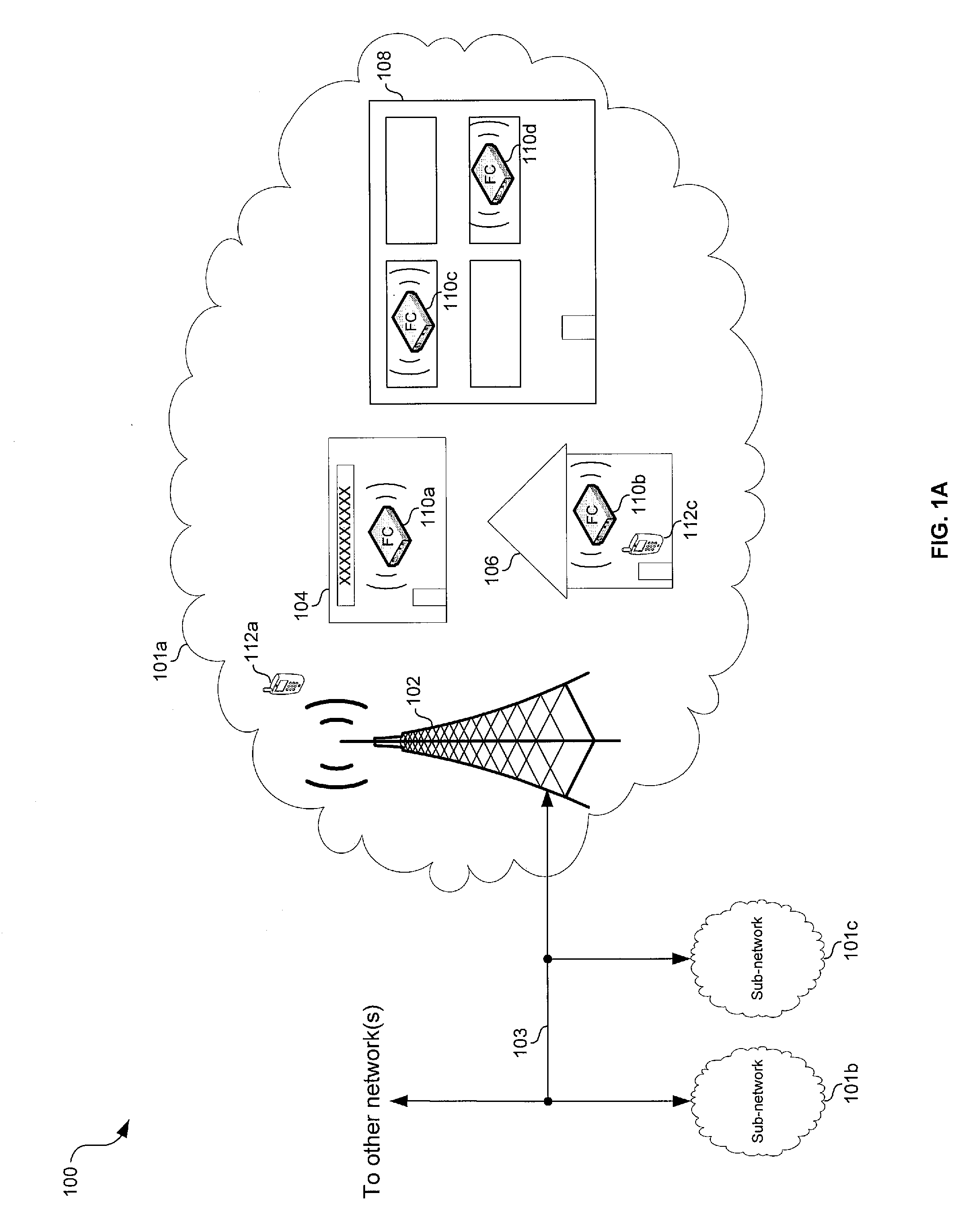

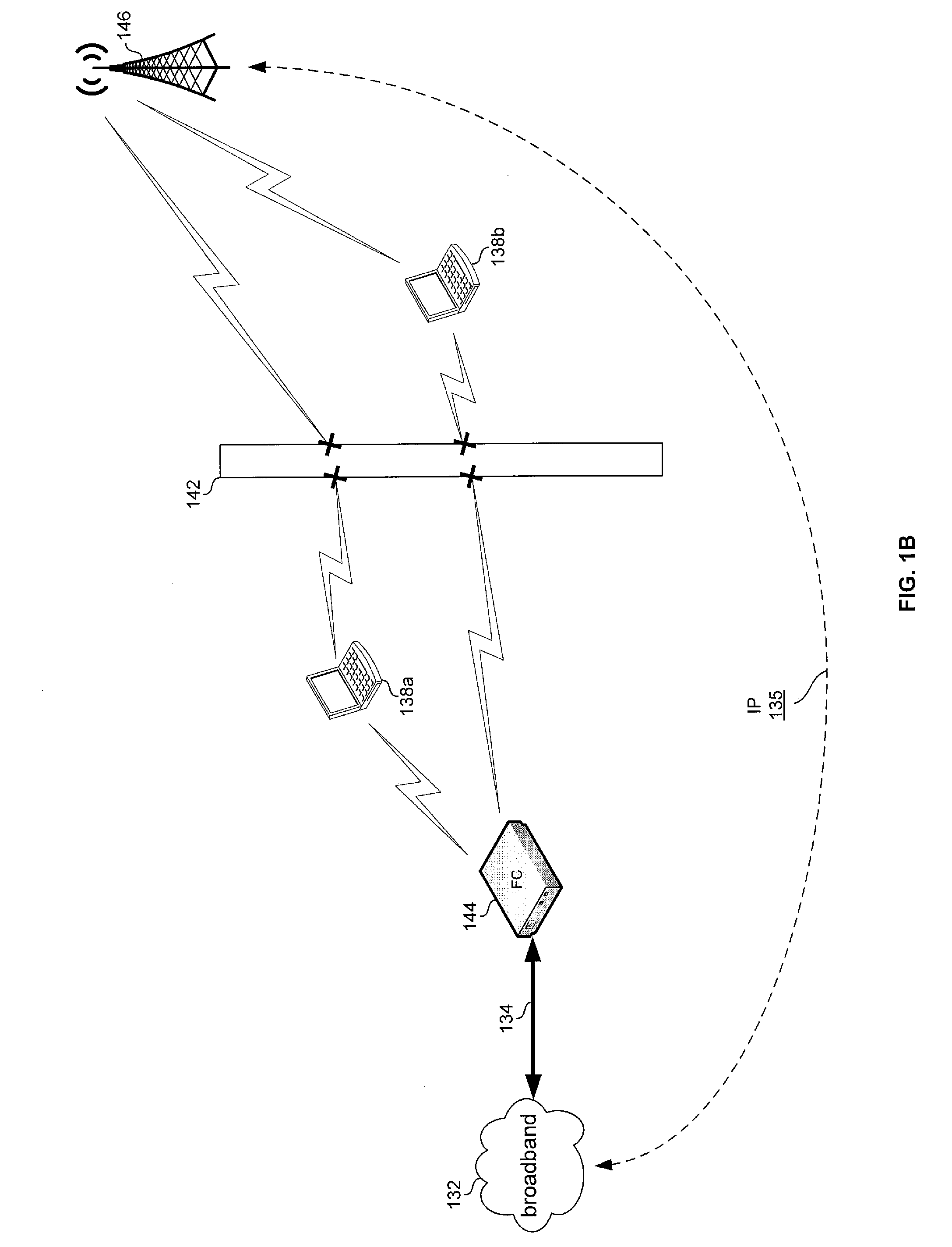

Method and system for controlling data distribution via cellular communications utilizing an integrated femtocell and set-top-box device

ActiveUS20100184411A1Network topologiesSpecial service for subscribersControl dataCommunication control

Aspects of a method and system for controlling data distribution via cellular communications with an integrated femtocell and set-top-box (IFSTB) device are provided. In this regard, a cellular enabled communication device may detect when it is within cellular communication range of a femtocell. Upon detection of the femtocell, the cellular enabled communication device may communicate instructions to a content source instructing the content source to deliver multimedia content to the femtocell. In instances that multimedia content is already being delivered to the cellular enabled communication device prior to the detection, the instructions from the cellular enabled communication device may instruct the content source to redirect the multimedia content to the femtocell. In this regard, the multimedia content may be delivered from the content source to the cellular enabled communication device via the femtocell. The femtocell may deliver at least a portion of the multimedia content to other communication devices.

Owner:AVAGO TECH INT SALES PTE LTD

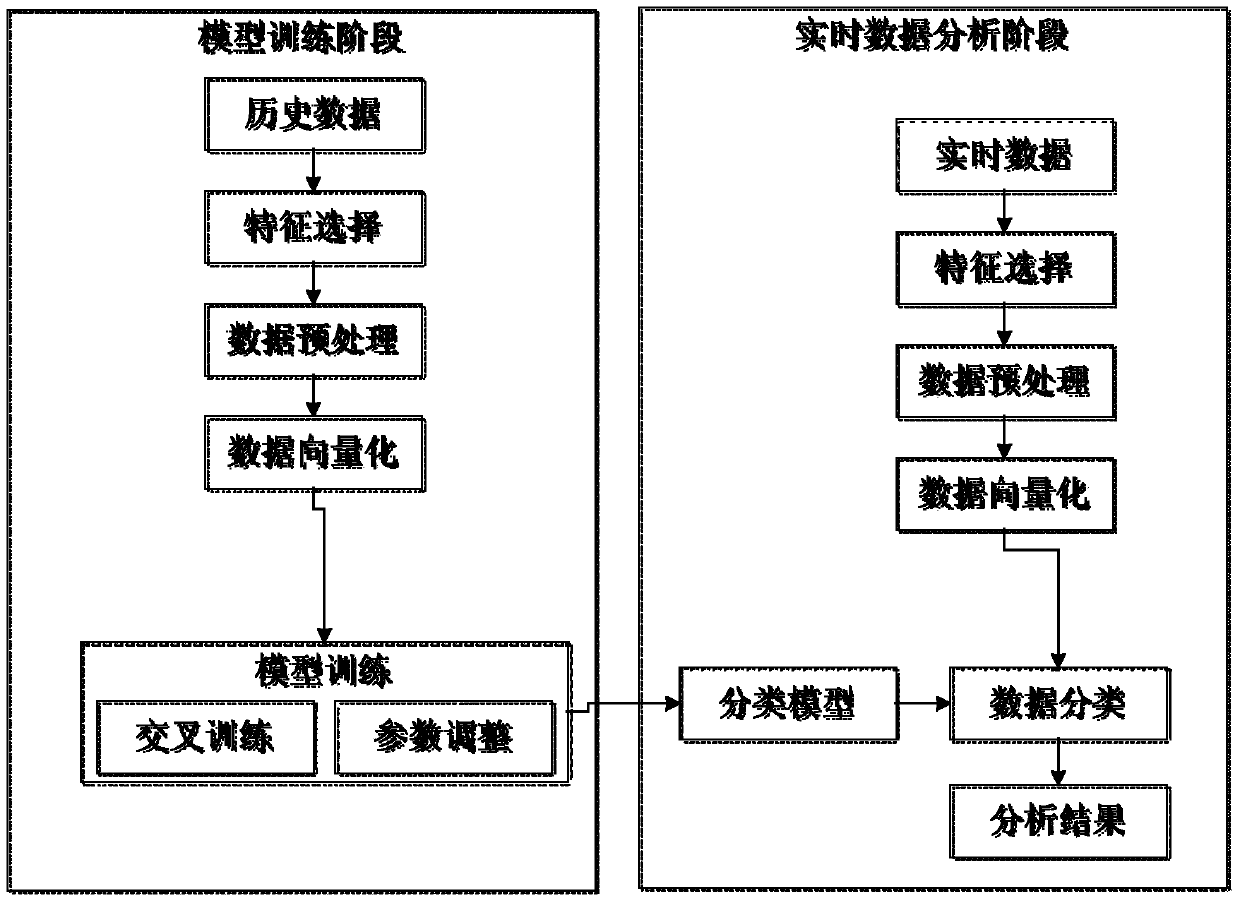

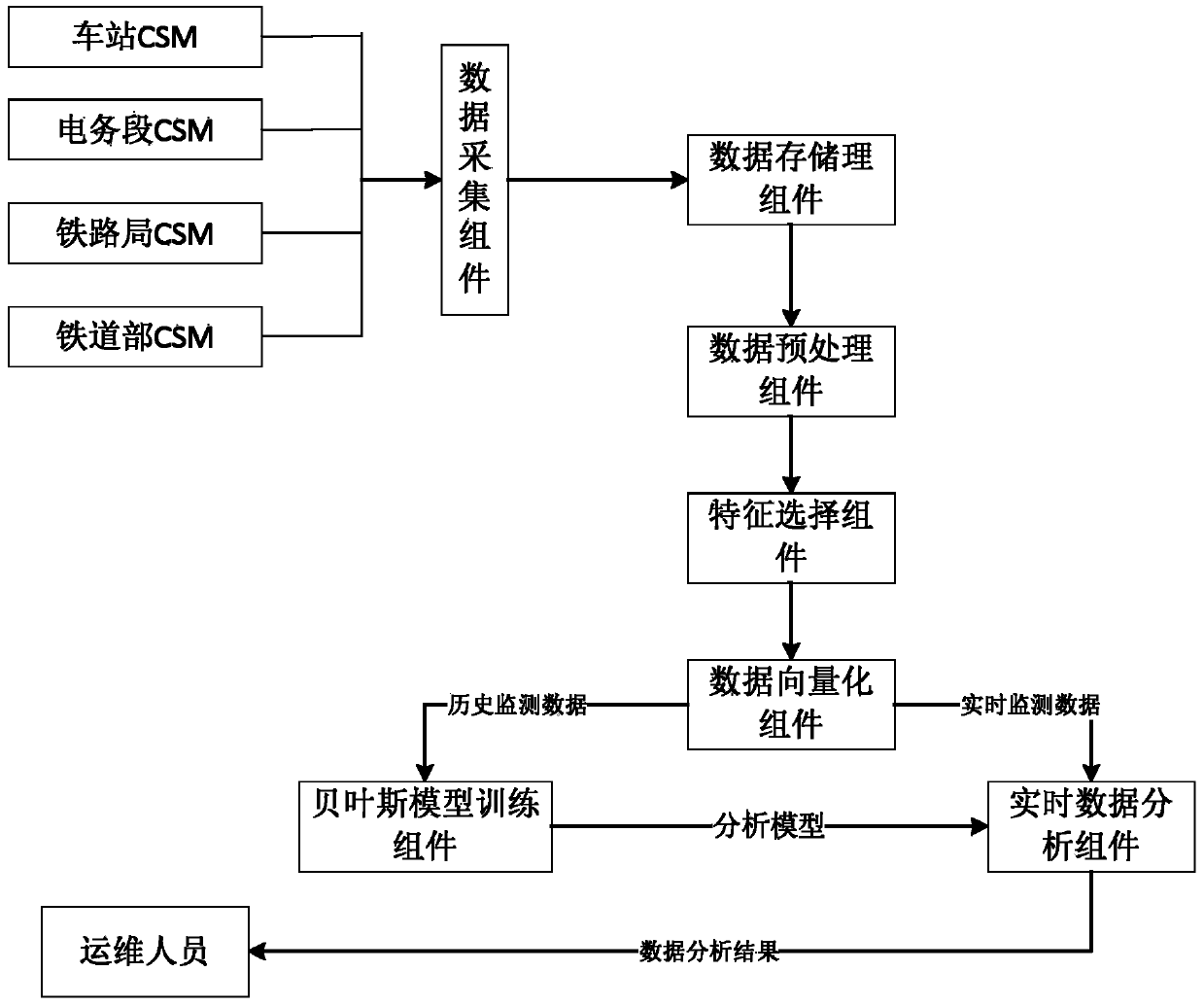

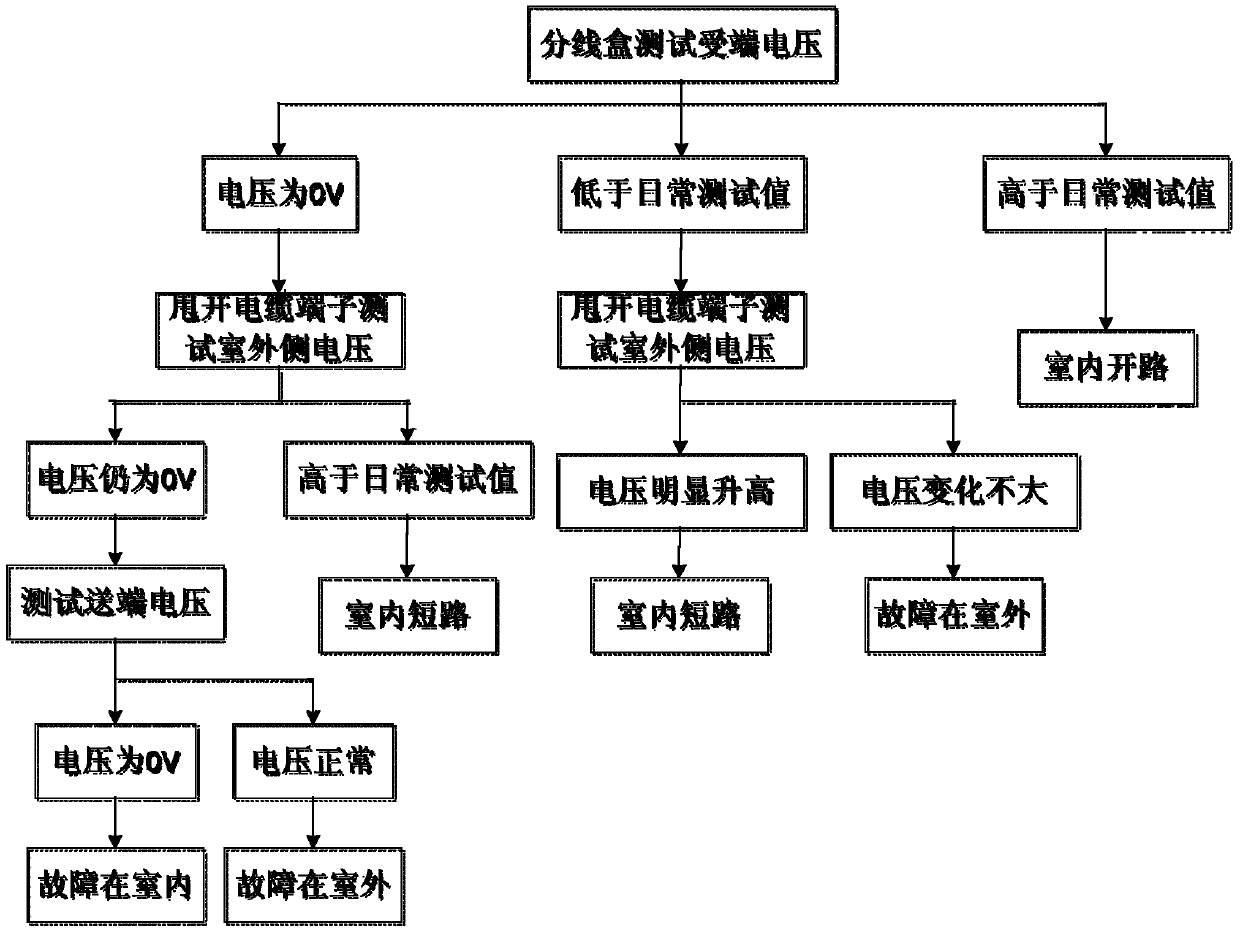

Method and system for track traffic failure recognition based on improved Bayesian algorithm

ActiveCN103699698AImprove accuracyImprove generalization abilitySpecial data processing applicationsRepair timeFault model

The invention discloses a method and a system for track traffic failure recognition based on improved Bayesian algorithm. The method comprises the following steps of: 1) determining various failure modes and corresponding monitoring values of each traffic device according to circuit structure of the traffic device, and building a failure model aiming at each failure mode and corresponding monitoring value; 2) recognizing a parent child relation among the monitoring data according to the failure model, thus obtaining a standard failure sample data; 3) training with the standard failure sample data through a Bayesian algorithm to obtain a failure recognition model, wherein weight of a parent node in the failure recognition model of each failure mode is greater than that of a child node; 4) monitoring and acquiring various monitoring values of the traffic device in real time, and recording time sequence of the monitoring values; 5) recognizing data through the failure recognition model, and determining corresponding failure. By the method and the system, accuracy of failure recognition is improved, failure repair time is reduced, the device can perform failure self-diagnosis, and traffic safety is guaranteed in the operation and maintenance aspect and the device aspect.

Owner:BEIJING TAILEDE INFORMATION TECH

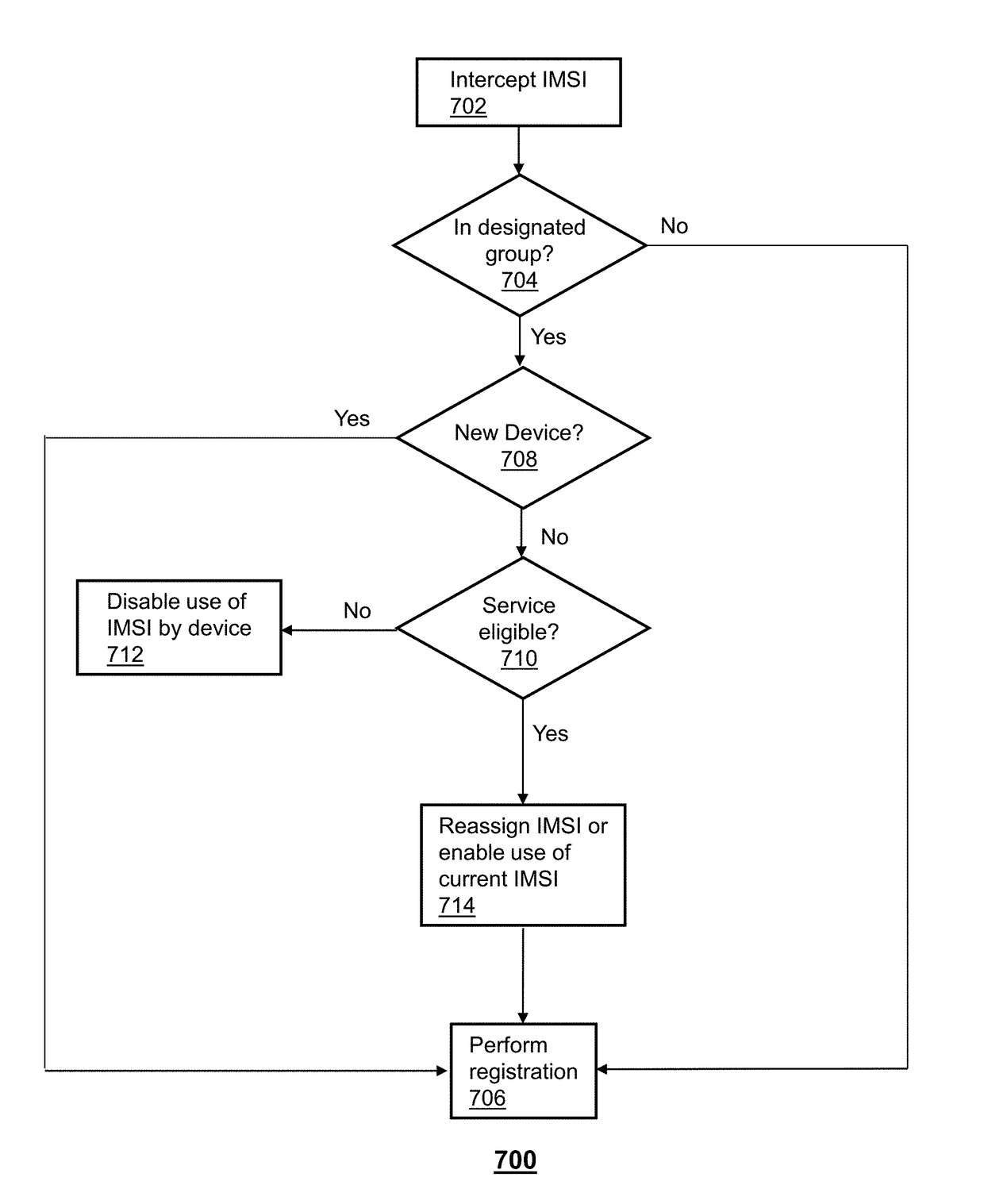

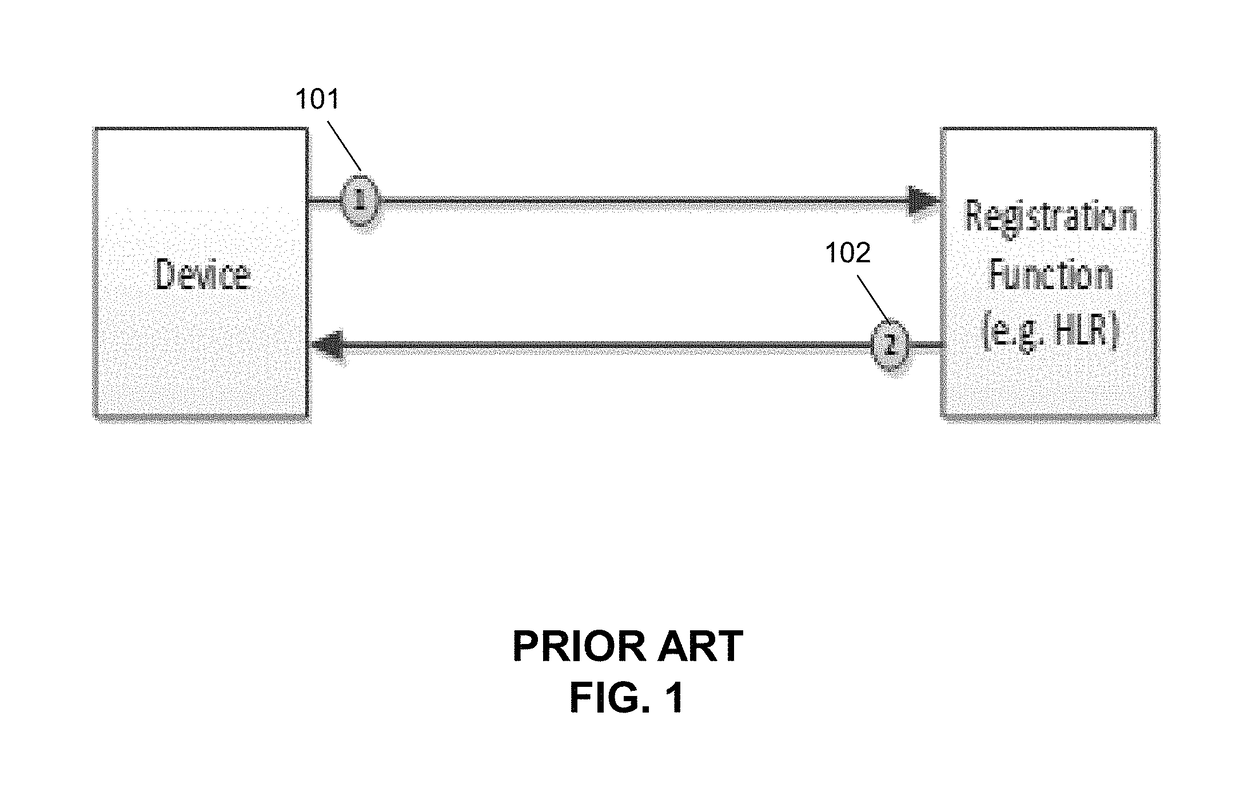

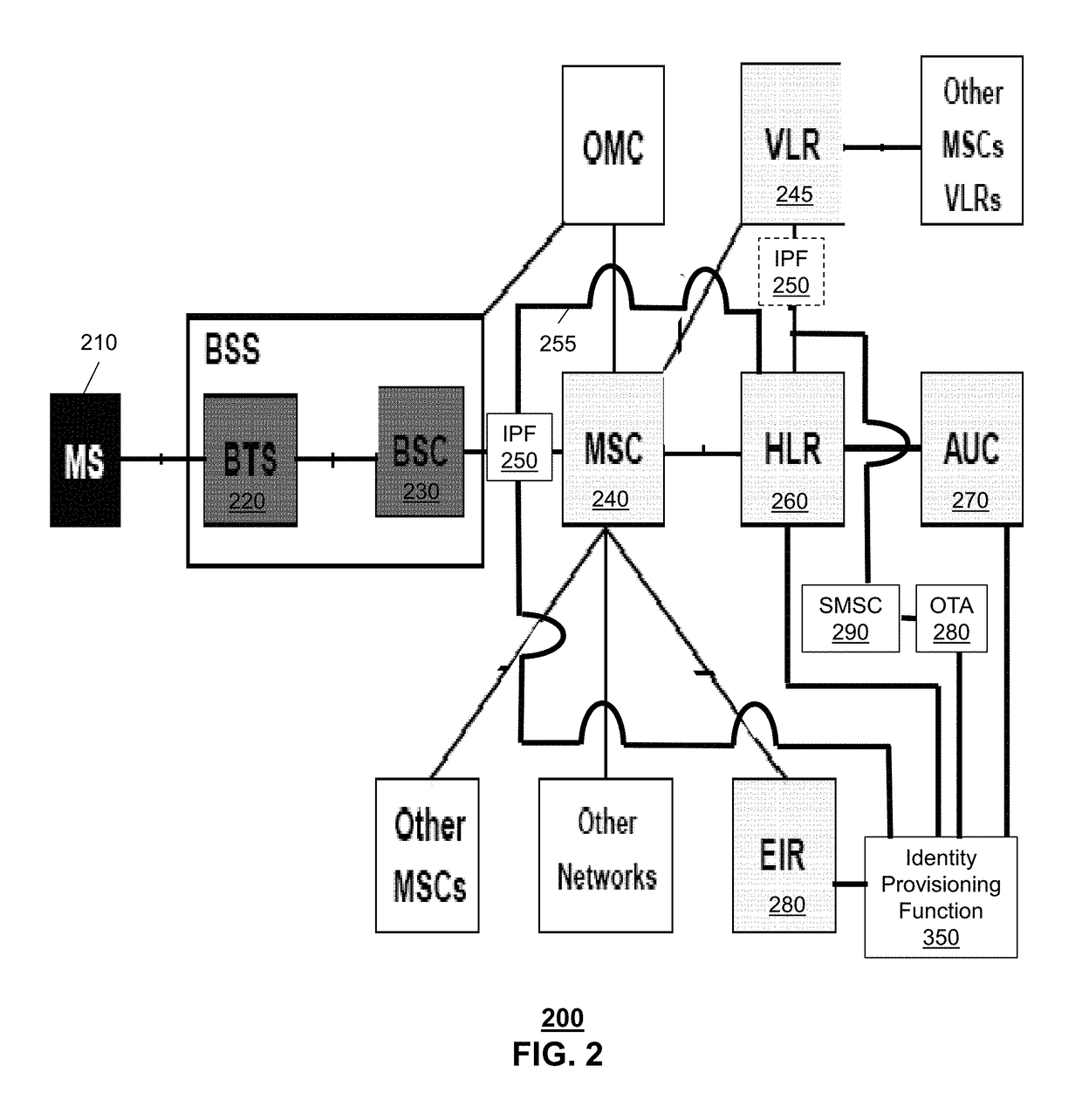

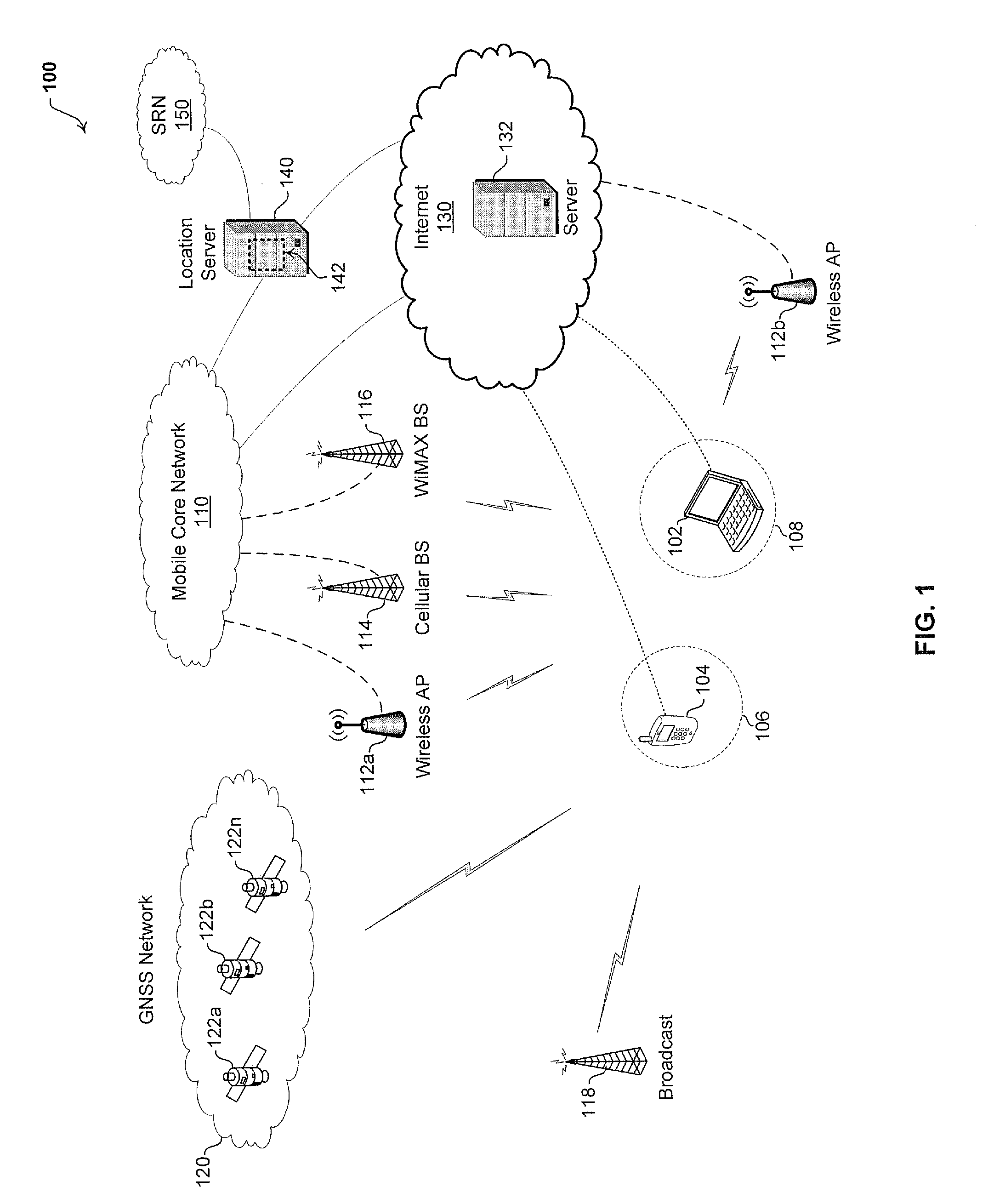

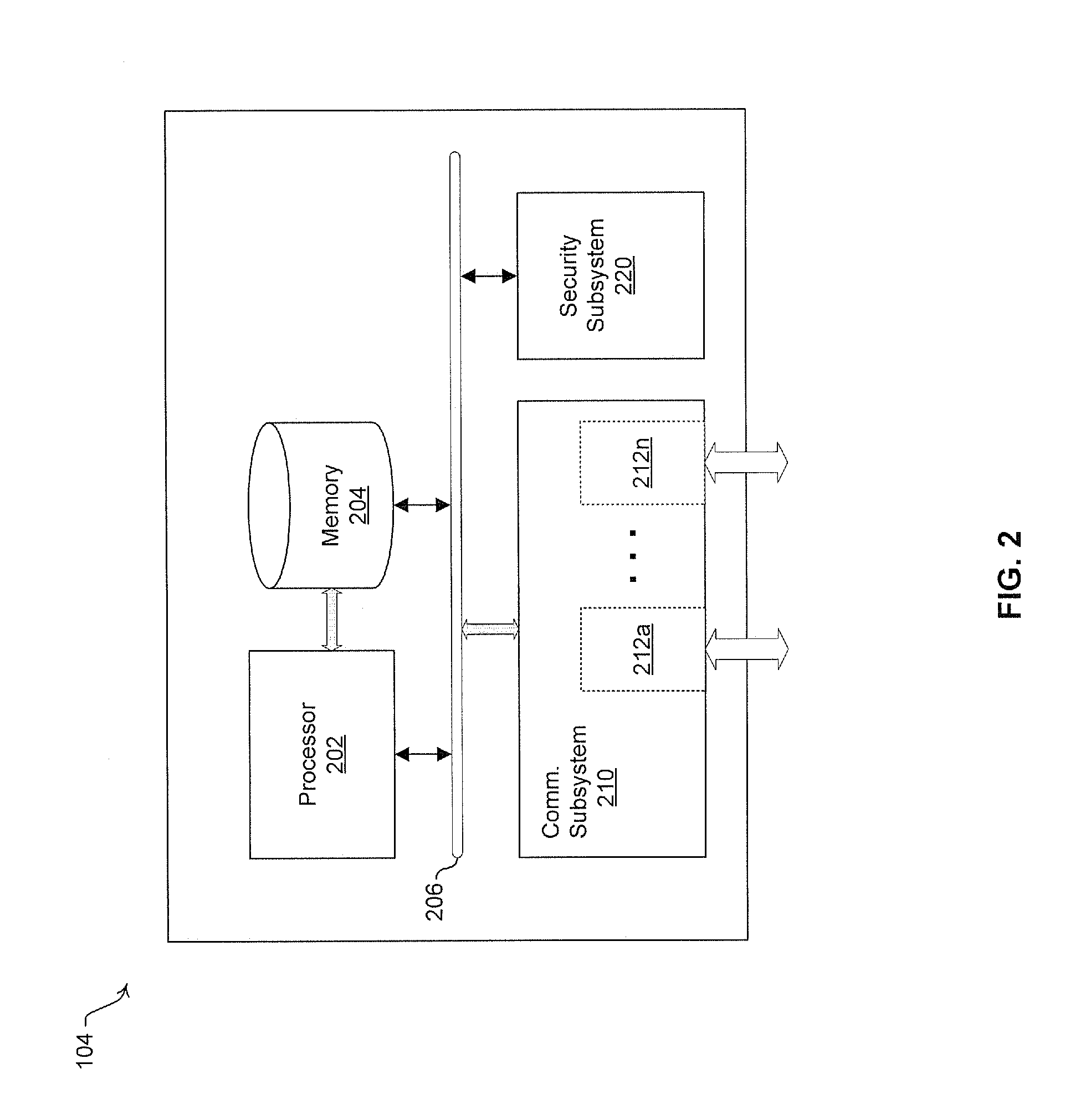

Method and apparatus for using mobile subscriber identification information for multiple device profiles for a device

ActiveUS20180160292A1Service provisioningWireless commuication servicesTelecommunicationsDevice aspects

Aspects of the subject disclosure may include, for example, a system that manages reuse of mobile subscriber identity information. Further aspects may include mobile subscriber identity information used in a device having multiple device profiles indexed, directly or indirectly, by multiple ki (e.g. shared secret keys). Other embodiments are disclosed.

Owner:AT&T INTPROP I L P +1

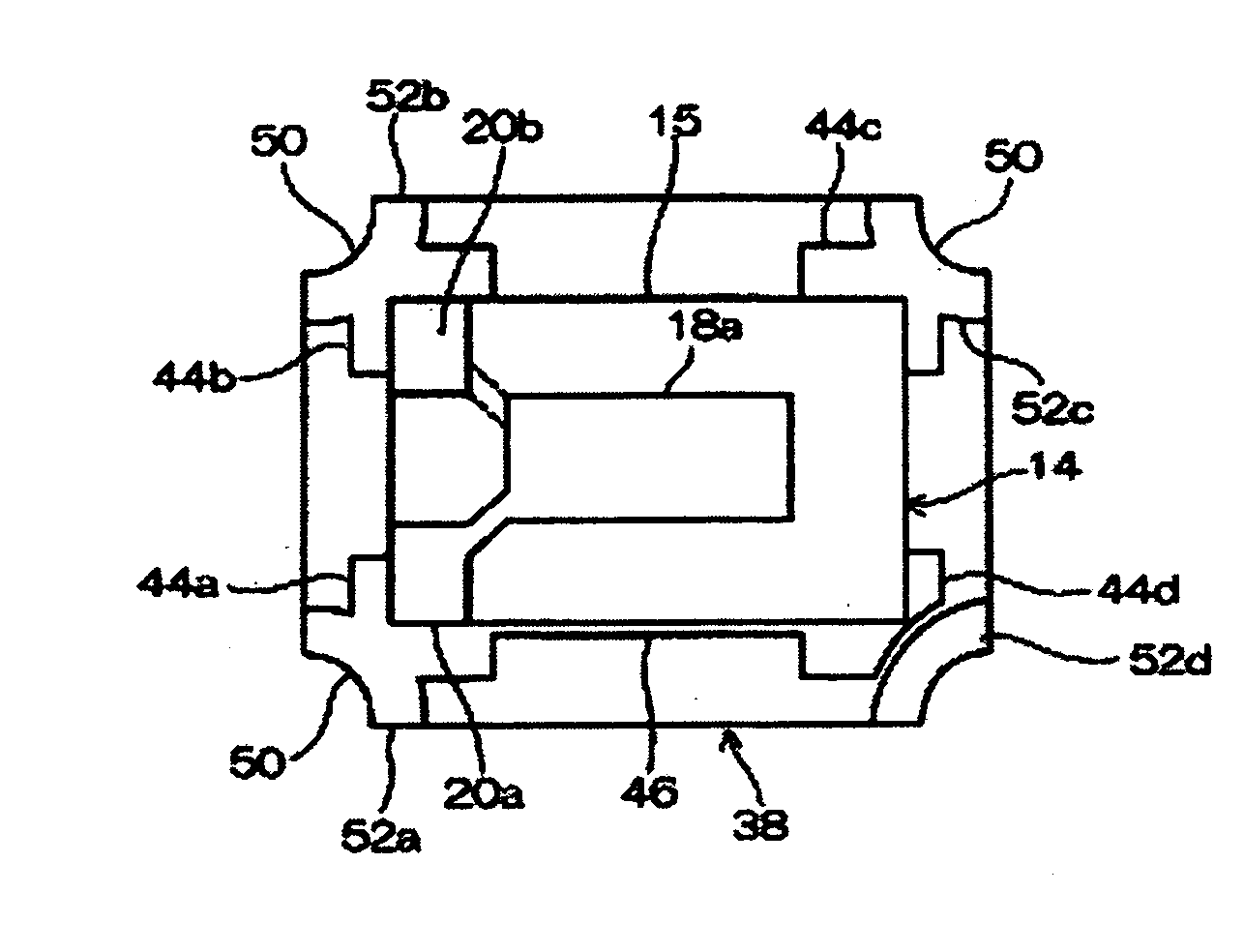

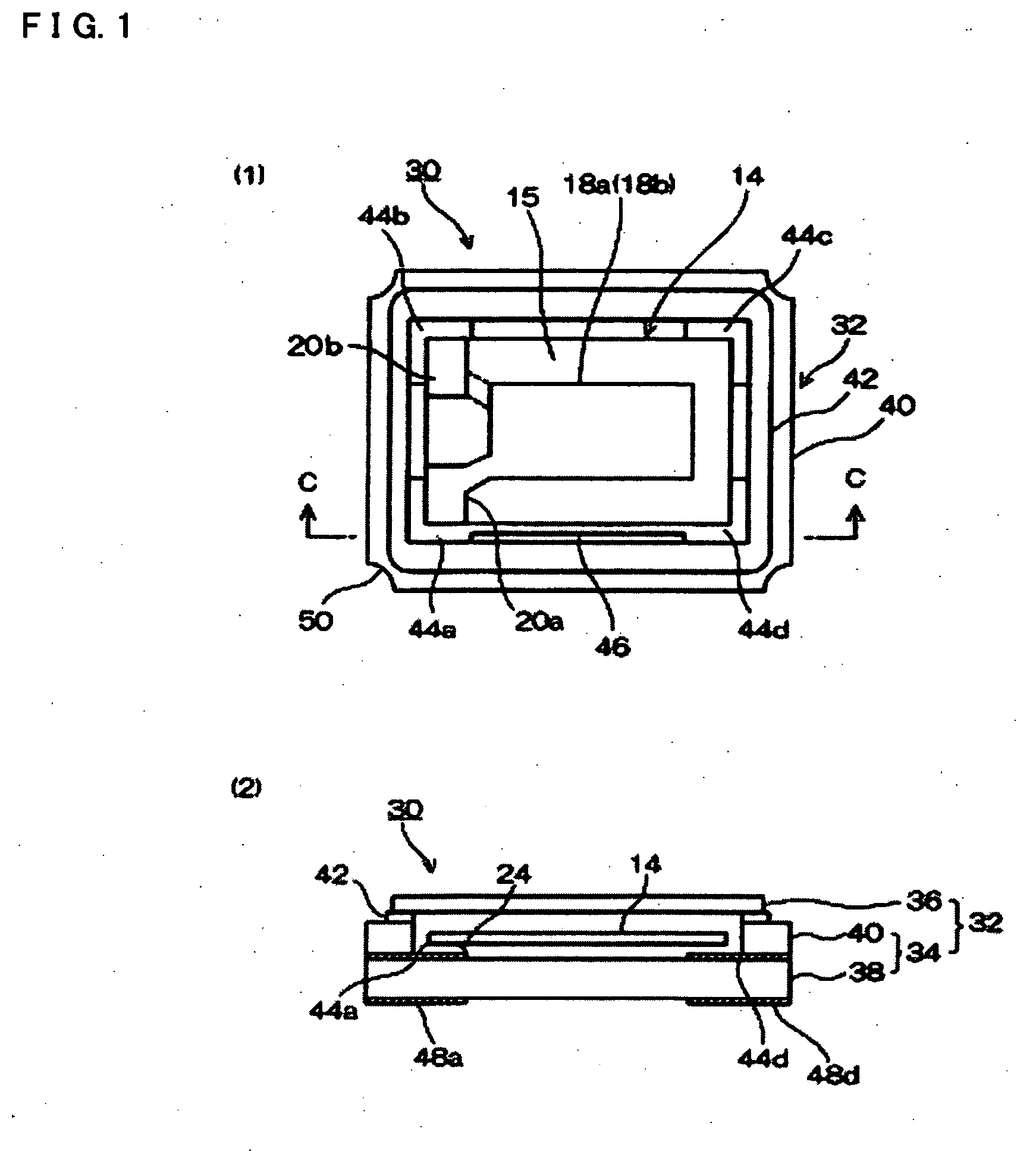

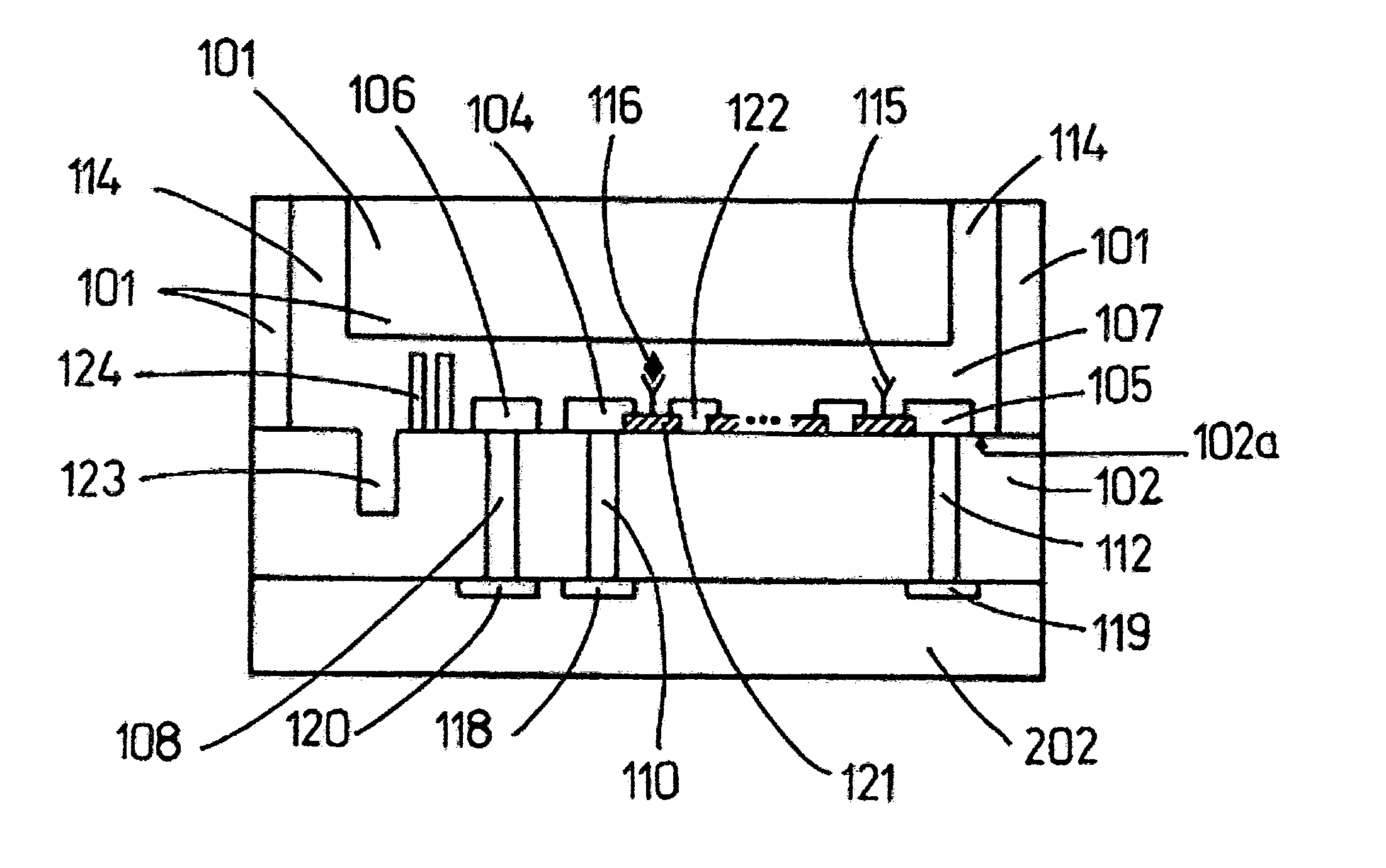

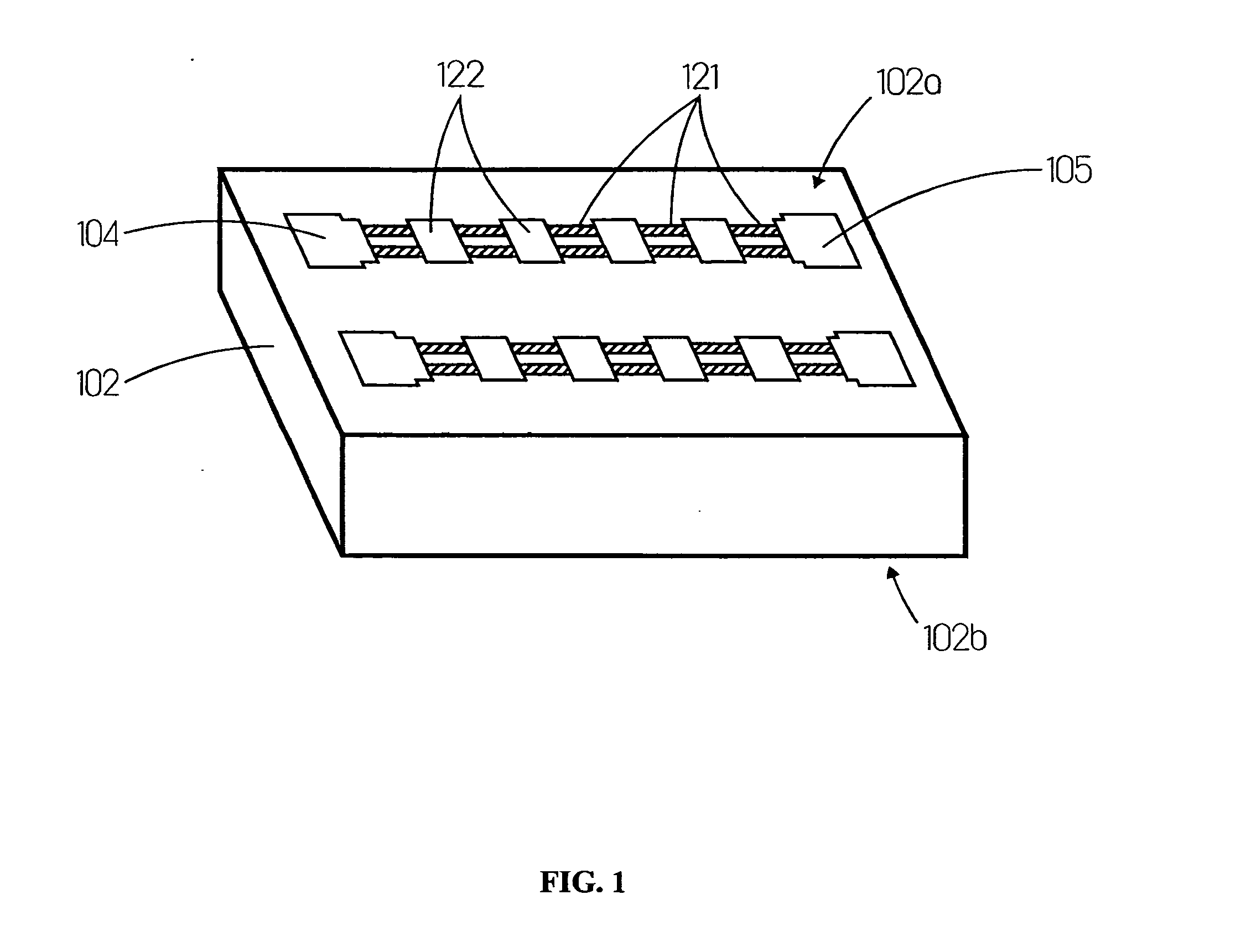

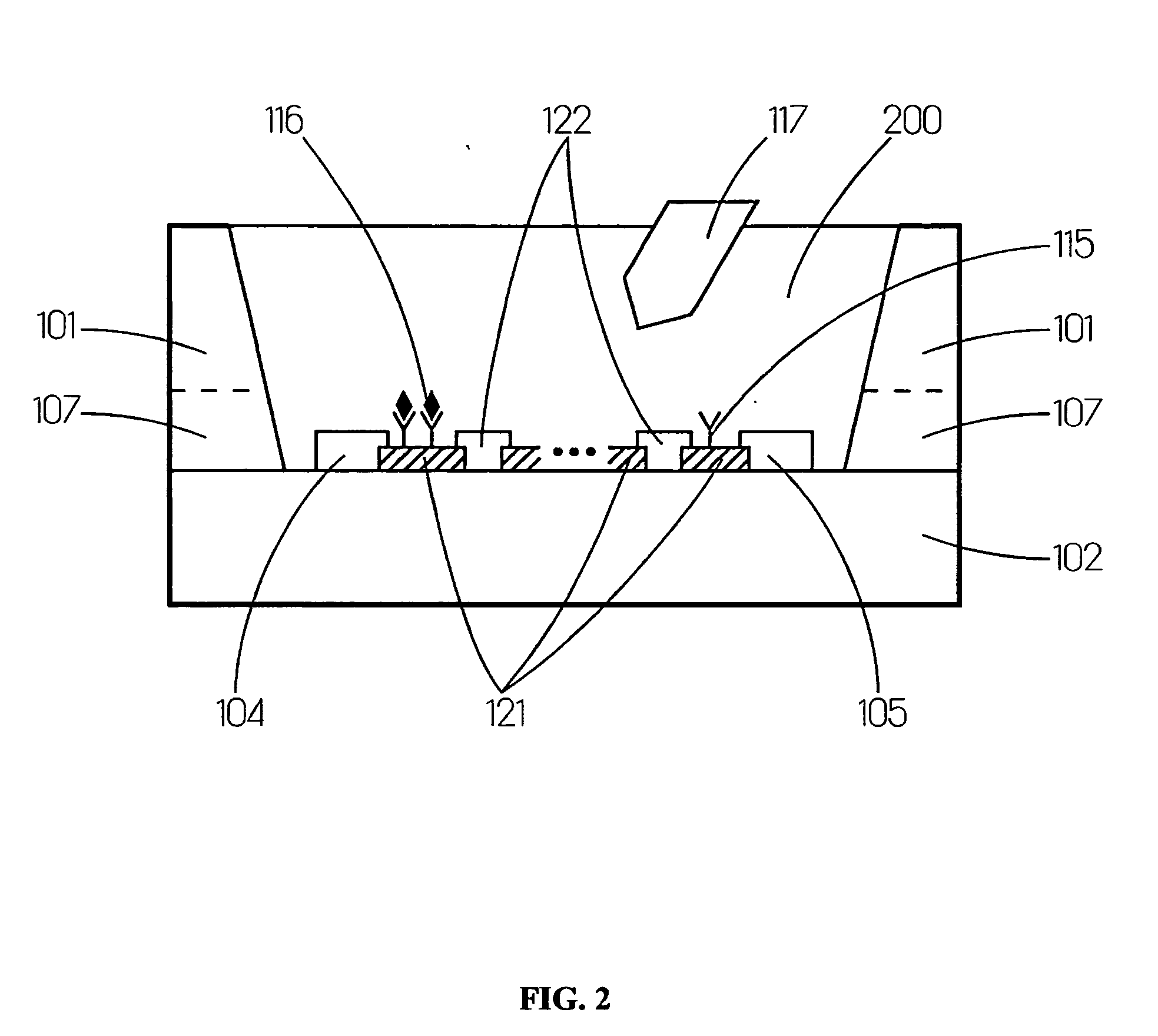

Package for electronic component and method of manufacturing piezoelectric device

InactiveUS20050184625A1Easy to changeEasy to takeImpedence networksPiezoelectric/electrostriction/magnetostriction machinesEngineeringChange positions

Aspects of the invention provide a package for accommodating a piezoelectric resonator that can include more mounting electrodes than connecting electrodes of the piezoelectric resonator element. The mounting electrodes can be electrically connected with a wiring pattern. In the lower surface of a package body, there can be formed external terminals at the four corners thereof. The external terminals are bonded to a mounting board. The external terminals are electrically connected to the mounting electrodes, respectively. The external terminal is not connected electrically to either of the mounting electrodes. Therefore, positions of the external terminals for operating the piezoelectric resonator can be changed based on whether a pair of connecting electrodes of the piezoelectric vibration element is bonded to the mounting electrodes, or it is connected to the mounting electrodes. Accordingly, it can be possible to easily change positions of external terminals for connecting to a circuit on a board.

Owner:SEIKO EPSON CORP

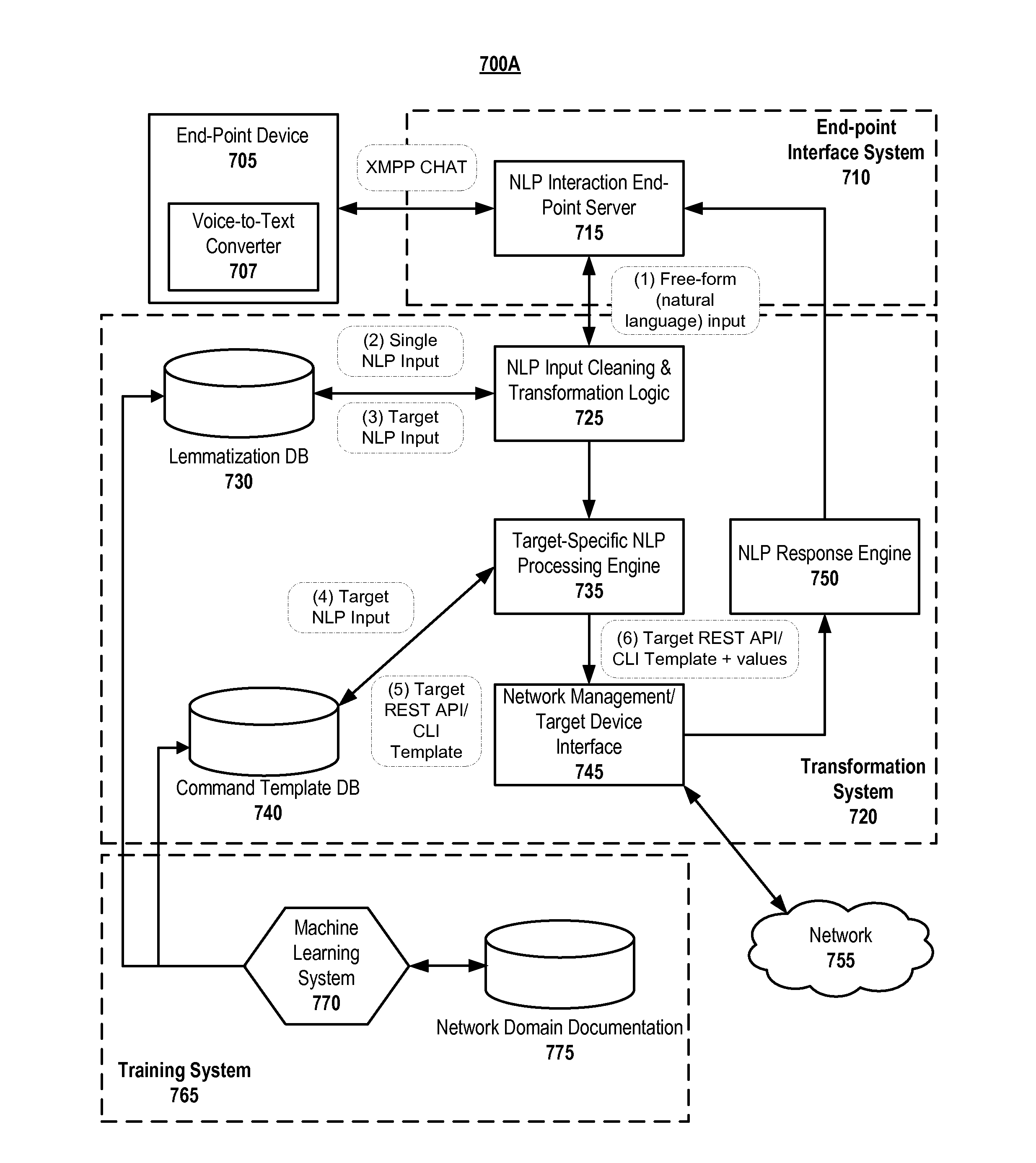

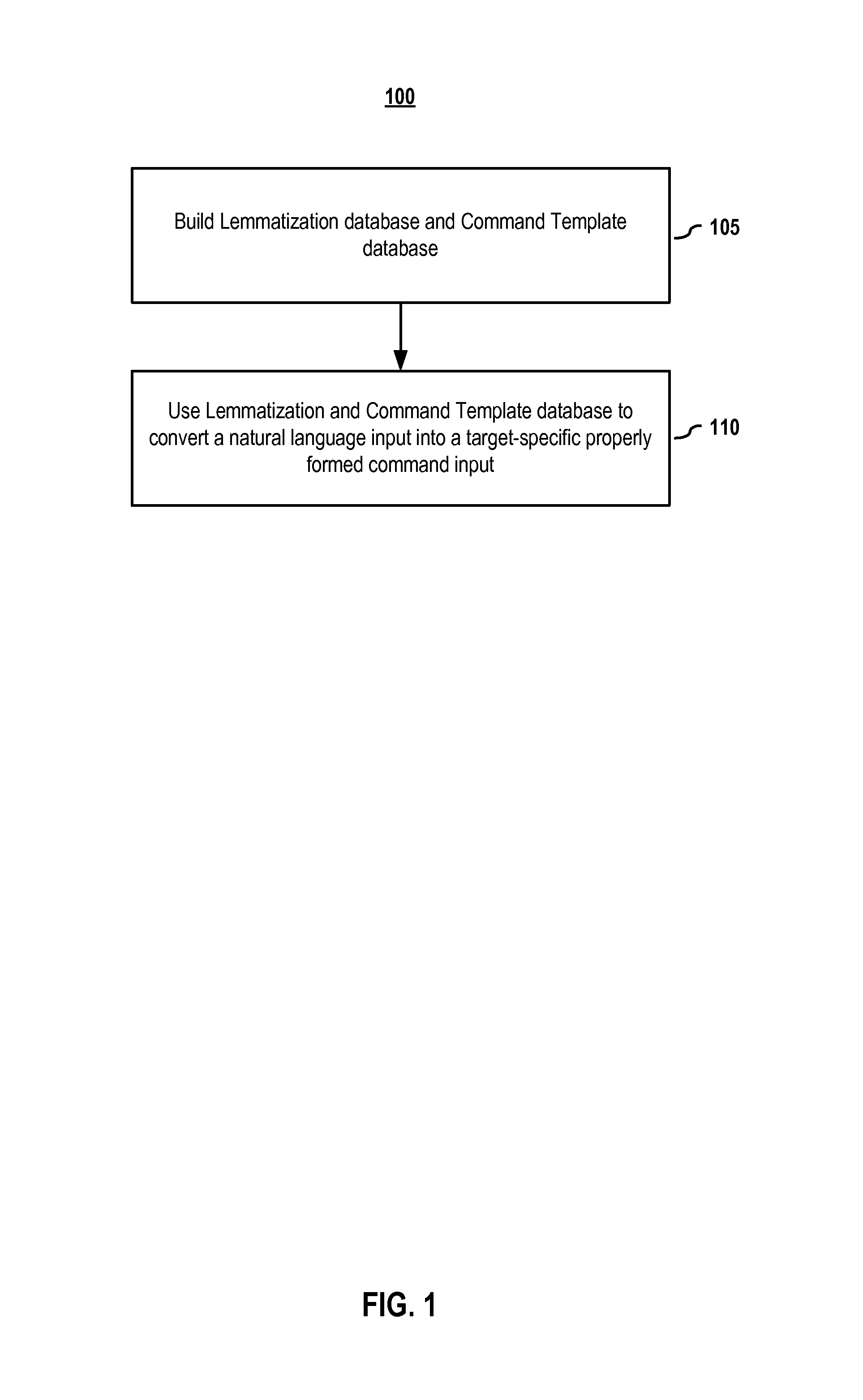

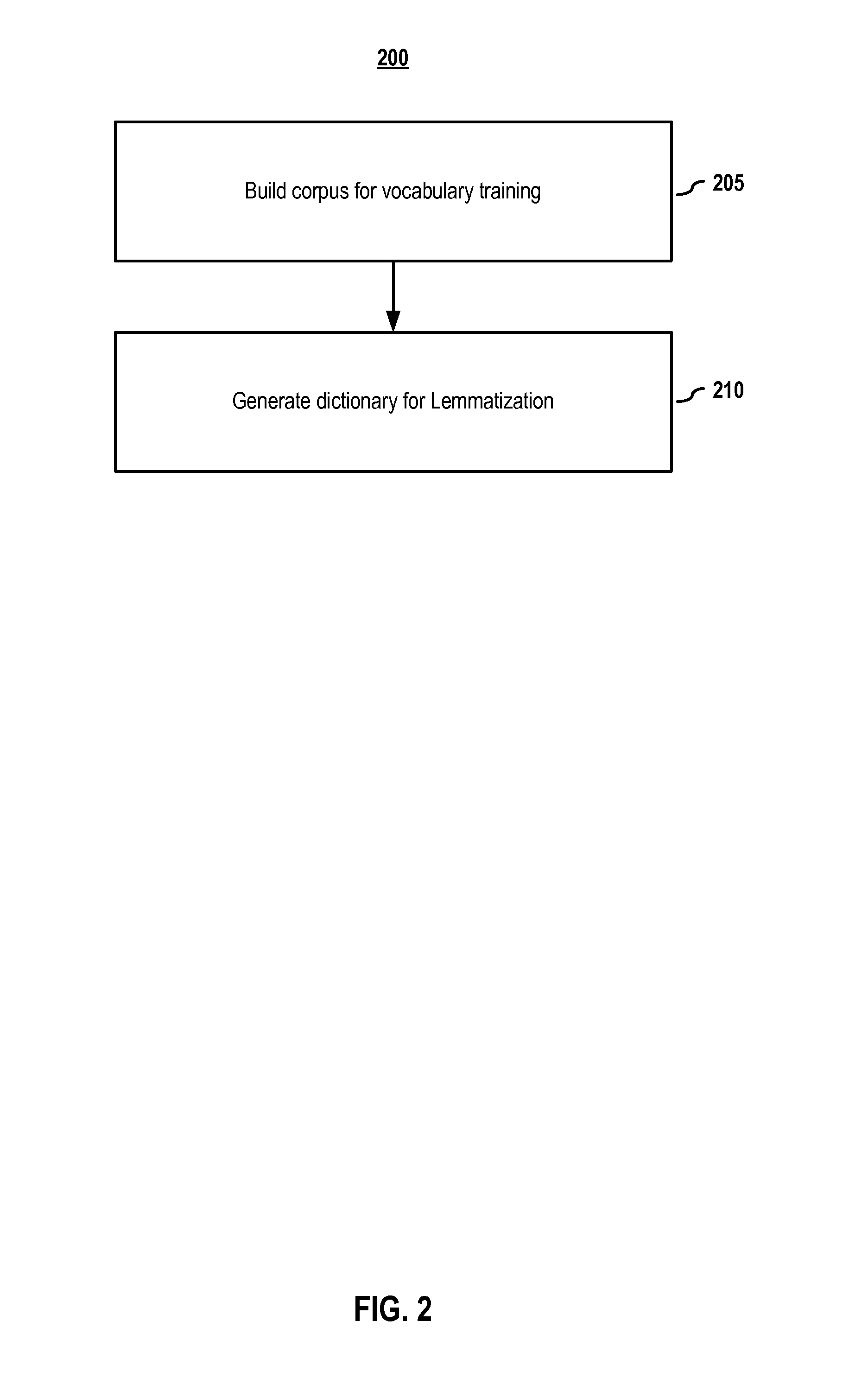

Voice-based input using natural language processing for interfacing with one or more devices

Aspects of the present invention provide a more universal, easy, natural, and vendor-agnostic interface to configure, manage, and / or monitor devices in networks. In embodiments, a user-friendly natural language interface voice interface may be used to “live chat” with one or more devices. In embodiments, a natural language input from a user intended for a target device is received and converted into one or more properly formed commands that are target-specific for the target device and may be executed by the target device. In embodiments, results from the execution of the one or more commands may be appropriately formatted for presentation to the user.

Owner:DELL PROD LP

Integrated sensing device and related methods

InactiveUS20130056367A1Facilitating detection and screeningRapid and accurate and reliable and low costImmobilised enzymesBioreactor/fermenter combinationsNucleic acidChemical substance

The present invention is generally directed to devices and methods for sensing a variety of biologically-related substances and / or chemical substances. In a device aspect, the present invention is directed to a multilayer device for sensing metal ions, non-biological molecules, biological molecules, or whole cells. In a method aspect, the present invention is directed to a method for sensing species such as ions, protons, metal ions, non-biological molecules, whole cells, and biological molecules, for example one or more biologically-related substances such as proteins, nucleic acids, DNA, RNA, enzymes, and chemical substances such as water contaminants.

Owner:NANOTECH BIOMACHINES

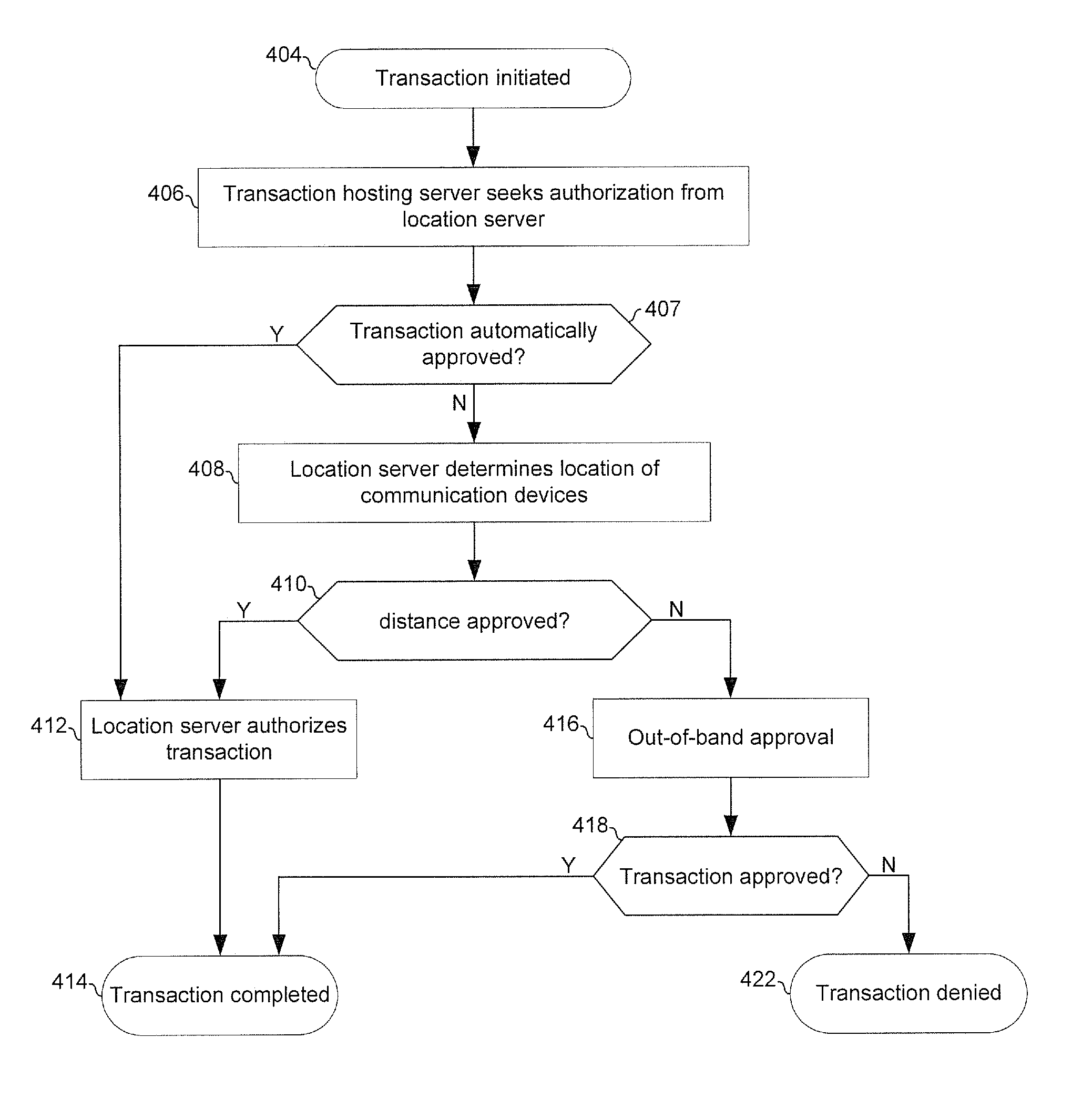

Method and system for authorizing transactions based on relative location of devices

InactiveUS20110202460A1Unauthorised/fraudulent call preventionEavesdropping prevention circuitsFinancial transactionCommunication device

Aspects of a method and system for authorizing transactions based on relative location of devices are provided. In this regard, data relating to a location of a first communication device and data relating to a location of a second communication device may be received, a distance between the first communication device and the second communication device may be determined based on the received data, and whether to approve a transaction may be determined based on the determined distance. The transaction may have been initiated from one of the first communication device and the second communication device, and may comprise a need to access an account. The transaction may be approved in instances that the first communication device and the second communication device are within a predetermined distance of each other. The received data may comprise distance information determined via communications between the first communication device and the second communication device.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

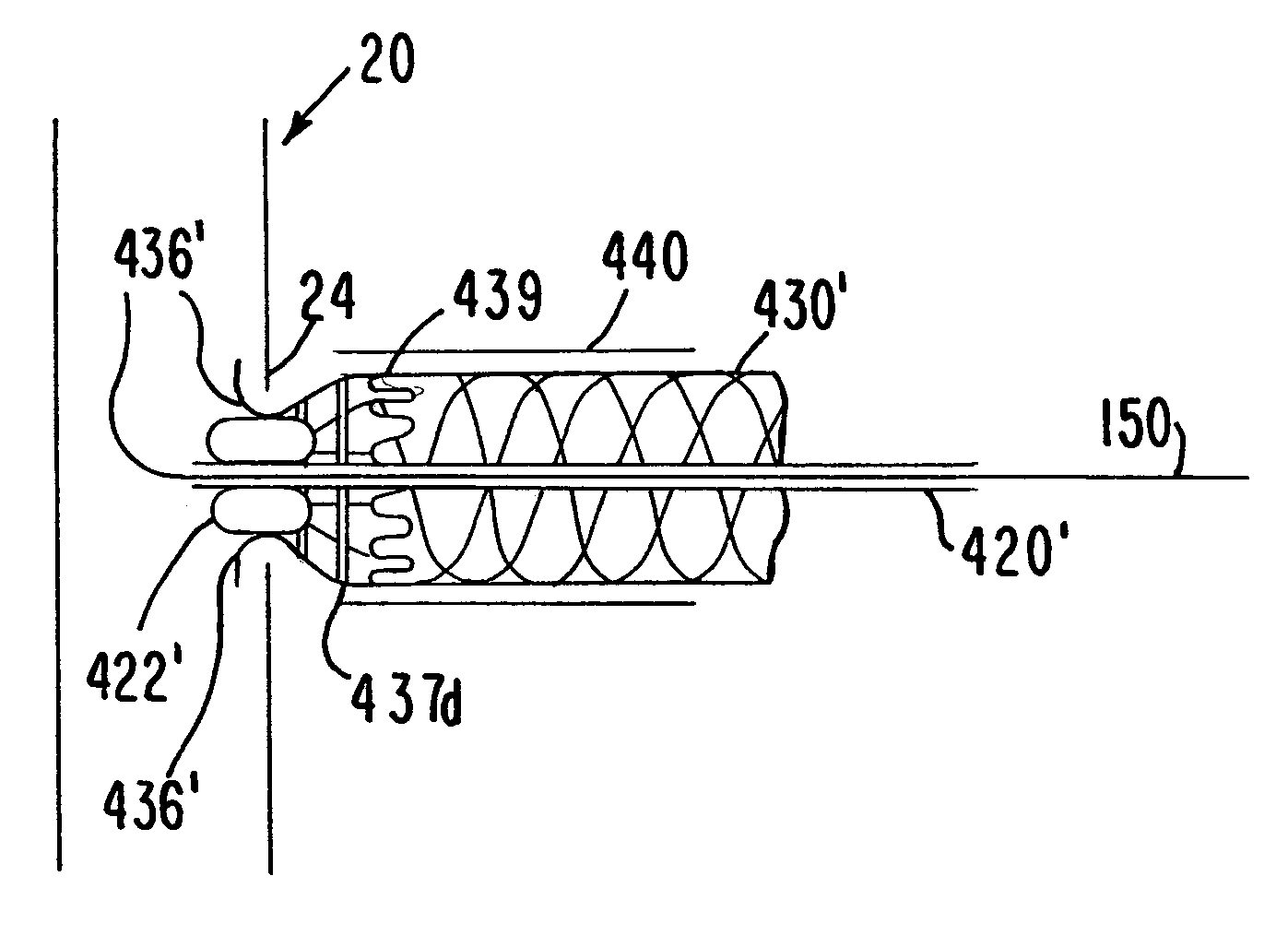

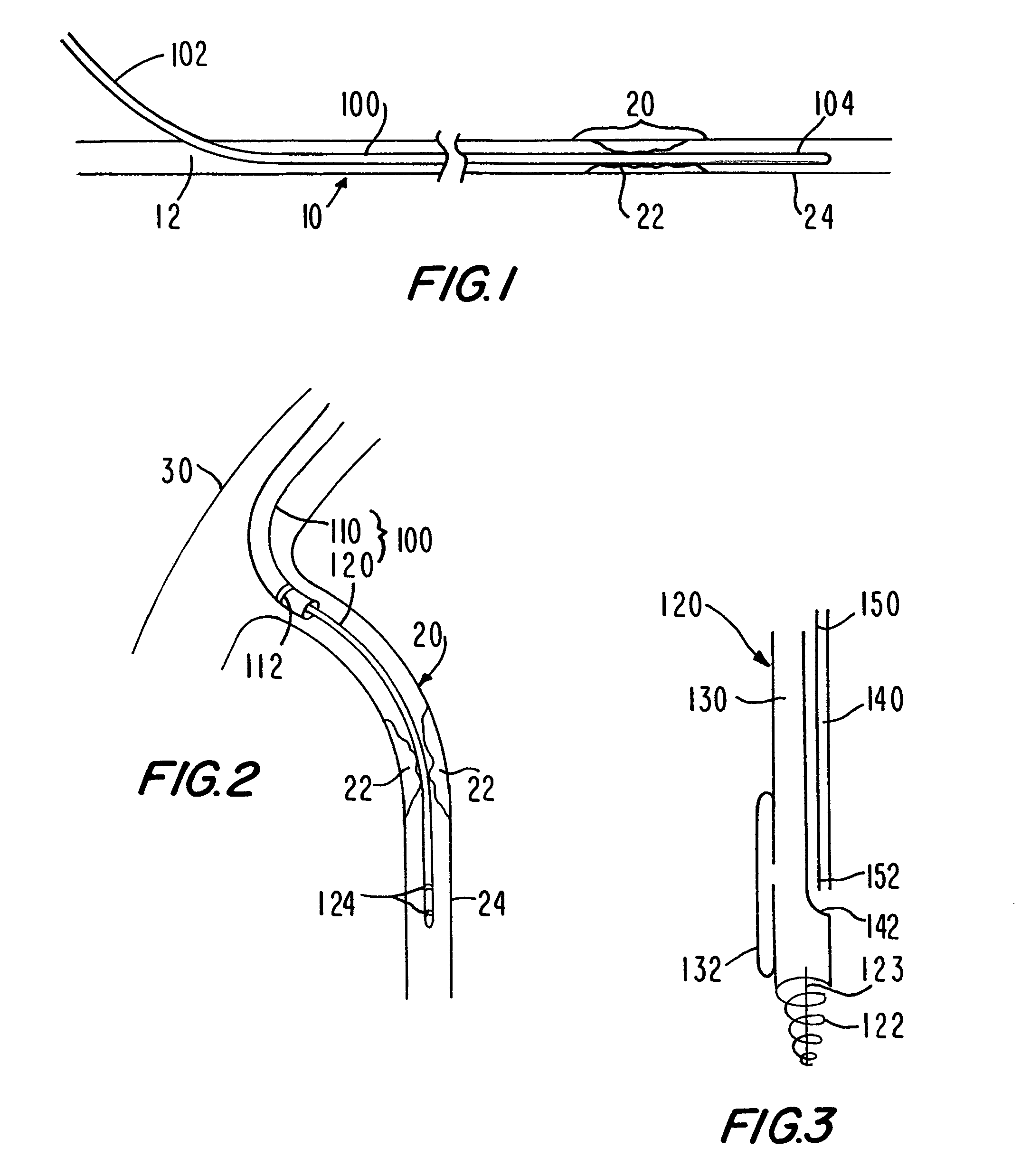

Medical grafting methods and apparatus

InactiveUS7578829B2Enhance their bio-utilityElasticityStentsBalloon catheterBody organsSurgical site

Methods and apparatus for delivering and installing a new length of tubing between two sections of a patient's existing body organ tubing and at least partly outside of that existing structure. For example, the new length of tubing may be for the purpose of providing the patient with a coronary bypass. The new tubing may be an artificial graft, a natural graft (harvested elsewhere from the patient), or both. The new tubing is delivered to and installed at the operative site primarily by working through the patient's existing tubular body organ structure. This avoids the need for any significant surgery on the patient. The artificial grafts may have shapes other than tubular. Certain procedural and apparatus aspects of the invention have uses other than in connection with grafting in general or tubular grafting in particular.

Owner:ST JUDE MEDICAL ATG

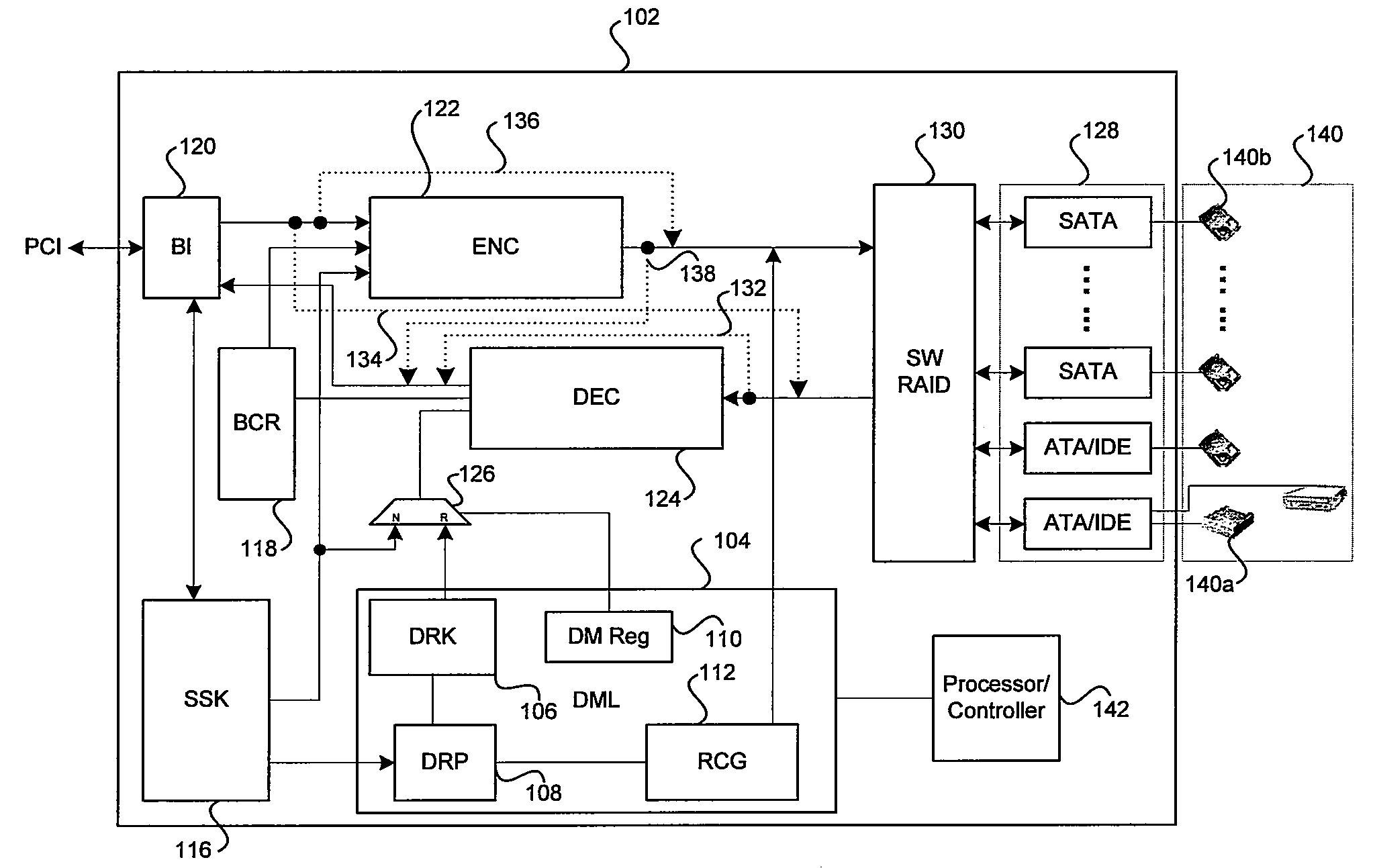

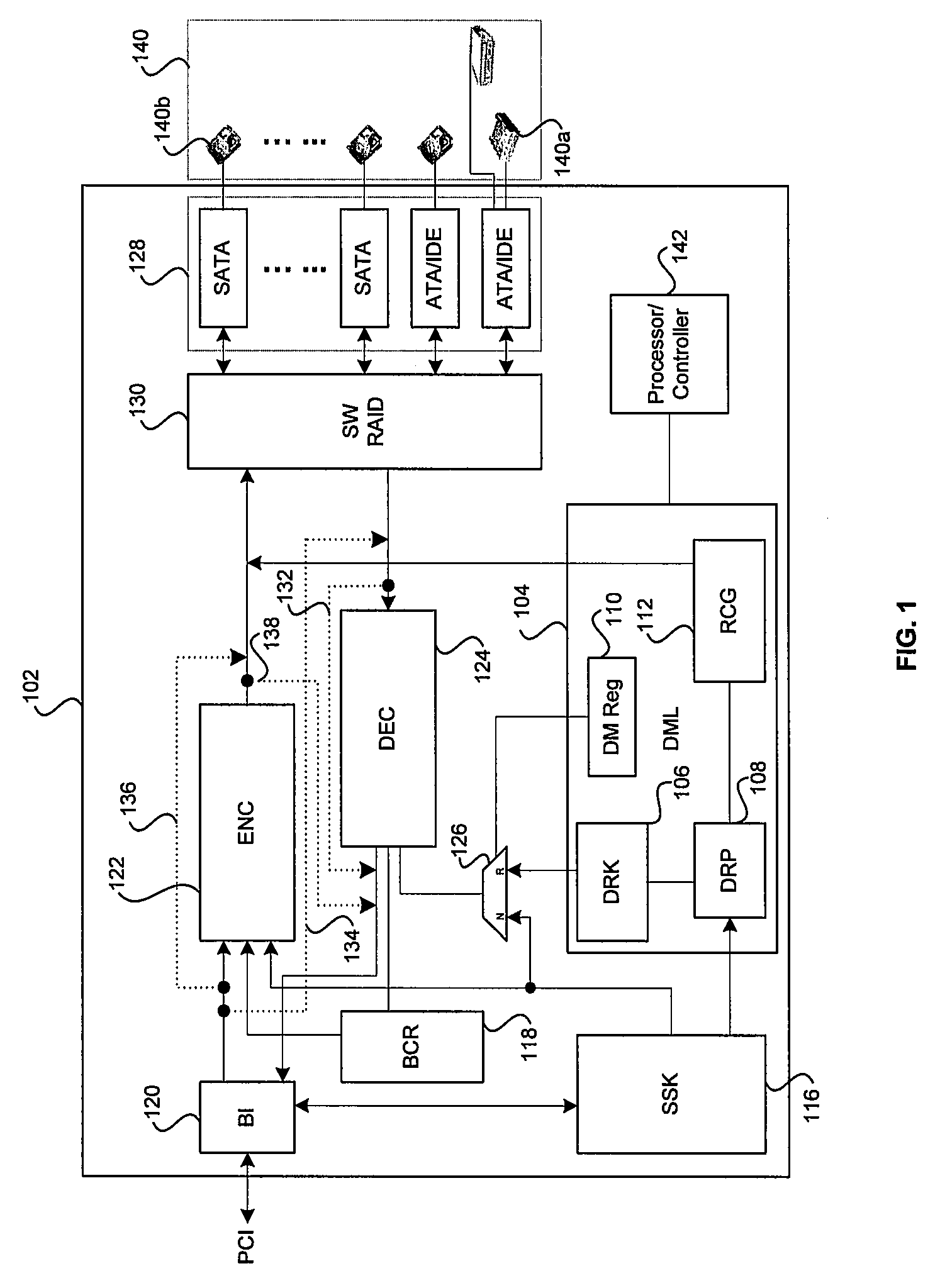

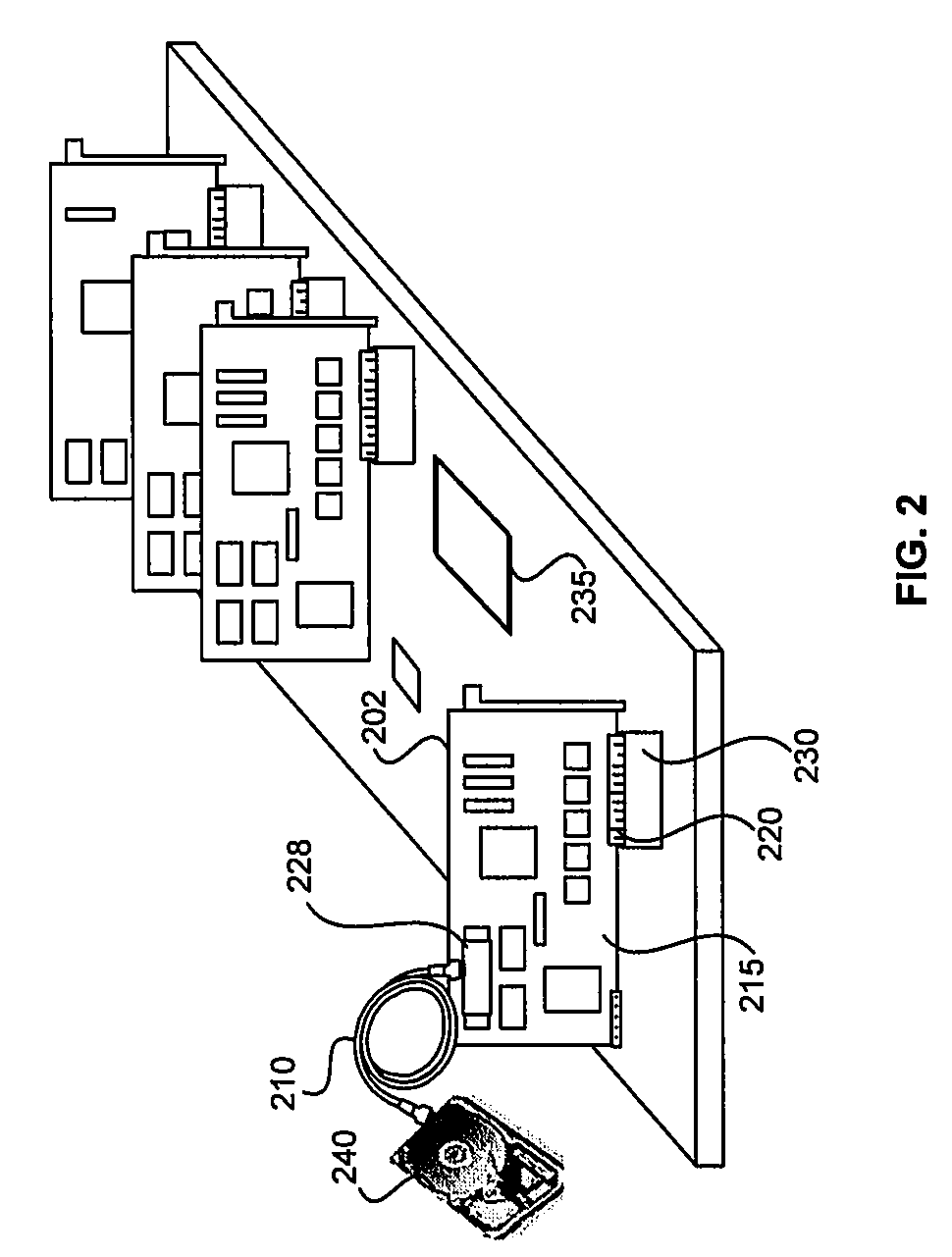

Method and system for disaster recovery of data from a storage device

InactiveUS20090052669A1Promote generationEnhanced couplingKey distribution for secure communicationEncryption apparatus with shift registers/memoriesPasswordRemovable media

Aspects of the invention provide a method and system for securely managing the storage and retrieval of data. Securely managing the storage and retrieval of data may include receiving a first disaster recovery code and acquiring a first password corresponding to the first disaster recovery code. A first disaster recovery key may be generated based on the first disaster recovery code and the first password. Another aspect of the invention may also include generating the received first disaster recovery code based on said first password and the first disaster recovery key. The generated disaster recovery code may be securely stored on at least a portion of a storage device or a removable media. Data stored on the storage device may be encrypted using the first generated disaster recovery key. Additionally, data read from the storage device may be decrypted using the generated first disaster recovery key.

Owner:AVAGO TECH INT SALES PTE LTD

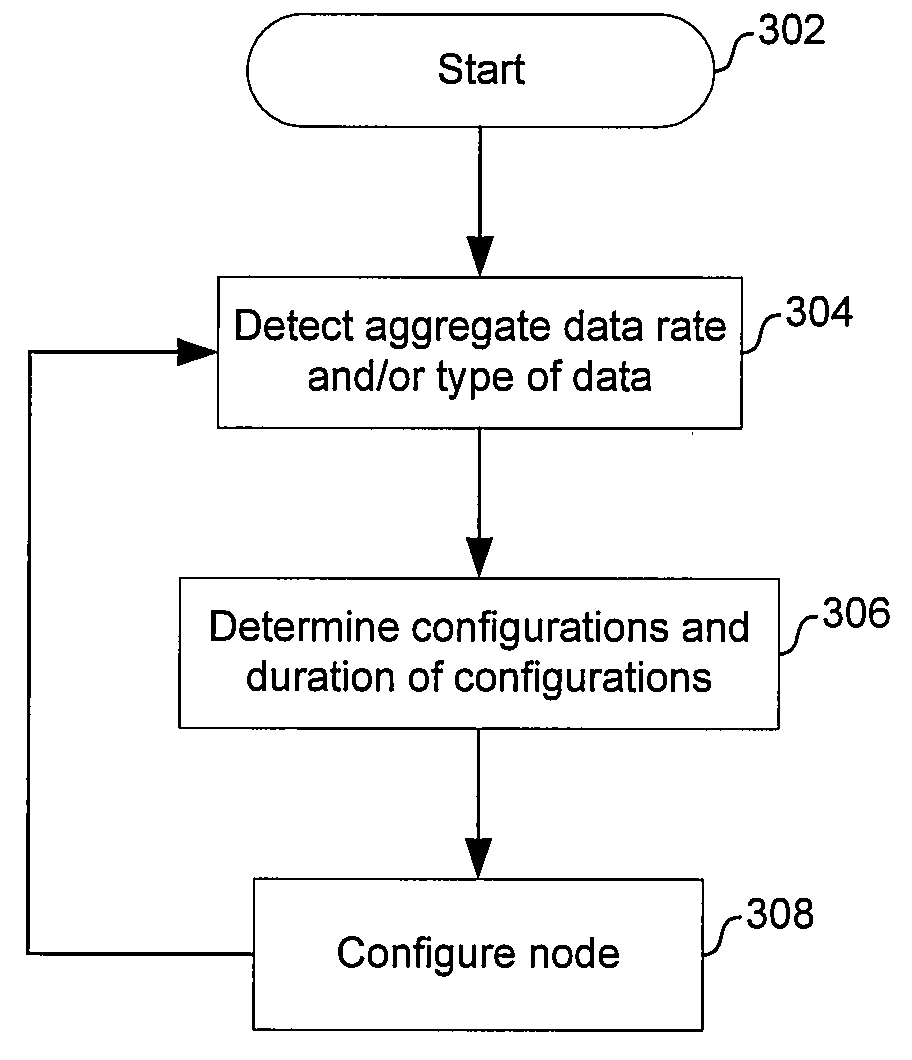

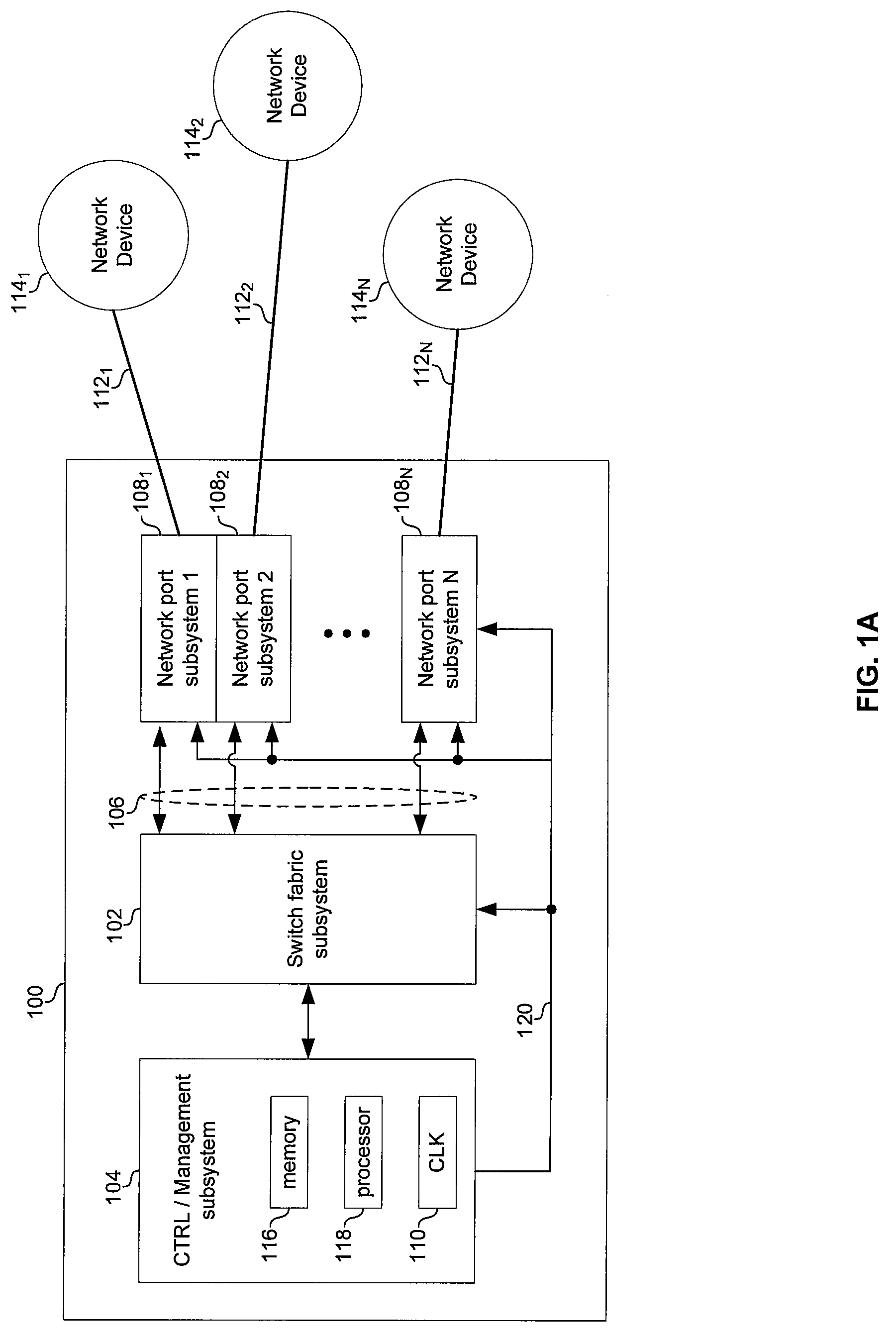

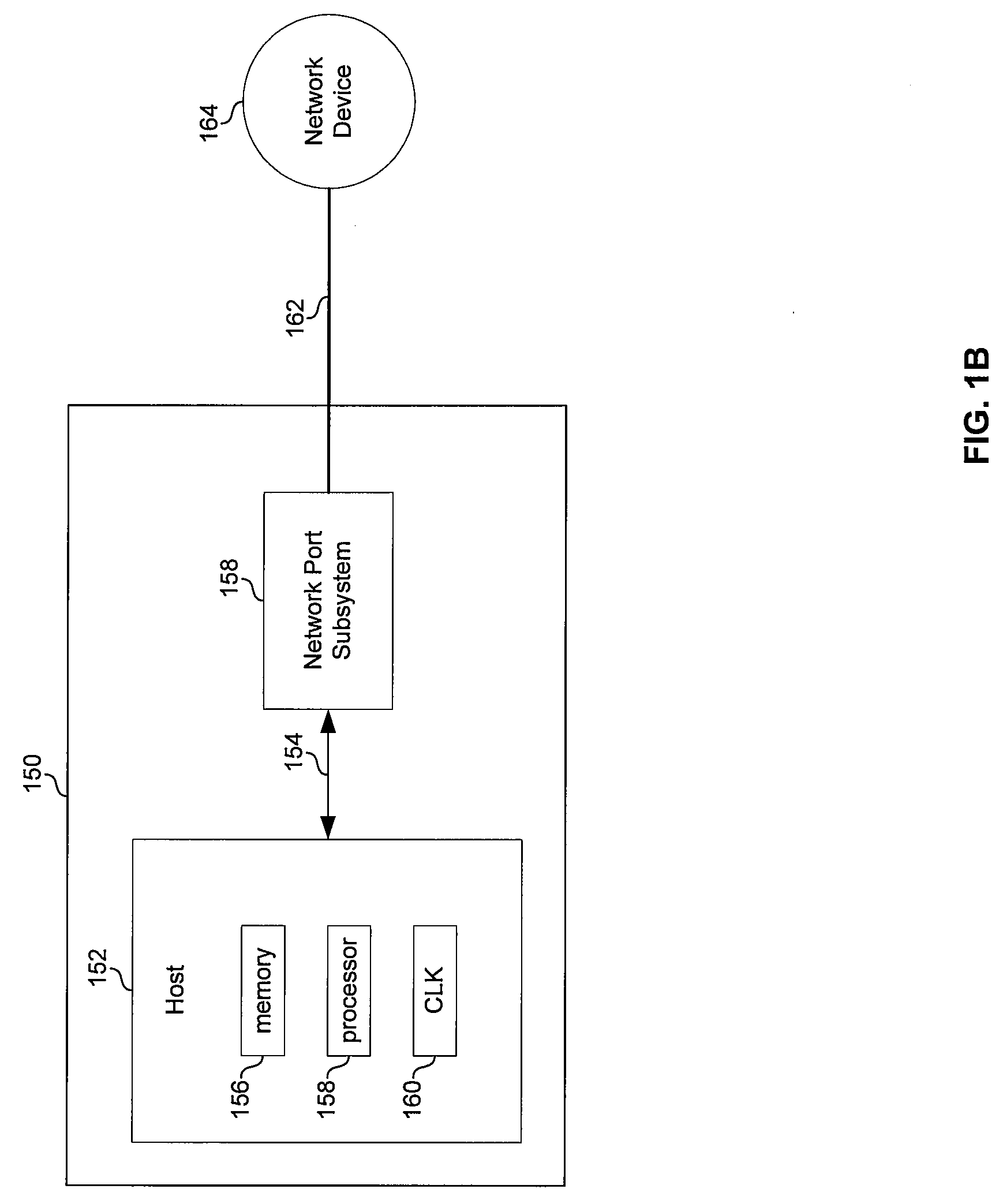

Method and system for duty cycling portions of a network device based on aggregate throughput of the device

Aspects of a method and system for duty cycling a network device based on aggregate throughput of the device are provided. In this regard, a limit on aggregate ingress and egress data of a network device during a time interval may be determined. Processing of data by the network device may be duty cycled based on the determination. The device may process data at a first rate during a first portion of the time interval and process data at a second rate during a remaining portion of the time interval. In this regard, portions of the device may be slowed or powered down during the first portion of the time interval. Power consumed by the device during the first portion of the time interval may be less than power consumed by the device during the remaining portion of the time interval.

Owner:AVAGO TECH INT SALES PTE LTD

Method of manufacturing luminescence device, and luminescence device

InactiveUS20050053719A1Long lastingProgress can be suppressedElectroluminescent light sourcesSolid-state devicesEngineeringLuminescence

Aspects of the invention provide a method of manufacturing a luminescence device including forming the first electrode on a substrate, forming a function layer including a luminescence layer on the first electrode, forming a second electrode on the function layer, and forming a sealing layer that covers a luminescence portion, formed of the first electrode, the function layer, and the second electrode, and the sealing layer is formed by an ink-jet method. Accordingly, the deterioration of a luminescence device that is sealed with the sealing layer can be prevented for a long period of time by an inexpensive method.

Owner:SEIKO EPSON CORP

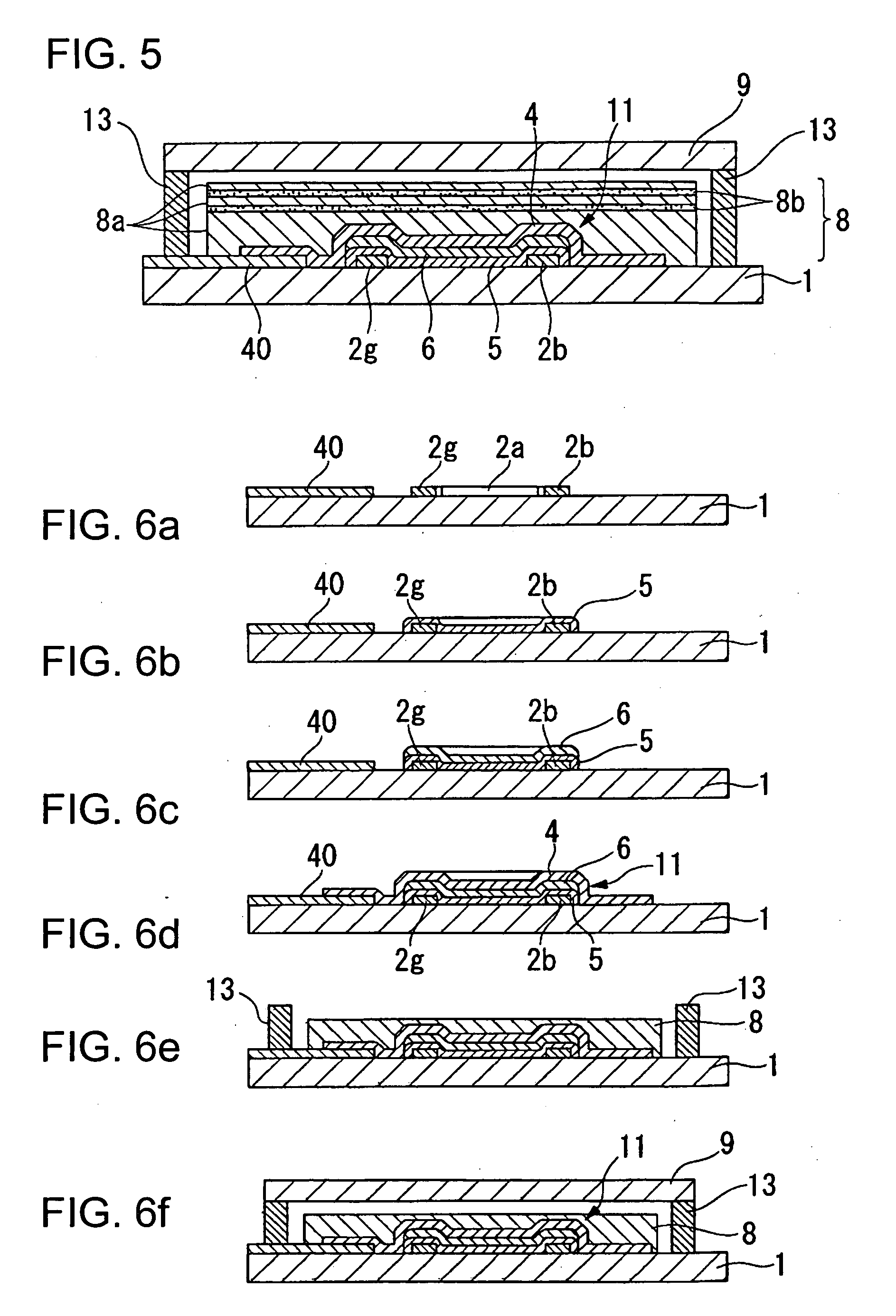

Exercise device

InactiveUS20060116249A1Conveniently engagedTherapy exerciseMuscle exercising devicesEngineeringBody size

Aspects of the present invention involve an exercise device configurable to allow a user to perform various exercises. The exercise devices include an adjustable bench assembly connected with a frame supporting adjustable arm and cable-pulley assemblies providing a user interface with a resistance system. In some embodiments of the invention, the adjustable bench assembly includes a bench seat and a pivotal back support supported on an adjustable bench frame. The exercise devices also utilize various configurations of adjustable arm assemblies that are selectively positionable for numerous exercises and to suit a user's particular body size and shape. Other embodiments of the exercise devices include a resistance system with a transmission supporting a plurality of resistance packs. The transmission allows a user to conveniently engage any number of resistance packs to change the resistance level for a particular exercise.

Owner:NAUTILUS INC

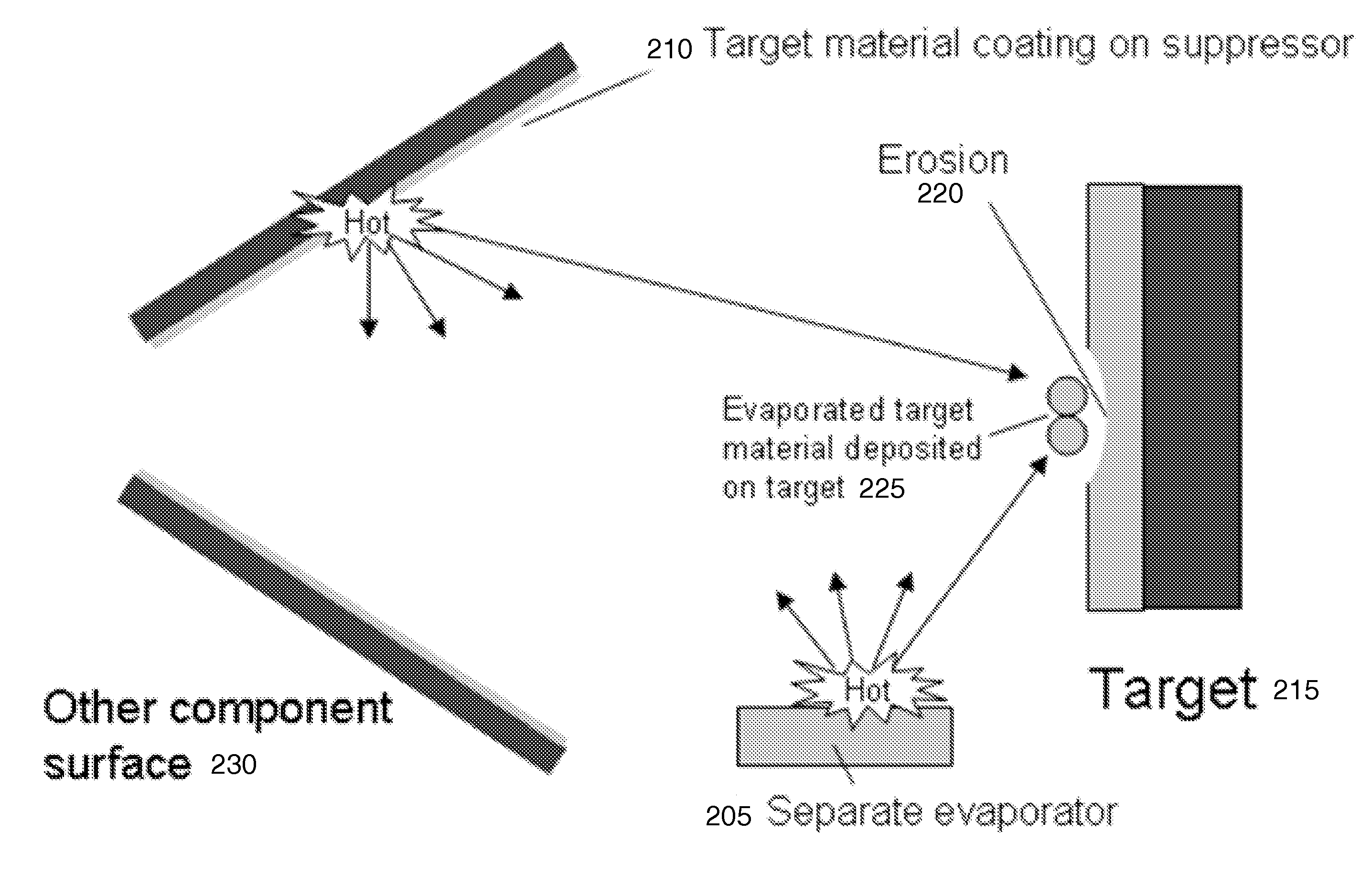

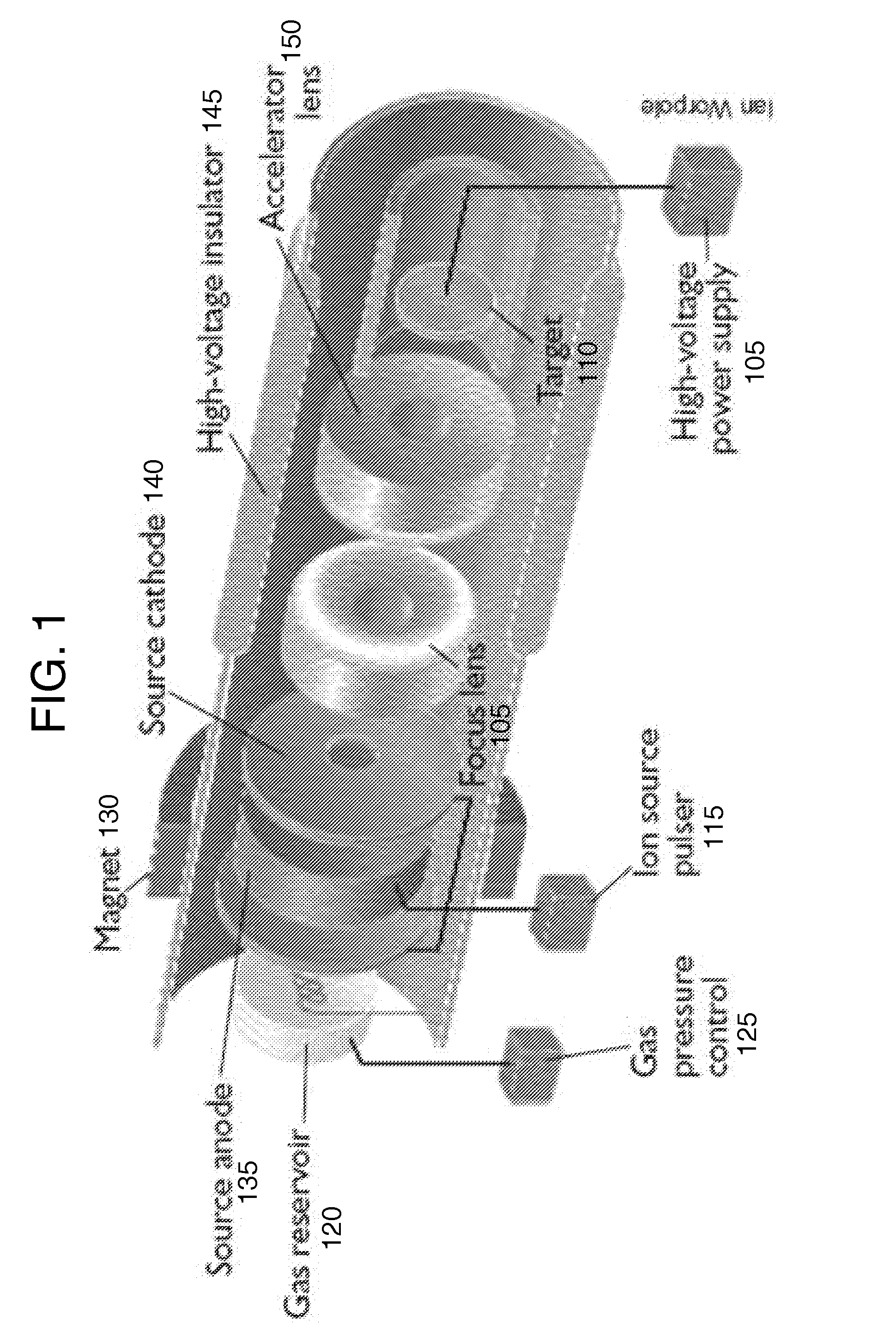

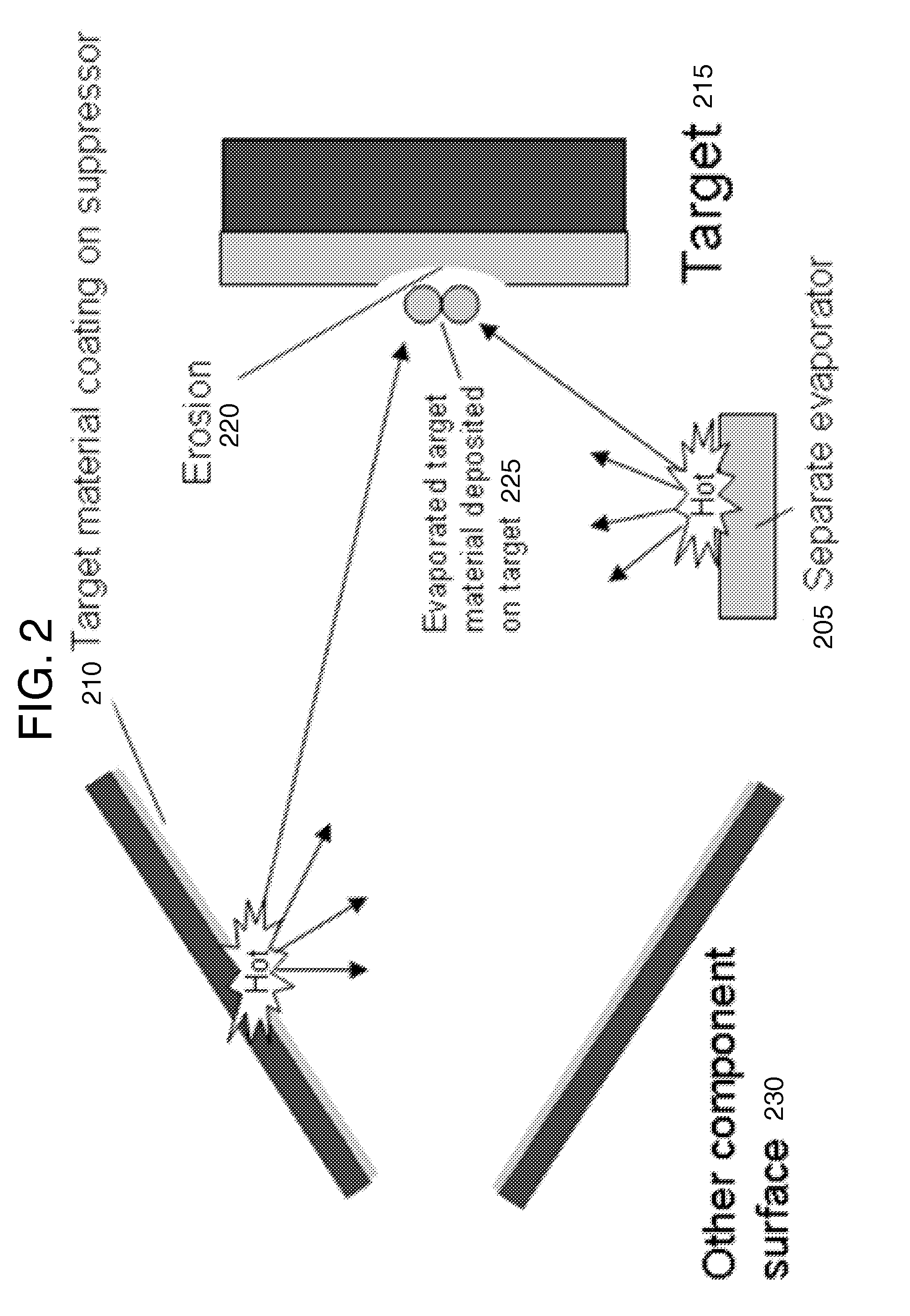

Method and system for in situ depositon and regeneration of high efficiency target materials for long life nuclear reaction devices

ActiveUS20110091000A1Maintain purityMinimize the numberNuclear energy generationDirect voltage acceleratorsNeutron energy spectrumNuclear reaction

Aspects of the invention relate to several methods to deposit and regenerate target materials in neutron generators and similar nuclear reaction devices. In situ deposition and regeneration of a target material reduces tube degradation of the nuclear reaction device and covers impurities on the surface of the target material at the target location. Further aspects of the invention include a method of designing a target to generate neutrons at a high efficiency rate and at a selected neutron energy from a neutron energy spectrum.

Owner:STARFIRE IND LLC

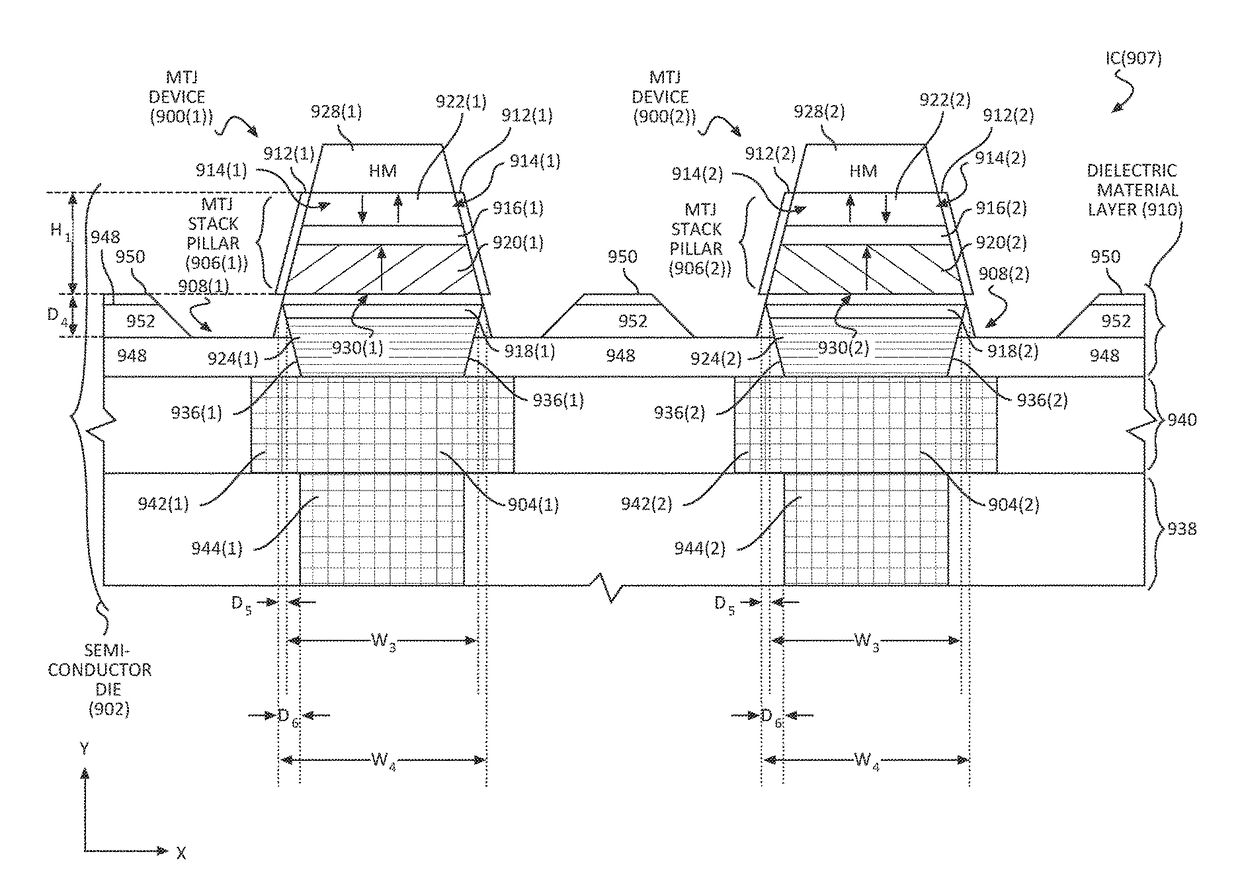

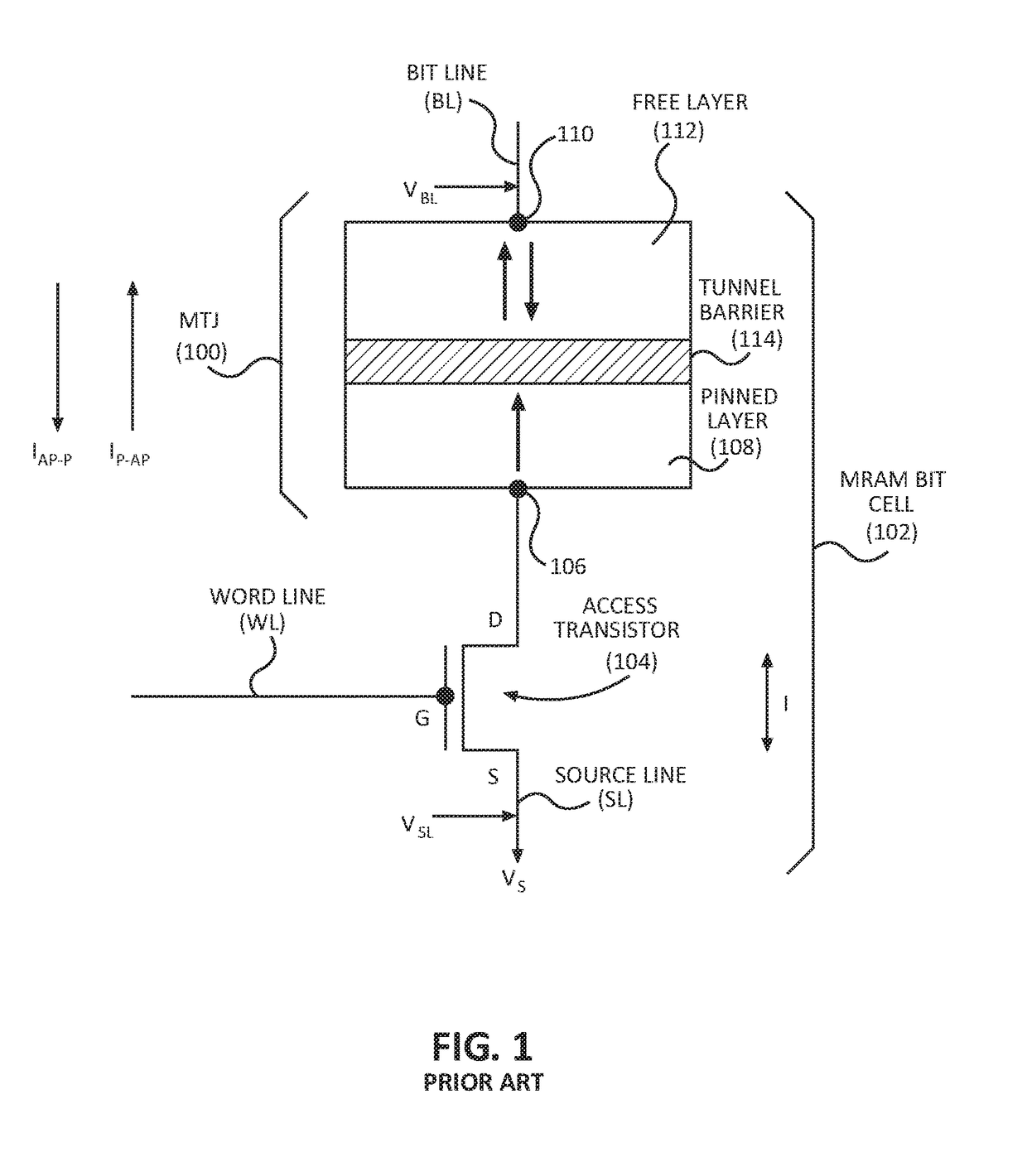

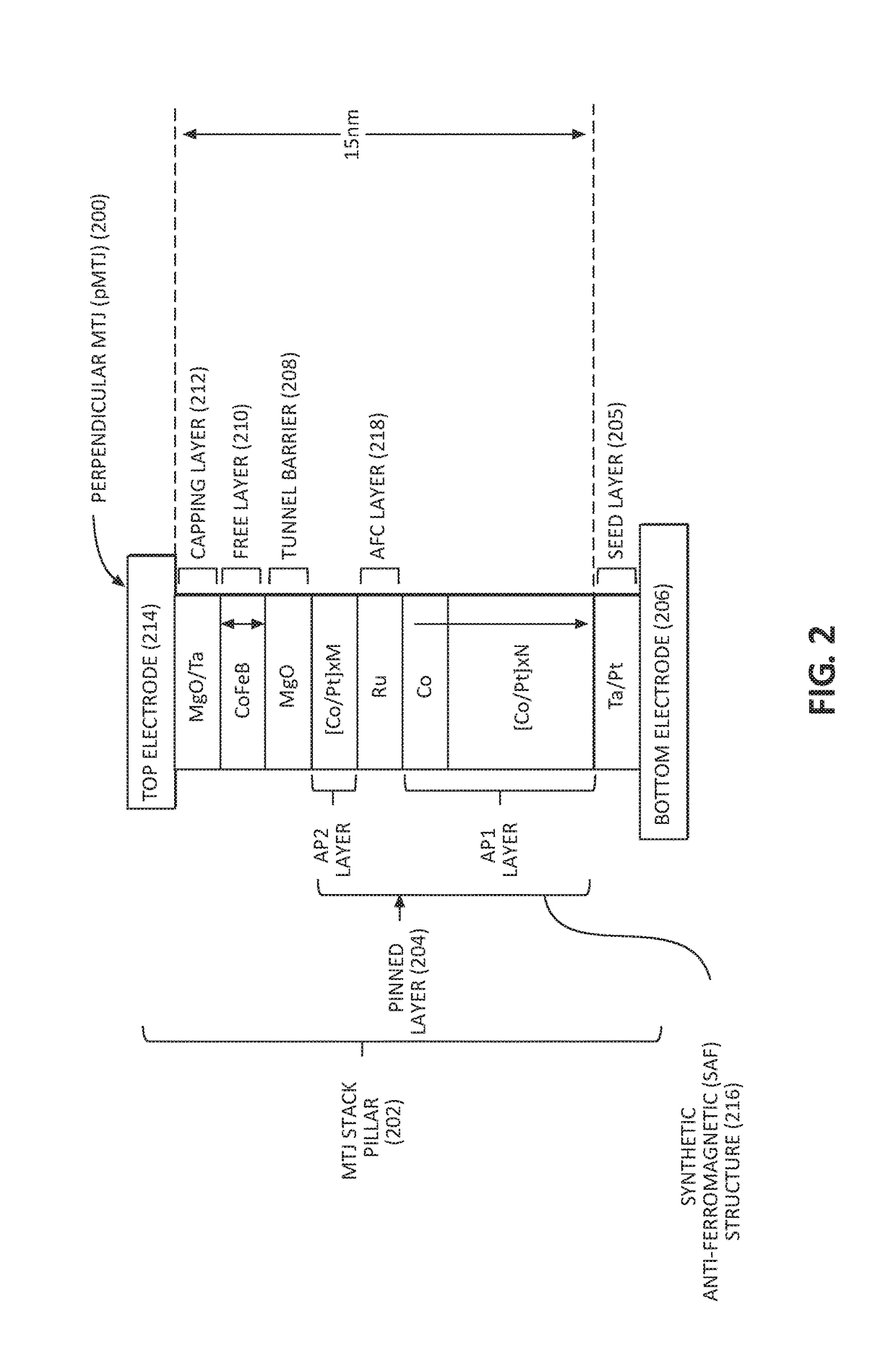

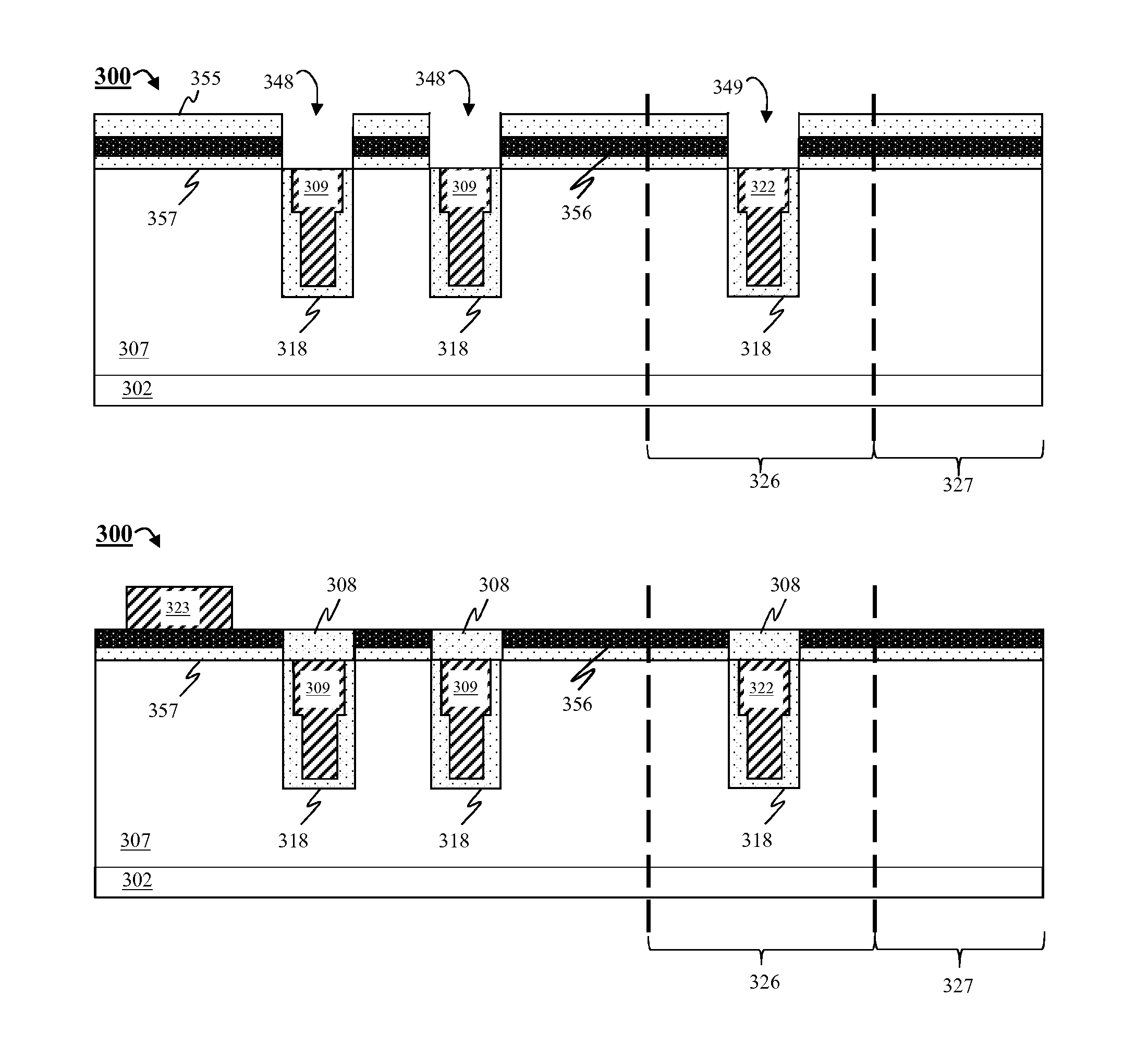

Reducing or avoiding metal deposition from etching magnetic tunnel junction (MTJ) devices, including magnetic random access memory (MRAM) devices

ActiveUS20180040668A1Reducing and avoiding metal depositionReduce and avoid metal redepositionMagnetic-field-controlled resistorsSolid-state devicesStatic random-access memoryRandom access memory

Aspects disclosed include reducing or avoiding metal deposition from etching magnetic tunnel junction (MTJ) devices. In one example, a width of a bottom electrode of an MTJ device is provided to be less than a width of the MTJ stack of the MTJ device. In this manner, etching of the bottom electrode may be reduced or avoided to reduce or avoid metal redeposition as a result of over-etching the MTJ device to avoid horizontal shorts between an adjacent device(s). In another example, a seed layer is embedded in a bottom electrode of the MTJ device. In this manner, the MTJ stack is reduced in height to reduce or avoid metal redeposition as a result of over-etching the MTJ device. In another example, an MTJ device includes an embedded seed layer in a bottom electrode which also has a width less than a width of the MTJ stack.

Owner:QUALCOMM INC

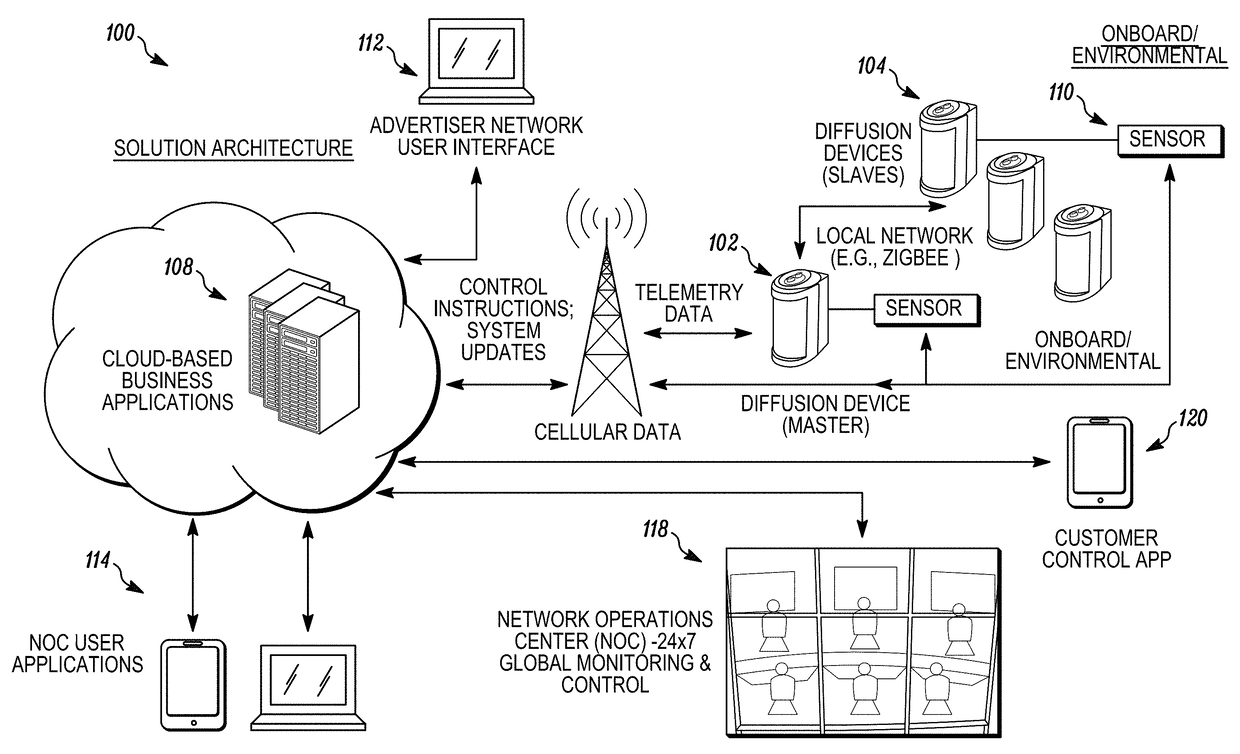

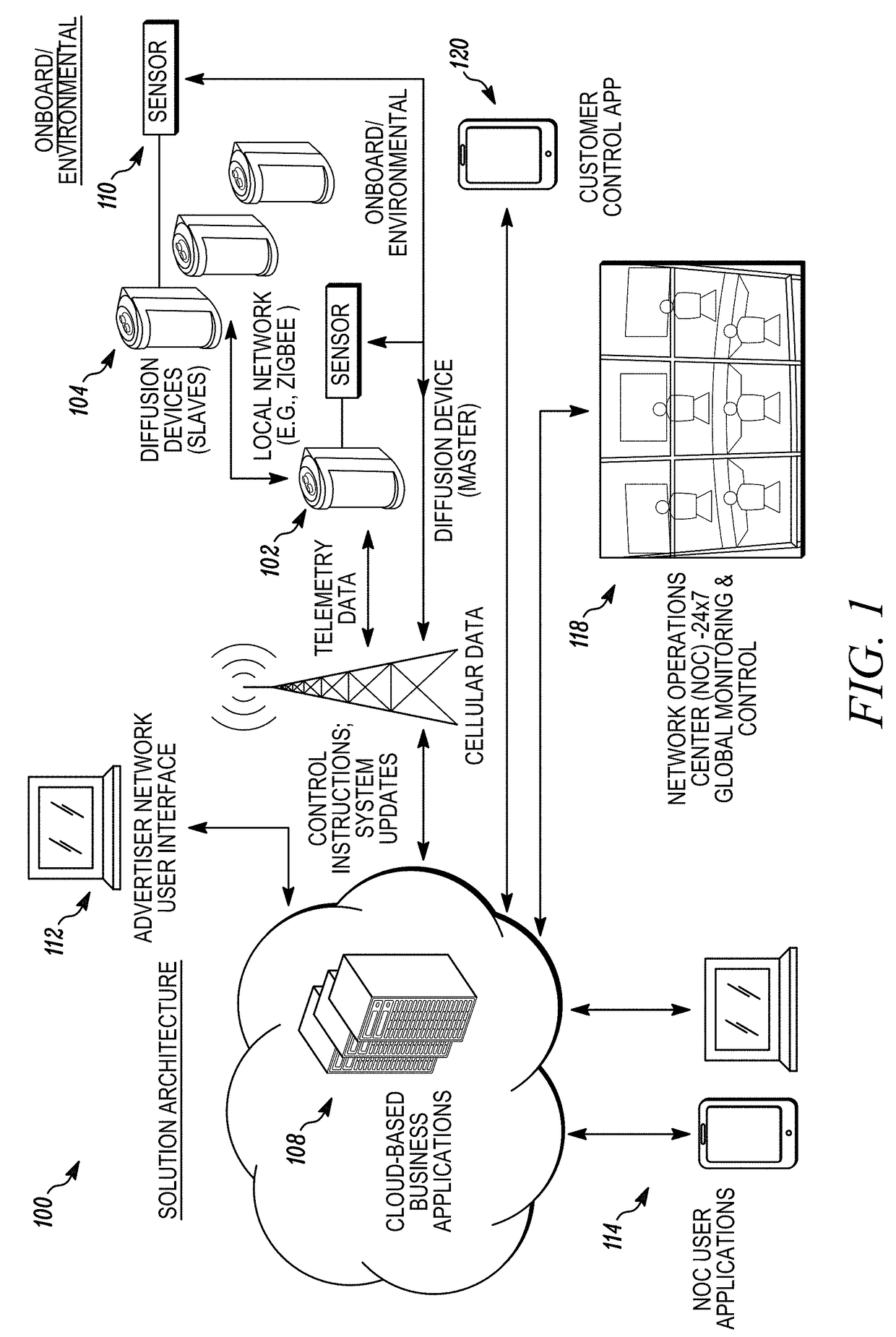

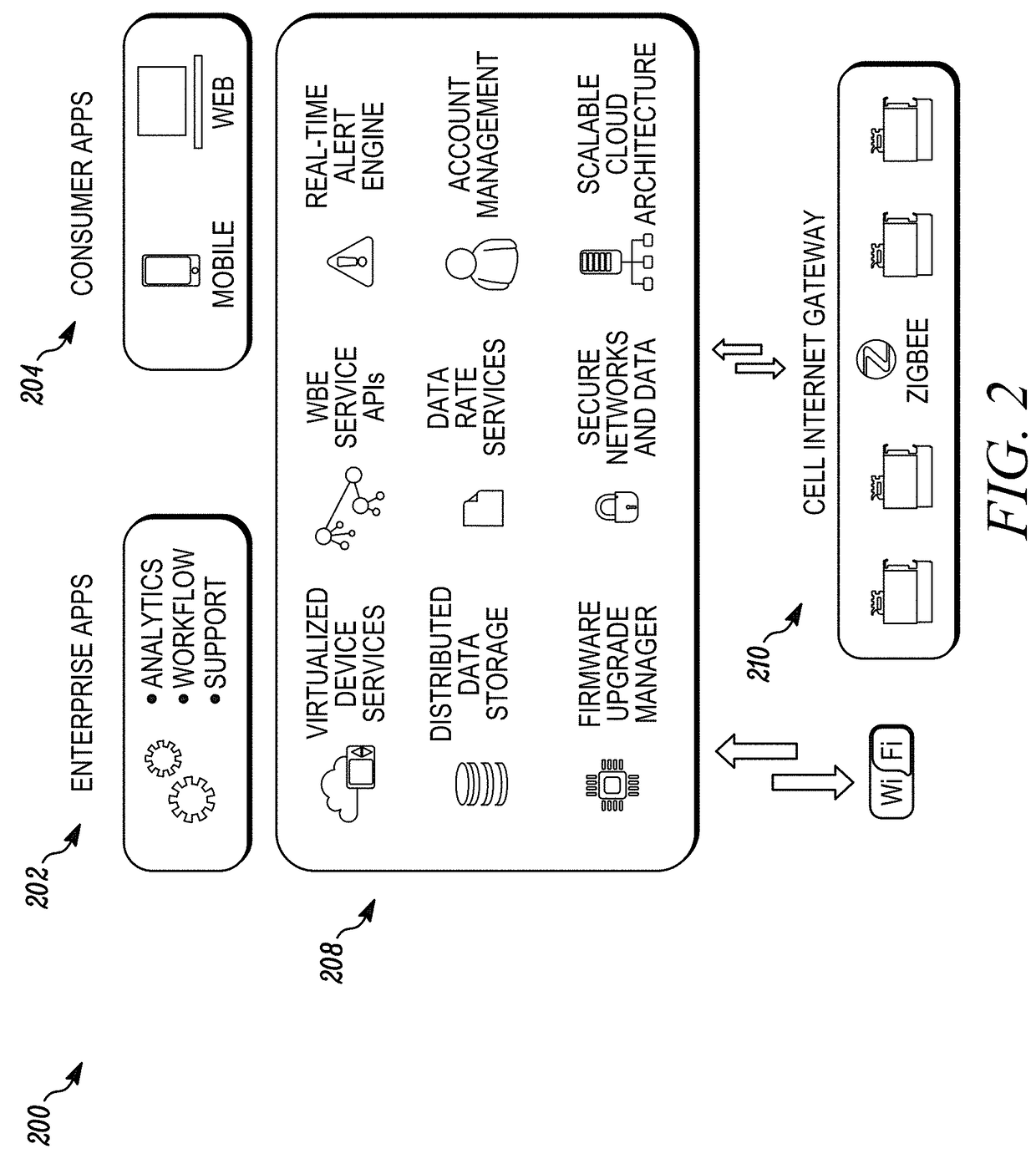

Method and system of a networked scent diffusion device

Aspects of the present disclosure include a method of managing scent in an environment, which includes disposing at least one scent diffusion device within an environment, wherein the at least one scent diffusion device comprises a communications facility that enables transmitting signals to and receiving signals from a remote computer, receiving at least one target value of a scent parameter for the environment at the remote computer, and controlling, via the remote computer, diffusion of a liquid from a source of the liquid in fluid communication with the at least one scent diffusion device to achieve the target value of the scent parameter. Controlling a diffusion rate of the liquid includes altering at least one of a voltage and a duty cycle applied to at least one component of the diffusion device.

Owner:SCENTBRIDGE HLDG LLC

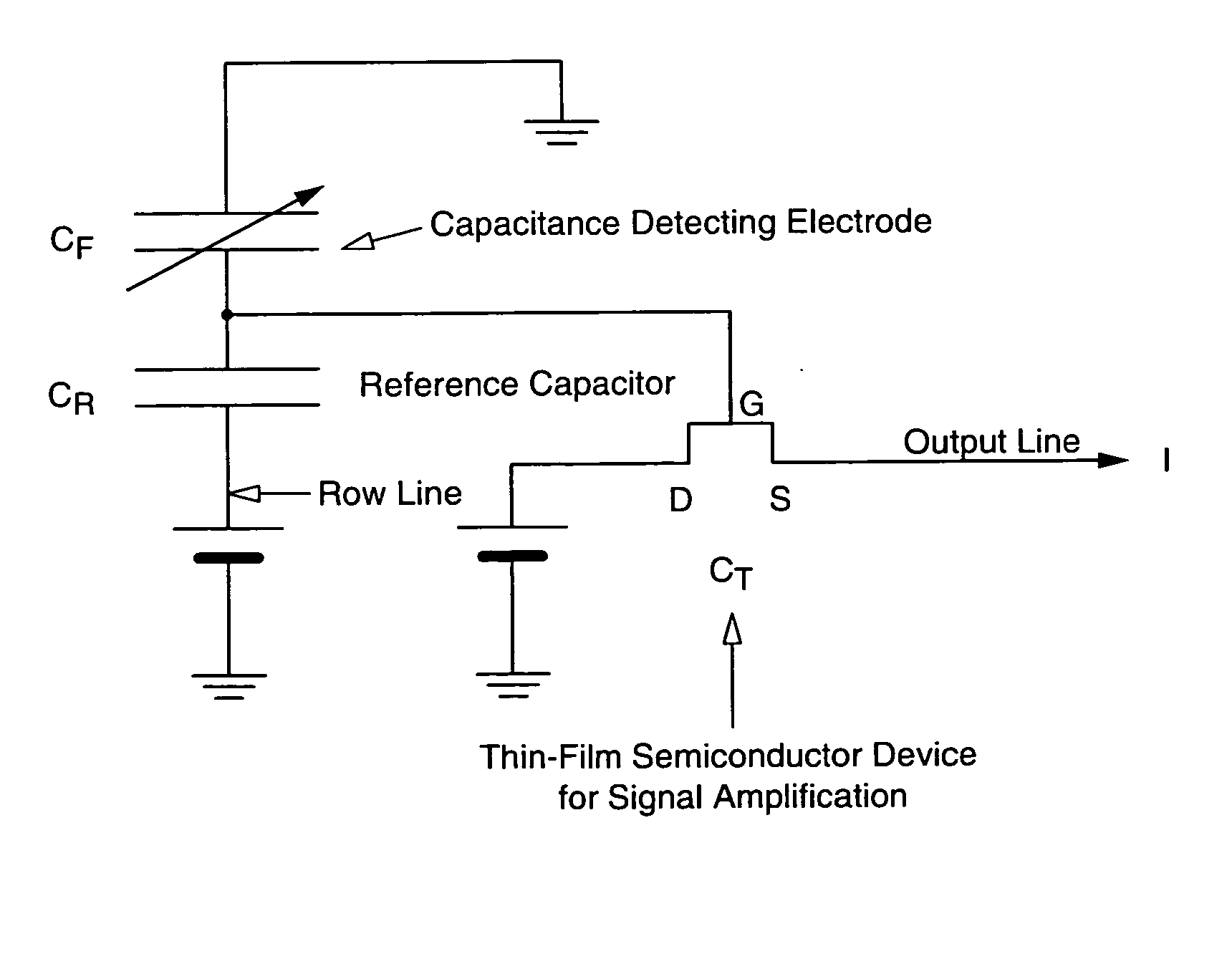

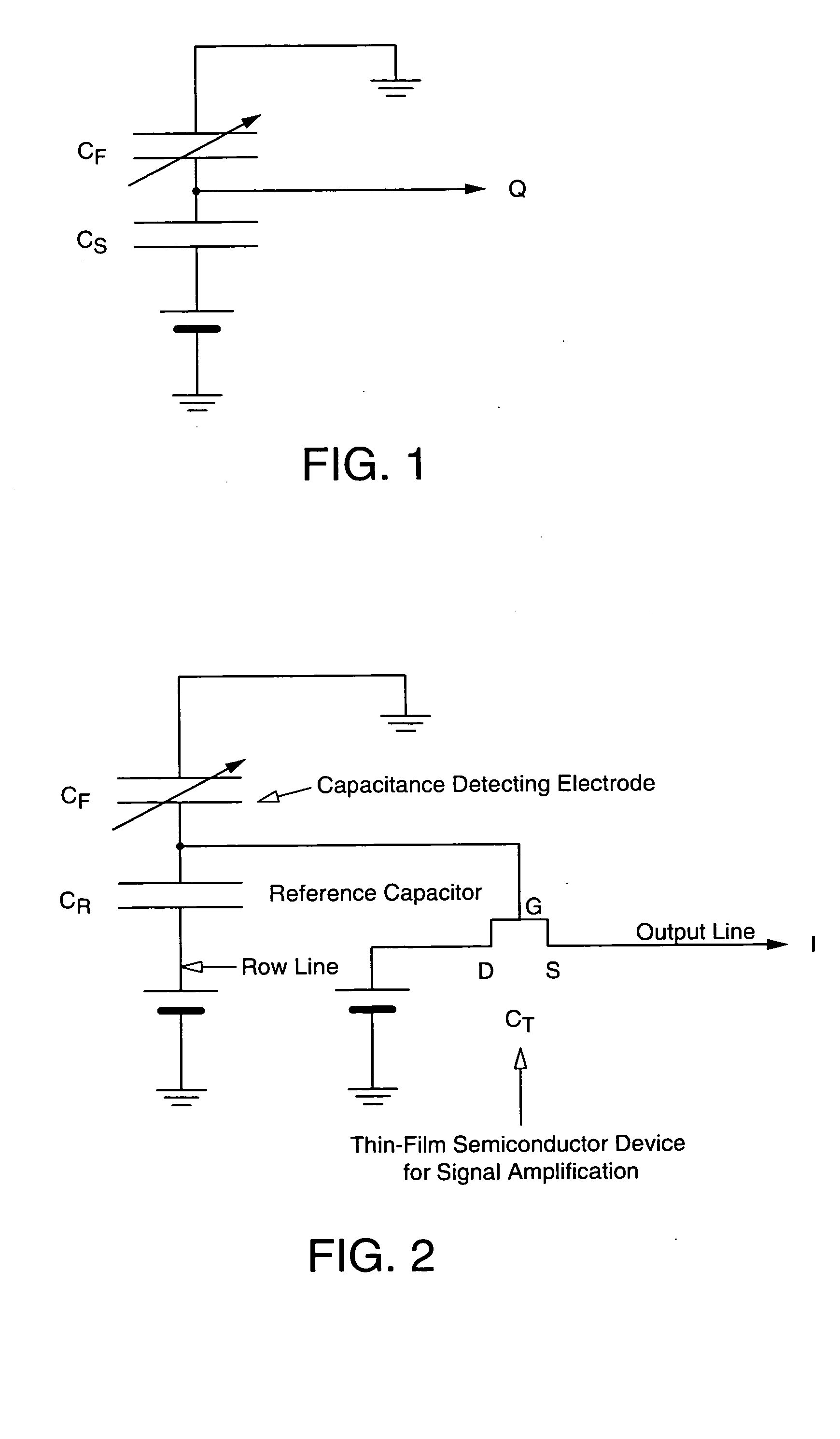

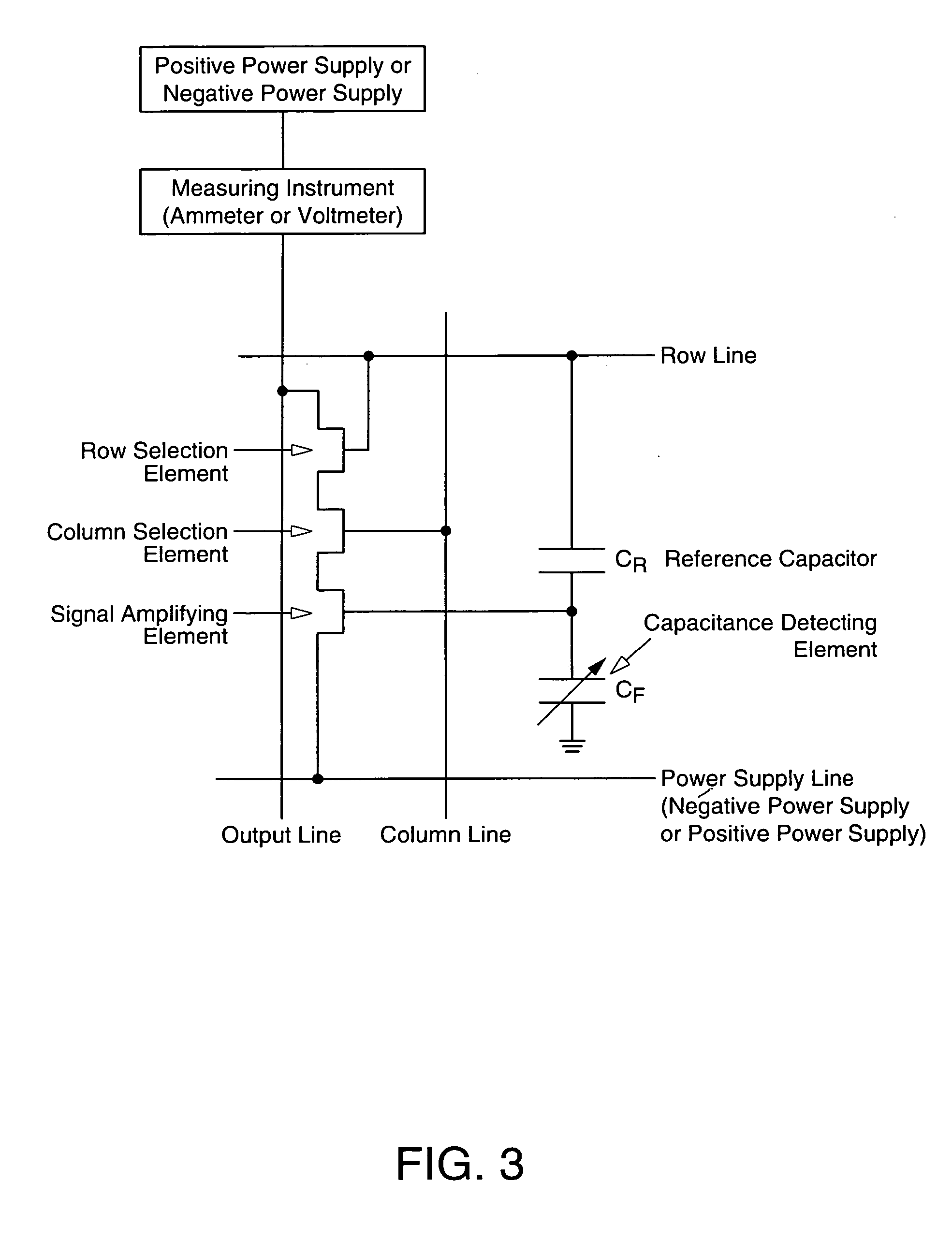

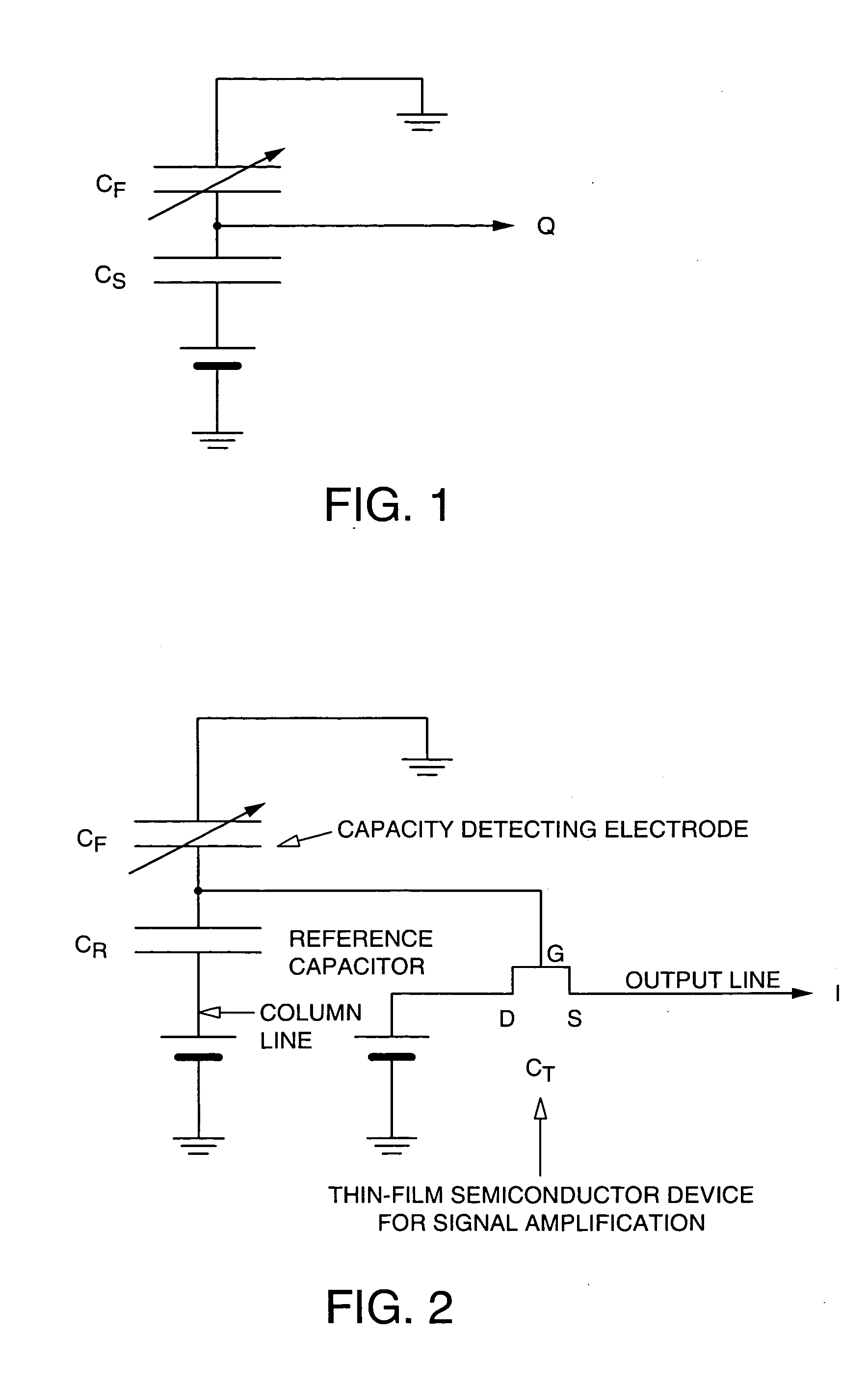

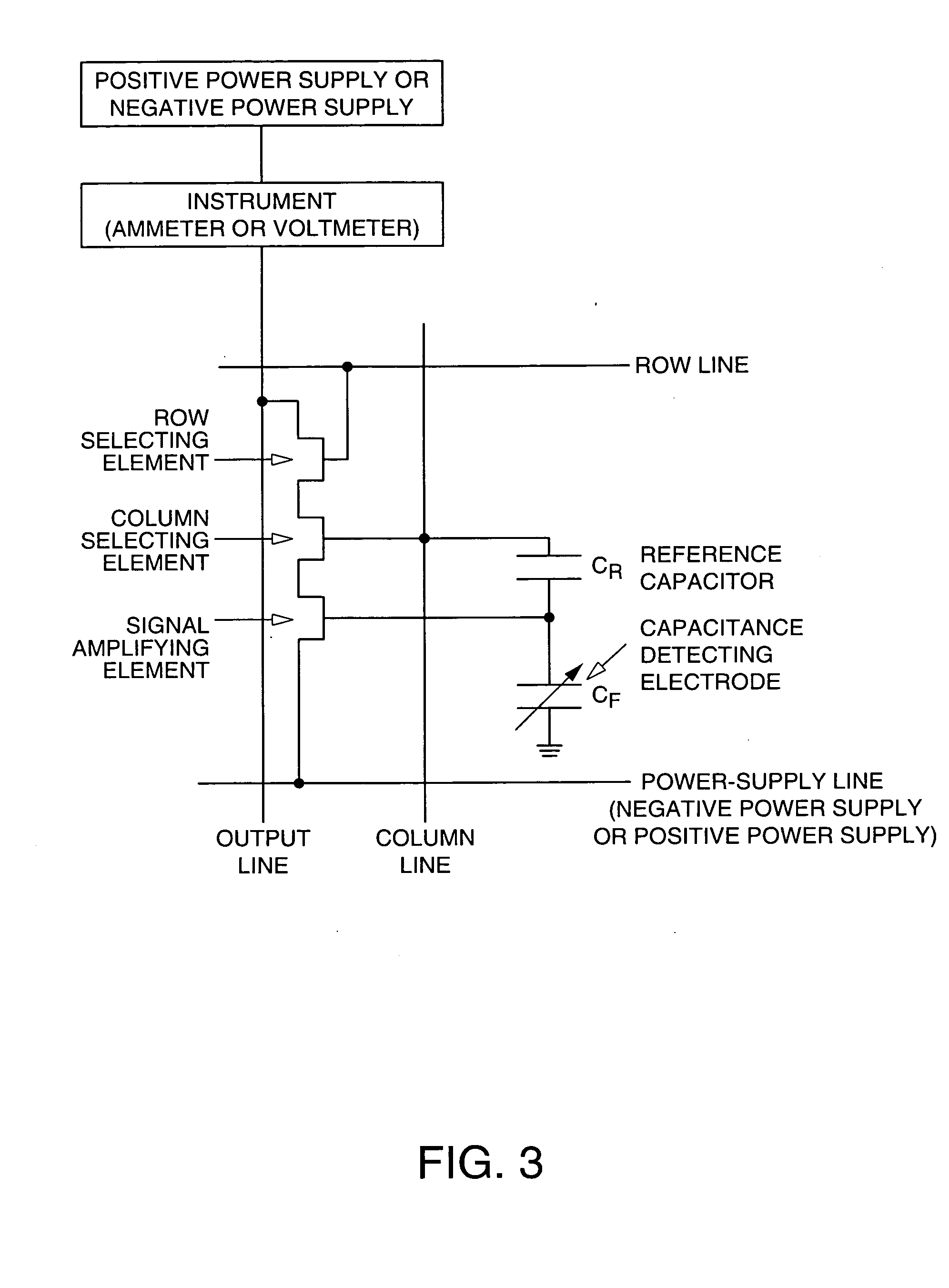

Electrostatic capacitance detection device

ActiveUS20050077911A1Easy to optimizeReduce expenditureTransistorResistance/reactance/impedenceCapacitanceEngineering

Aspects of the invention can provide an electrostatic capacitance detection device having M number of row lines and N number of column lines arranged in a matrix of M rows and N columns, and an electrostatic capacitance detection element formed at the intersection thereof. The electrostatic capacitance detection element can include a signal detection element, a signal amplifying element and a column selection element and a row selection element. The signal detection element can include a capacitance detecting electrode, a capacitance detecting dielectric layer, and a reference capacitor. One of a pair of electrodes in the reference capacitor is coupled to the row line. Accordingly, the invention can achieve a superior electrostatic capacitance detection device.

Owner:138 EAST LCD ADVANCEMENTS LTD

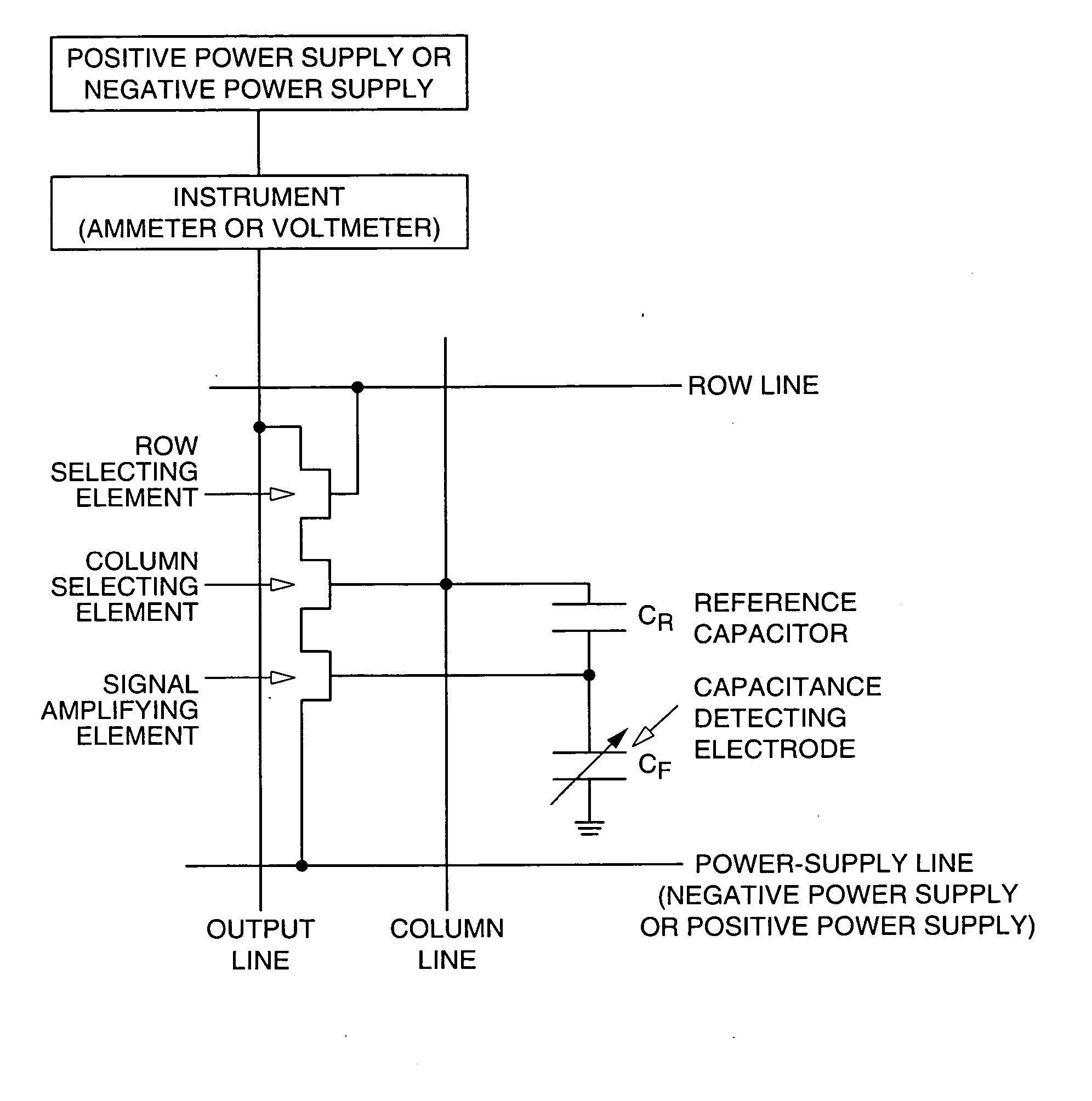

Electrostatic capacitance detection device

ActiveUS20050078856A1Guaranteed uptimeReduce expenditureResistance/reactance/impedencePerson identificationCapacitanceDevice form

Aspects of the invention provide a superior electrostatic capacitance detecting device. The electrostatic capacitance detection device can include M number of row lines, N number of column lines, and electrostatic capacitance detecting devices formed at intersections of these lines. The electrostatic capacitance detecting element can include a signal detection element, a signal amplifying element, a column selecting element, and a row selecting element, and the signal detection element can include a capacitance detecting electrode, a capacitance detecting dielectric layer, and a reference capacitor, and one electrode of the reference capacitor connects to a column line.

Owner:138 EAST LCD ADVANCEMENTS LTD

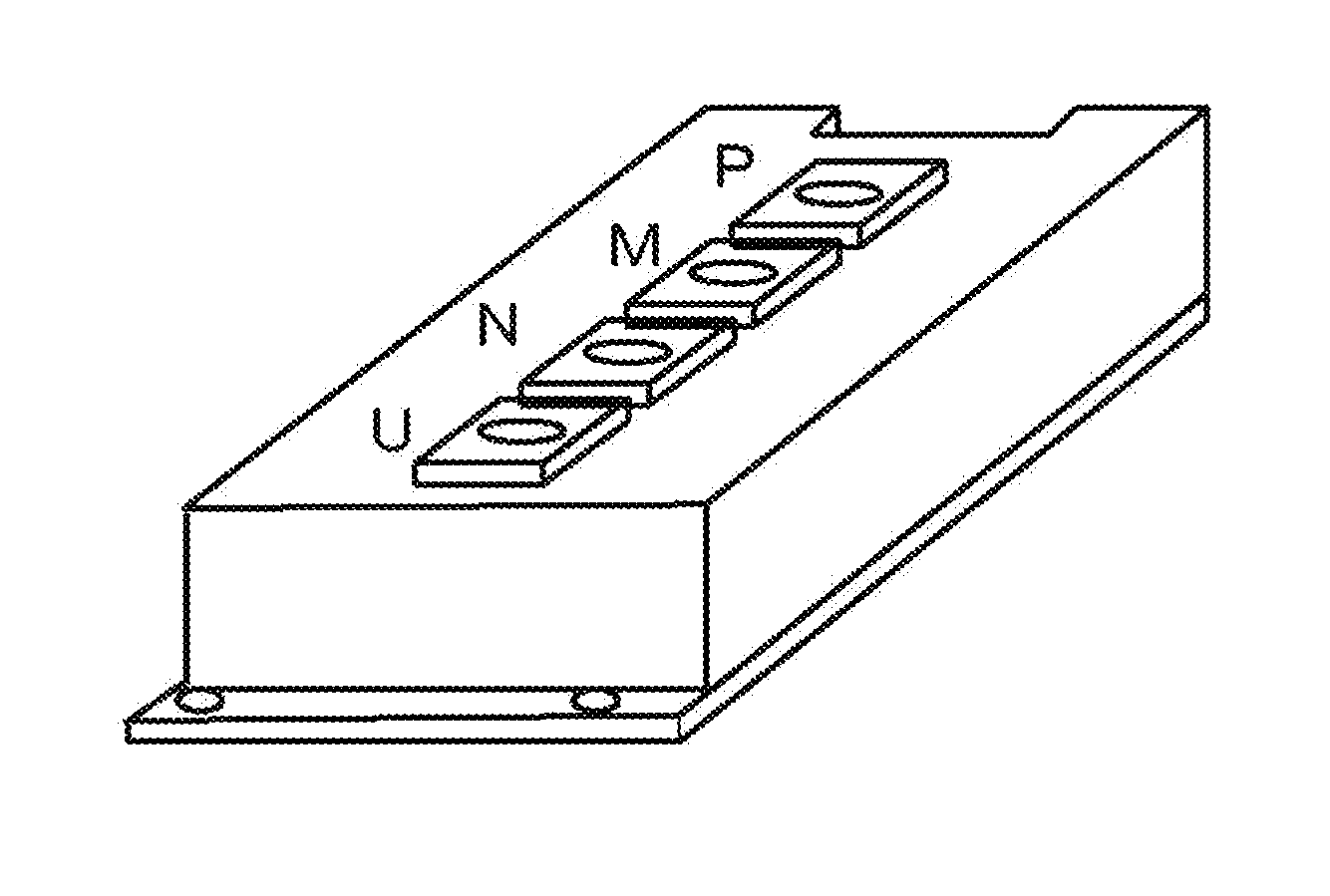

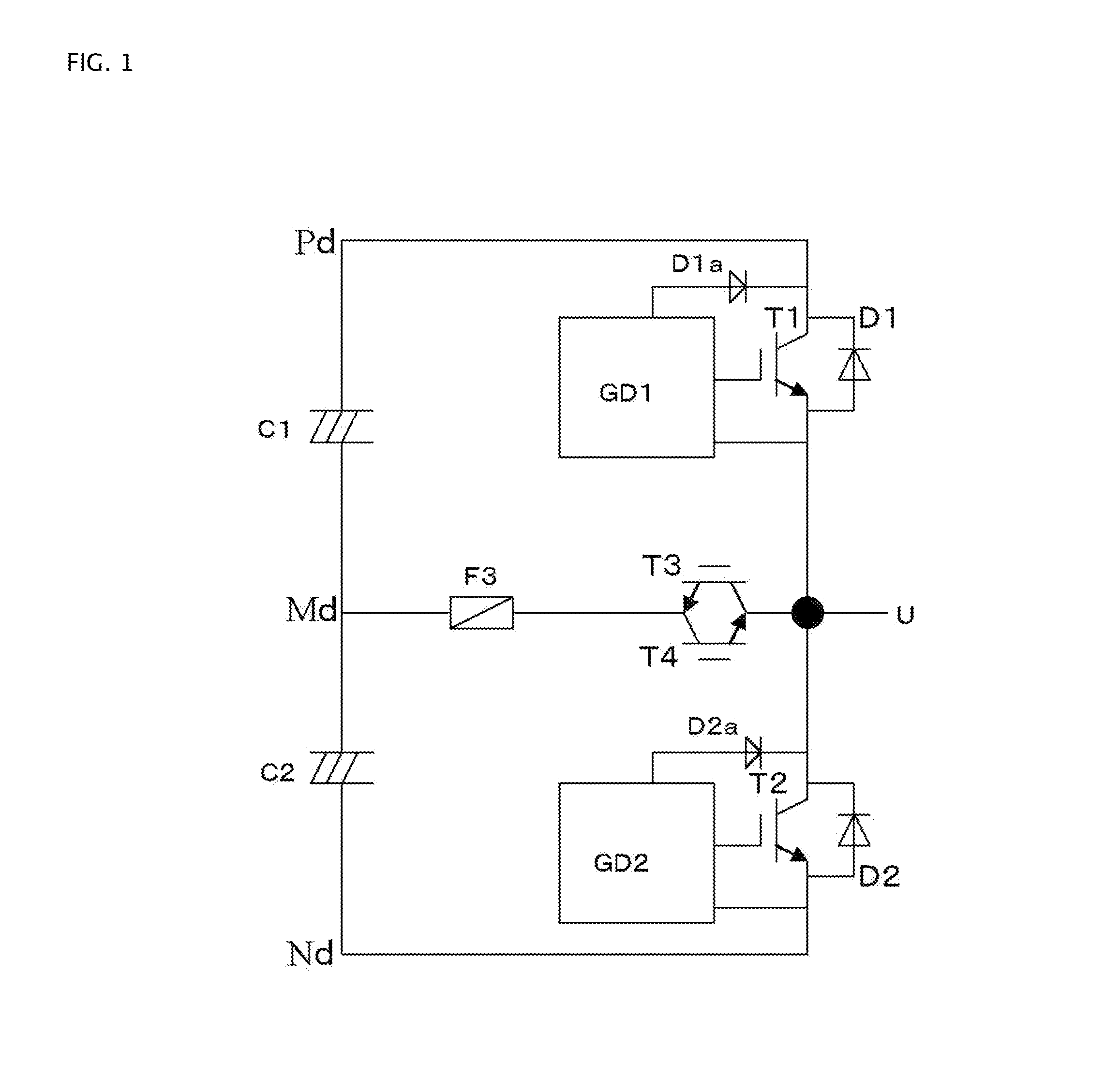

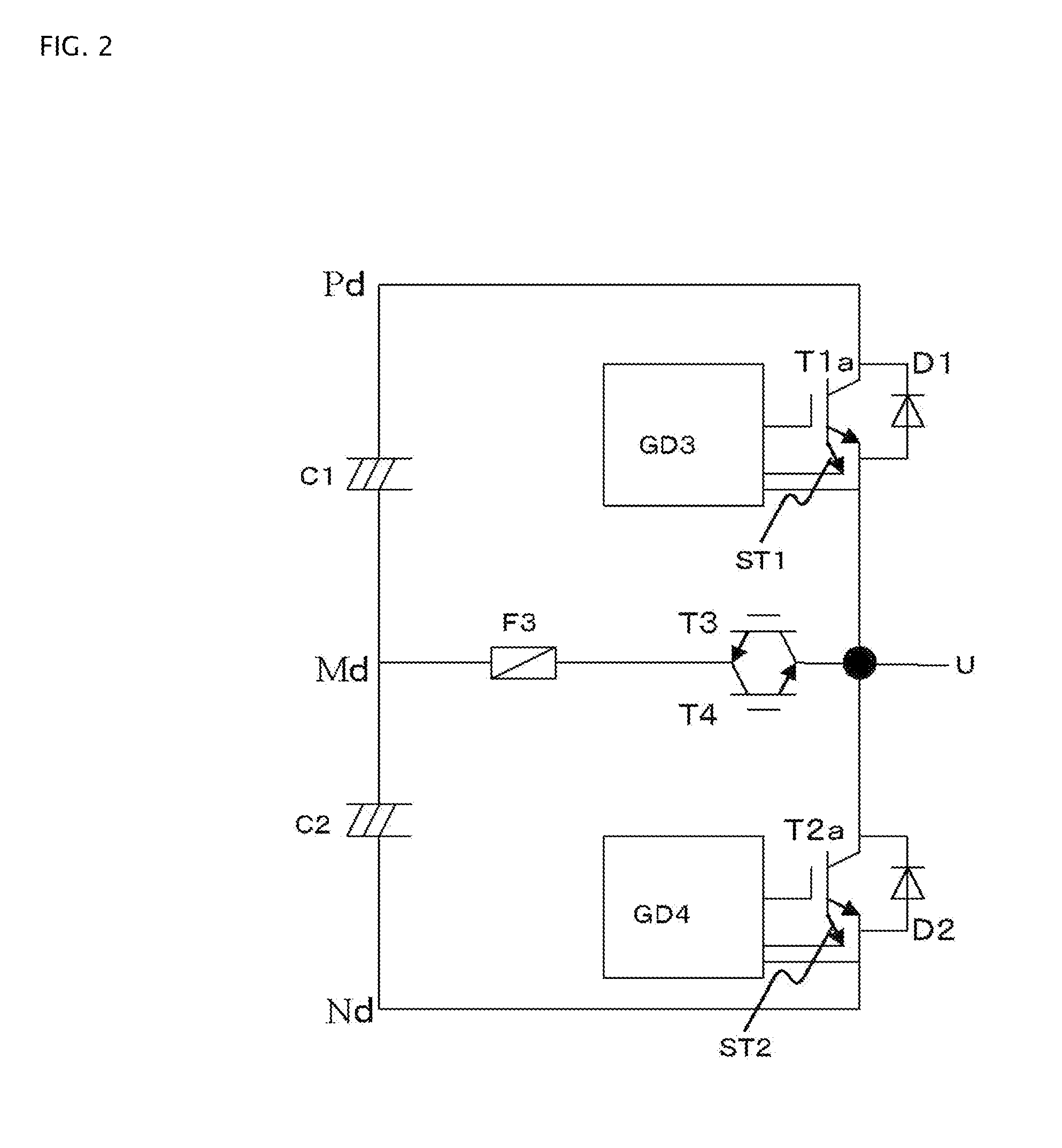

Three level power converting device

InactiveUS20120018777A1Suppress surge voltageReliable protection functionAc-dc conversionElectronic switchingThree levelDriver circuit

Aspects of the invention are directed to a three-level power converter that has, as one phase, a bidirectional switching element connected to the series connection point of a series circuit of a first insulated gate bi-polar transistor (“IGBT”) and second IGBT and an intermediate electrode of a direct current power supply. Also included is a fuse connected between the bidirectional switching element and the intermediate electrode of the direct current power supply, and an overcurrent shutdown unit provided in each gate drive circuit of the first and second IGBTs, are provided as protection from a power supply short circuit phenomenon occurring in the event of a short circuit failure of any of the IGBTs or diodes.

Owner:FUJI ELECTRIC CO LTD

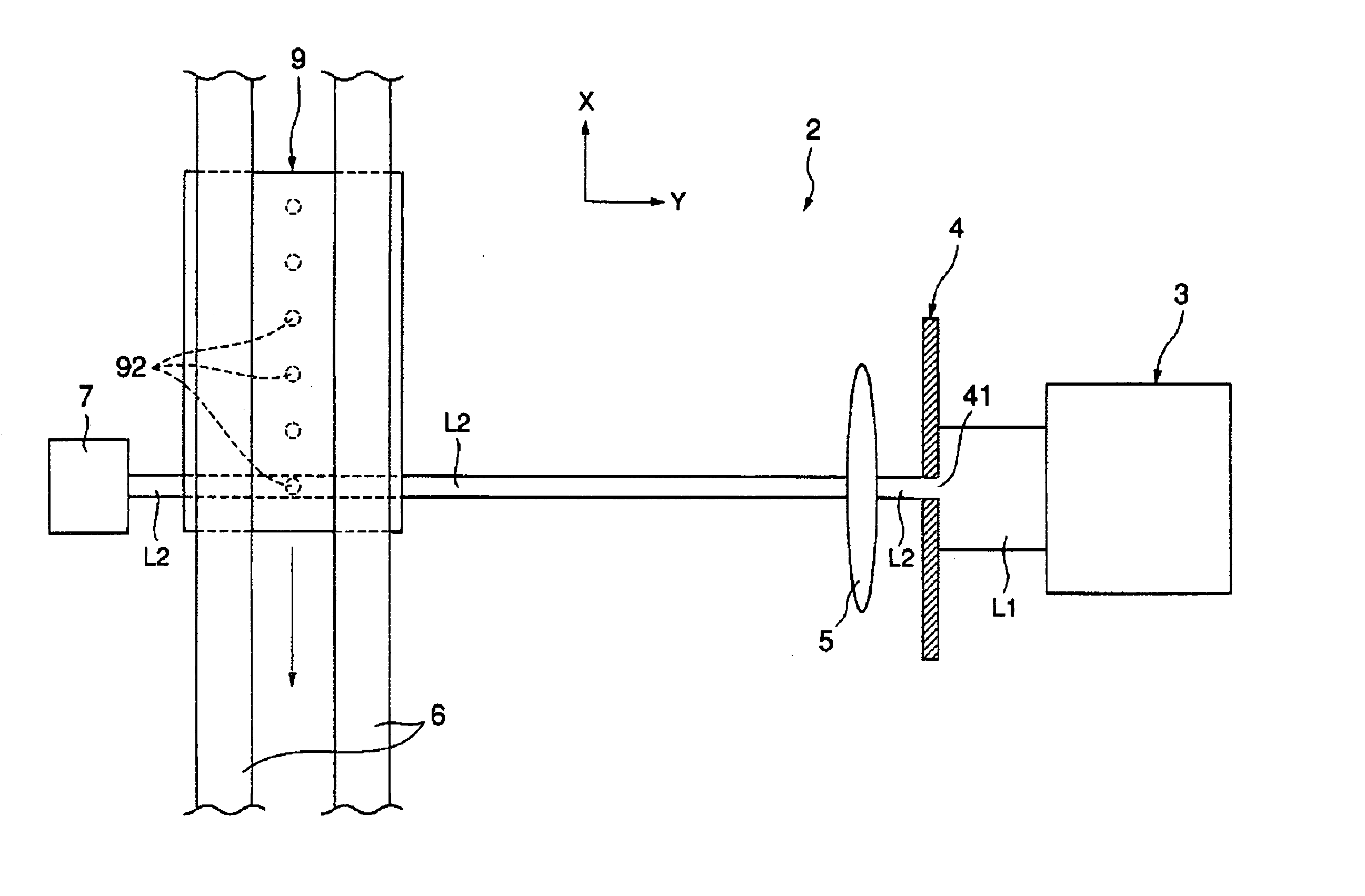

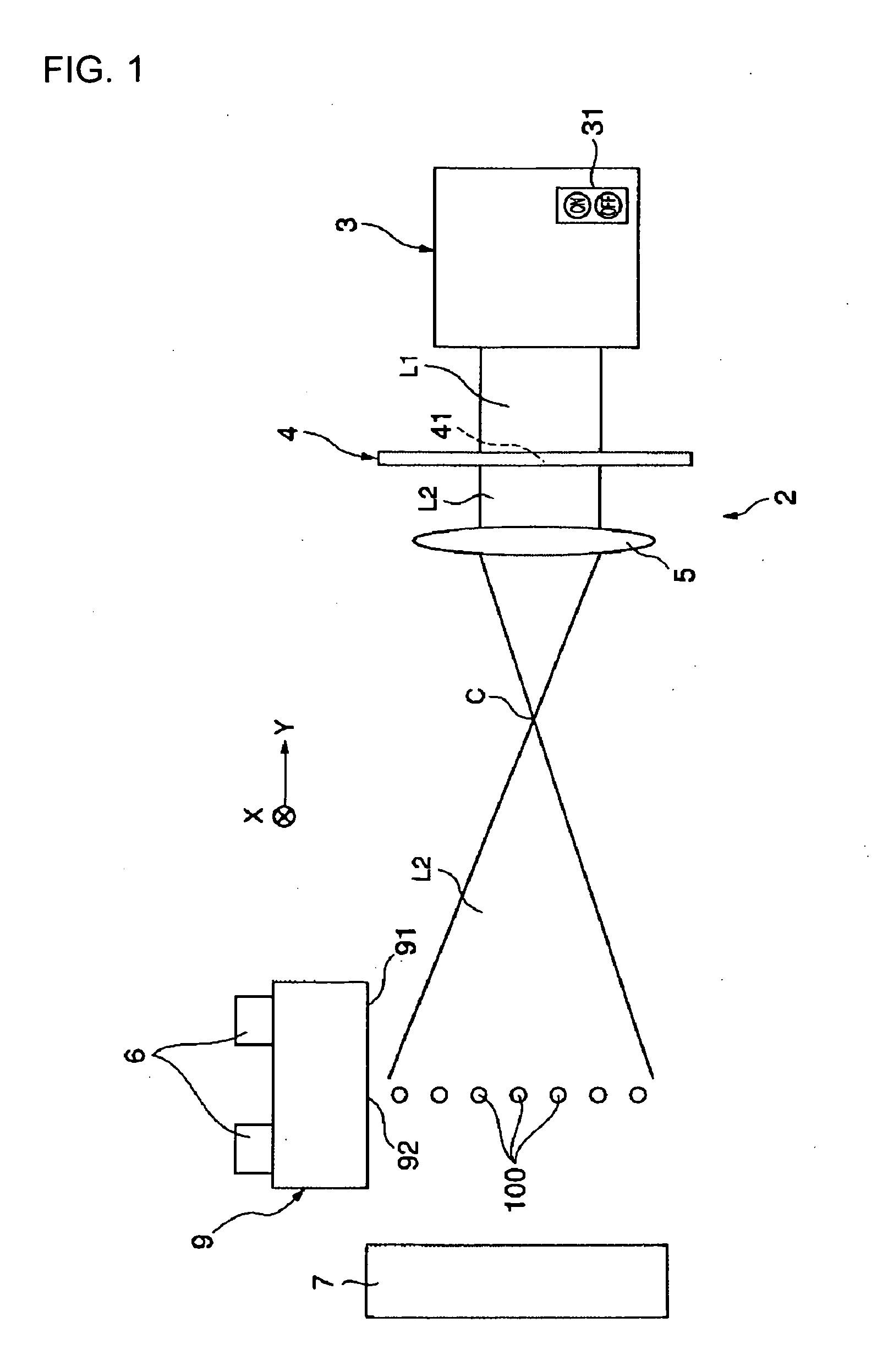

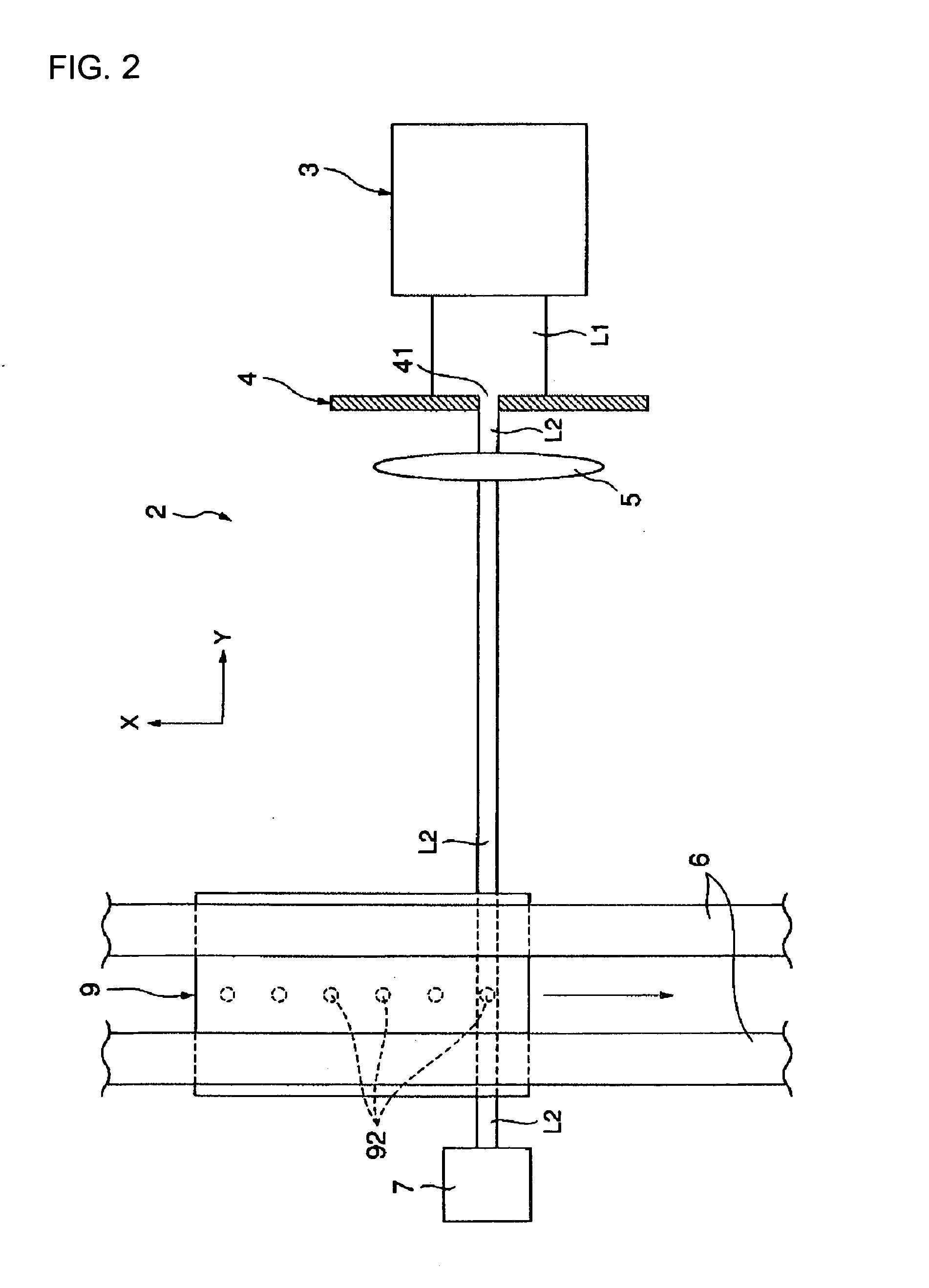

Method for visually recognizing a droplet, droplet discharge head inspection device, and droplet discharge device

InactiveUS20050078138A1Easy to identifyEasy to adjust the widthOther printing apparatusLight beamEngineering

Aspects of the invention can provide a method for visually recognizing a droplet, a droplet discharge head inspection device, and a droplet discharge device that are capable of easily visually recognizing an airborne droplet discharged from a nozzle hole of a droplet discharge head. The droplet discharge head inspection device can provide visual recognition of an airborne droplet discharged from a nozzle hole included in a droplet discharge head, and includes a laser light irradiation device that irradiates laser light and a plate member having a slit through which the laser light passes. The laser light is made pass through the slit so as to be shaped into flat-shaped light beams, that is, laser light. With the laser light laid out in parallel with a course of the droplet, the course is irradiated with the laser light. This makes it possible to illuminate and easily visually recognize the airborne droplet.

Owner:SEIKO EPSON CORP

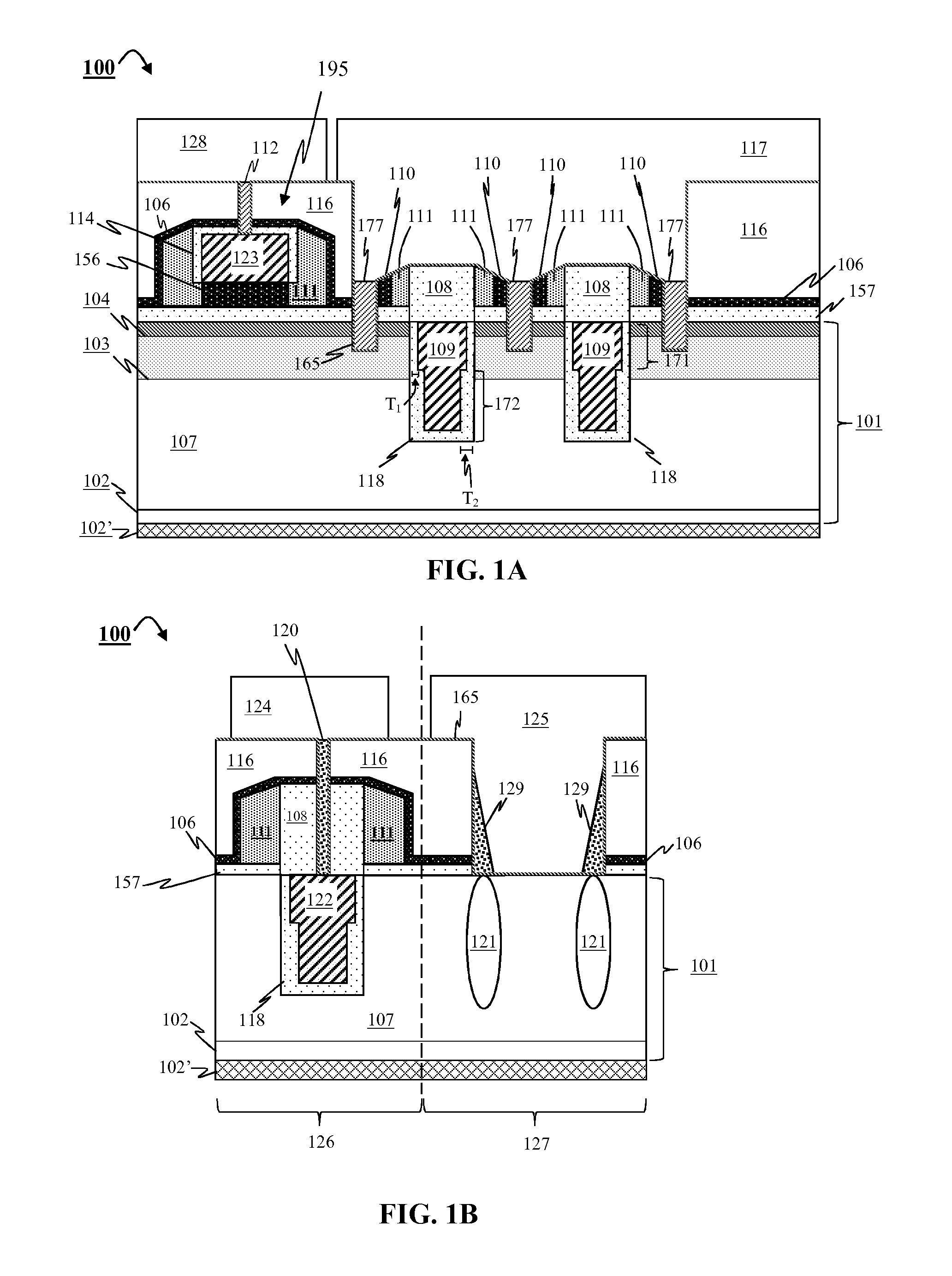

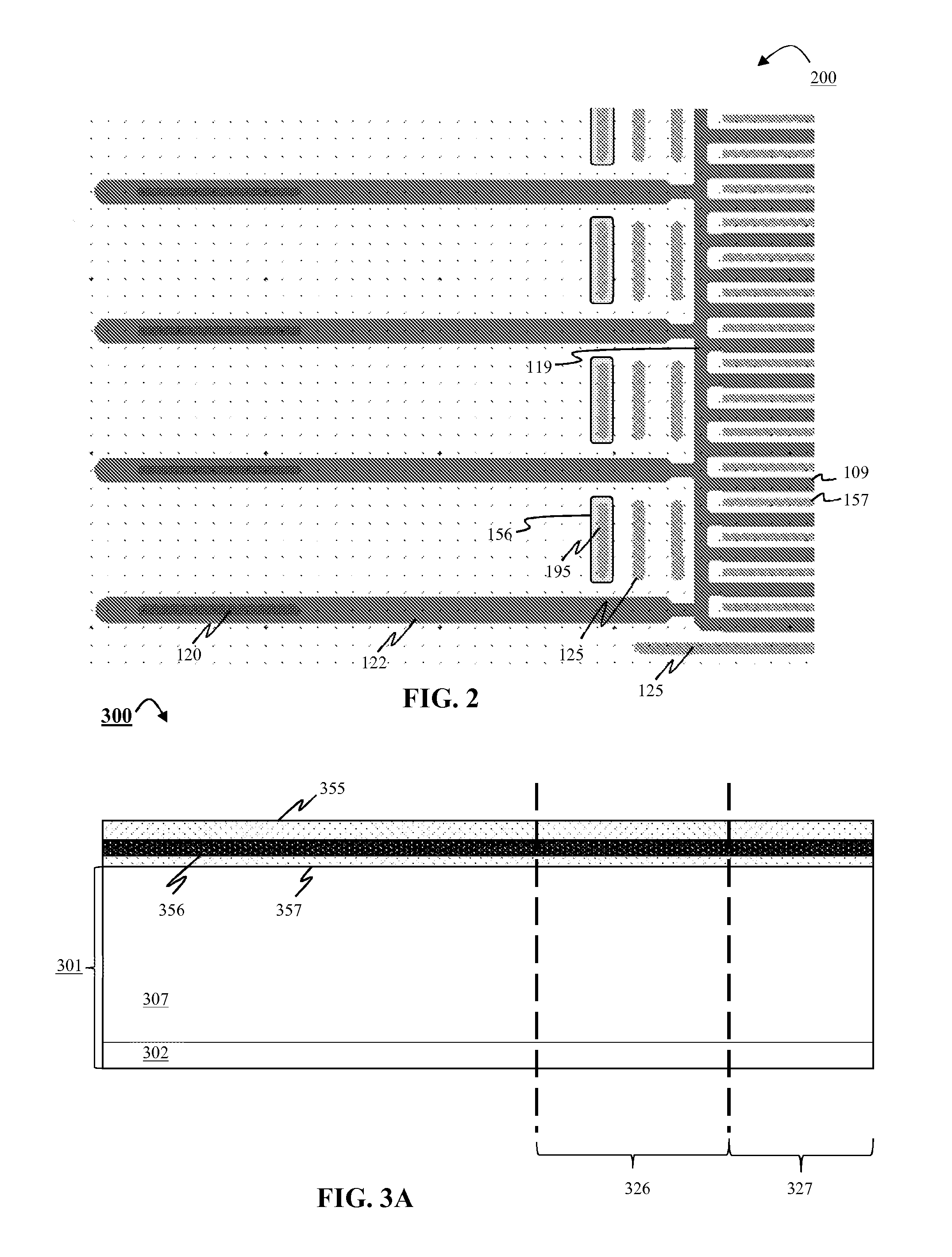

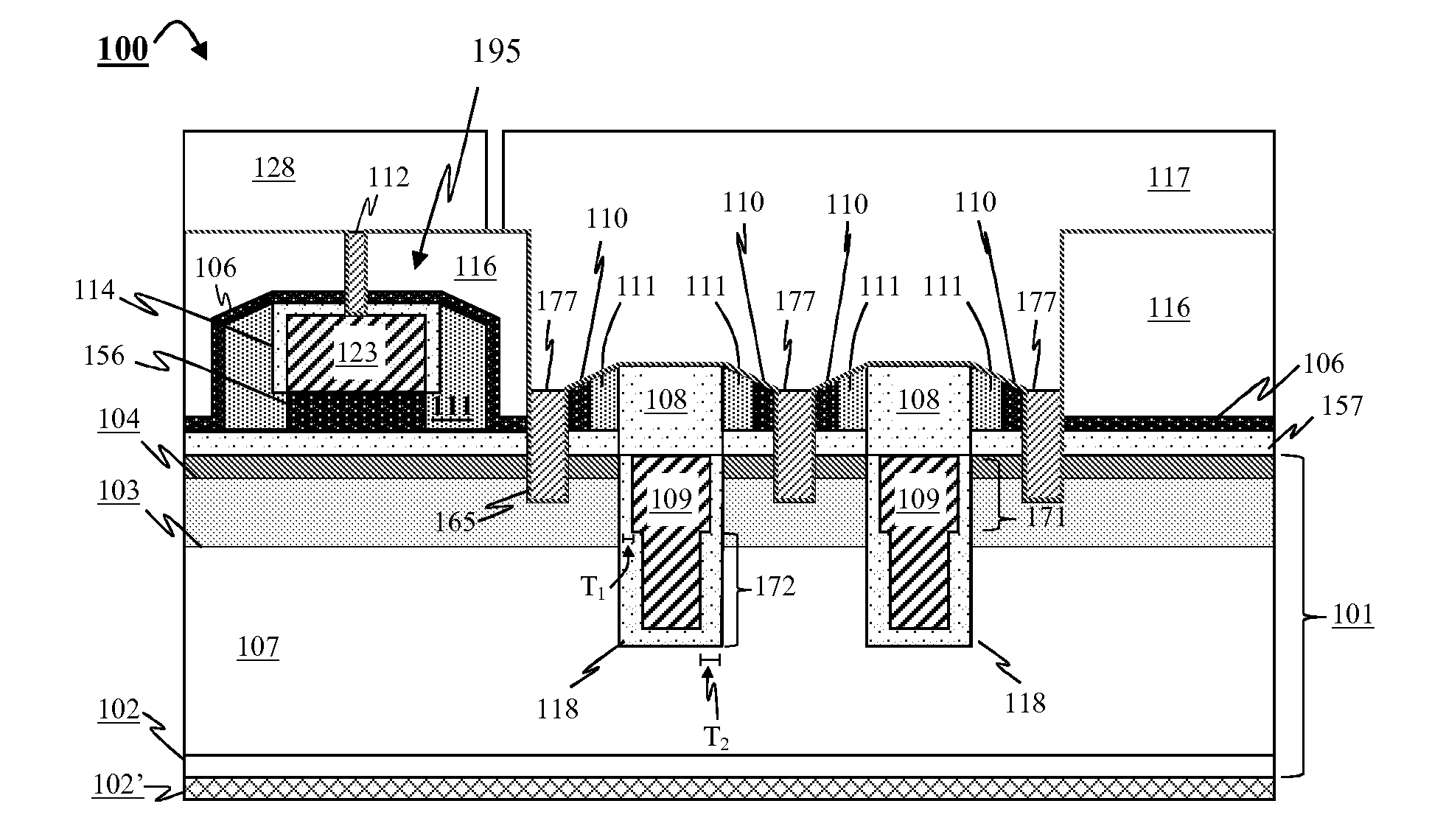

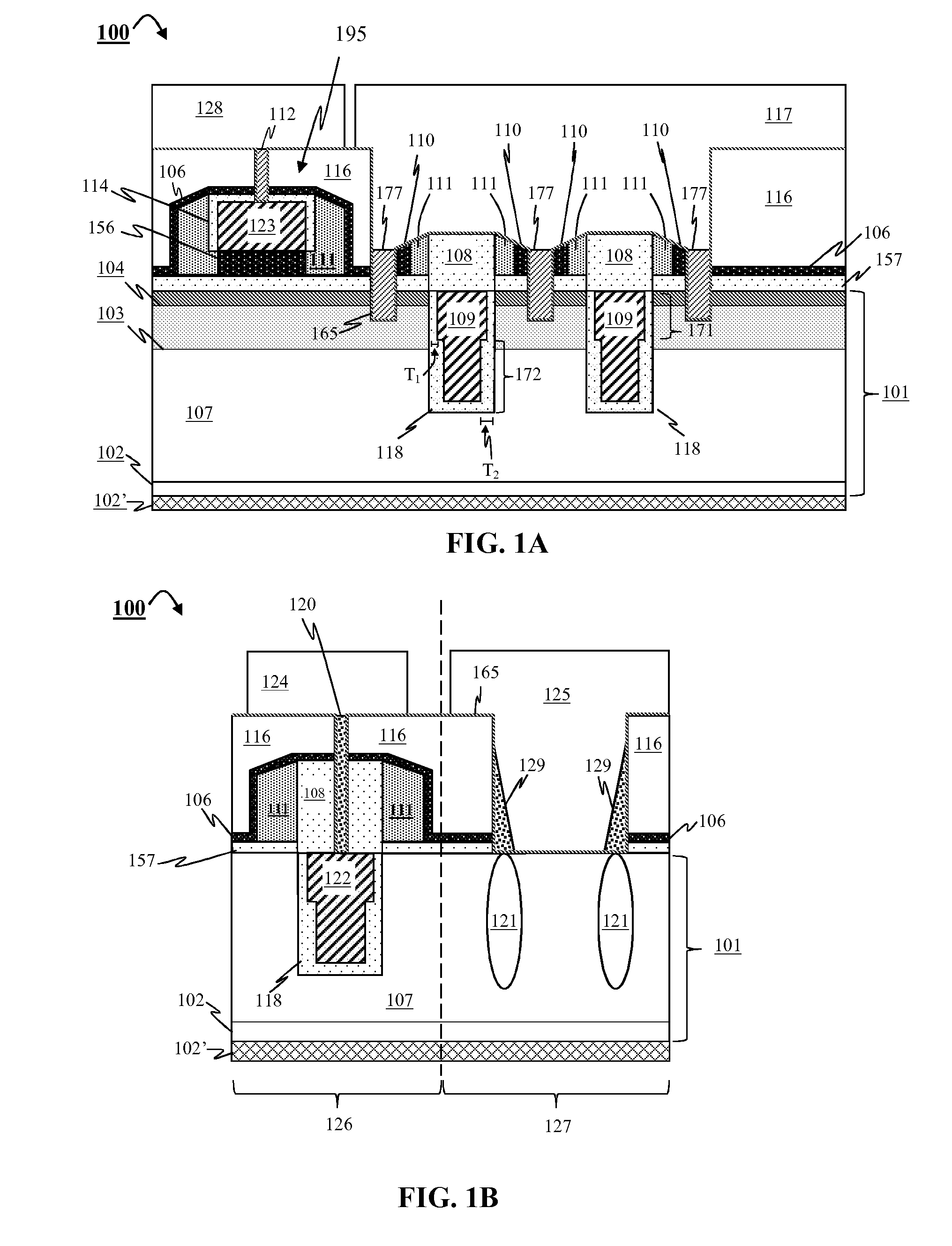

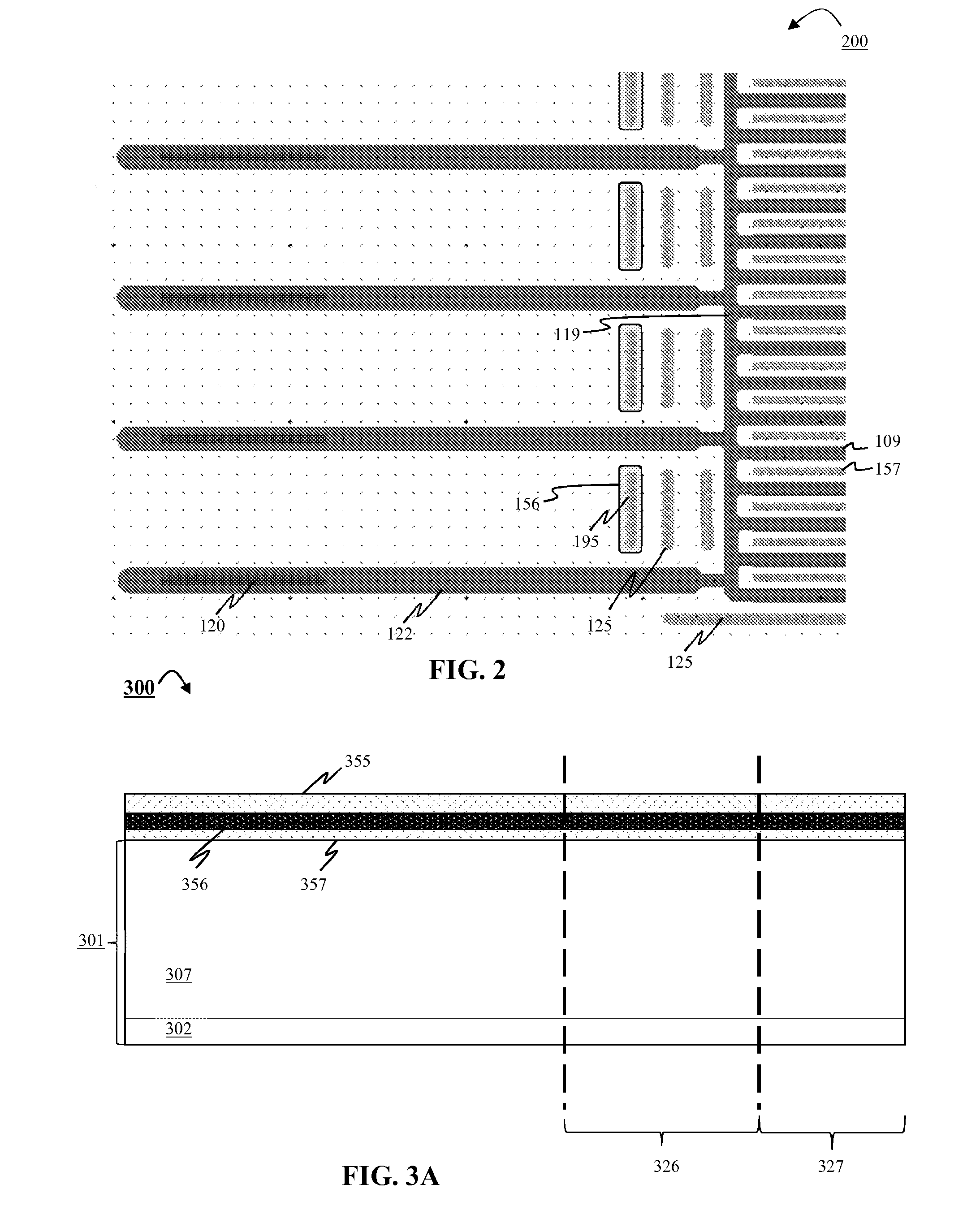

High density trench-based power MOSFETs with self-aligned active contacts and method for making such devices

ActiveUS8951867B2Semiconductor/solid-state device detailsSolid-state devicesHigh densitySubject matter

Aspects of the present disclosure describe a high density trench-based power MOSFET with self-aligned source contacts. The source contacts are self-aligned with a first insulative spacer and a second insulative spacer, wherein the first spacer is resistant to an etching process that will selectively remove the material the second spacer is made from. Additionally, the active devices may have a two-step gate oxide, wherein a lower portion of the gate oxide has a thickness T2 that is larger than the thickness T1 of an upper portion of the gate oxide. It is emphasized that this abstract is provided to comply with rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:ALPHA & OMEGA SEMICON INC

High density trench-based power mosfets with self-aligned active contacts and method for making such devices

ActiveUS20140175536A1Semiconductor/solid-state device detailsSolid-state devicesHigh densitySubject matter

Aspects of the present disclosure describe a high density trench-based power MOSFET with self-aligned source contacts. The source contacts are self-aligned with a first insulative spacer and a second insulative spacer, wherein the first spacer is resistant to an etching process that will selectively remove the material the second spacer is made from. Additionally, the active devices may have a two-step gate oxide, wherein a lower portion of the gate oxide has a thickness T2 that is larger than the thickness T1 of an upper portion of the gate oxide. It is emphasized that this abstract is provided to comply with rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:ALPHA & OMEGA SEMICON INC

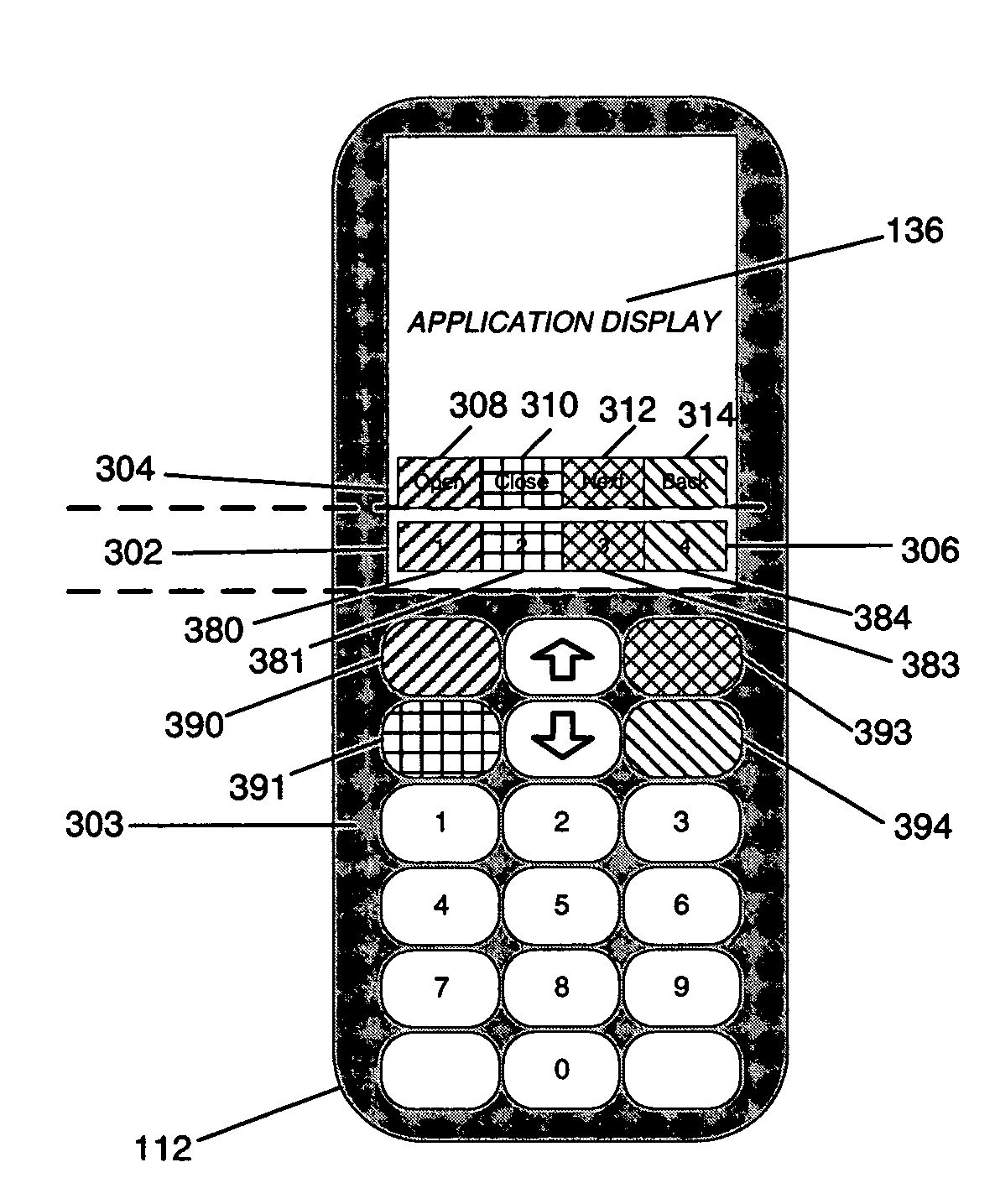

Application specific key buttons in a portable device

Aspects of the invention implement and execute commands of applications and / or services on portable devices with various key button configurations. Certain aspects of the invention create and display an intermediary user interface on a display of a portable device in order to match and utilize an application's commands with the various capabilities of different portable devices.

Owner:RPX CORP

Method and system for transmit power control techniques to reduce mutual interference between coexistent wireless networks device

Aspects of a method and system for transmit power control techniques to reduce mutual interference between coexistent wireless networks are provided. A coexistence terminal comprising a WLAN radio and a Bluetooth radio operating as a master device may transmit signals to one or more remote controllers comprising a slave Bluetooth radio to increase transmission power when the isolation between the coexistence terminal's WLAN and Bluetooth radios is below a threshold. Link manager protocol (LMP) signals may be utilized for changing the transmission power. When the isolation increases above the threshold, signals may be generated to reduce the remote controllers' transmission power. In some instances, in addition to increasing the transmission power of remote controllers, the transmission power of the Bluetooth radio or the WLAN radio may be reduced. The reduced Bluetooth or WLAN radio transmission power may be increased when the radio isolation in the coexistence terminal increases.

Owner:AVAGO TECH INT SALES PTE LTD