Semiconductor device capable of preventing moisture-absorption of fuse area thereof and method for manufacturing the fuse area

a technology of a semiconductor device and a fuse area, which is applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical equipment, etc., can solve the problems of affecting the reliability of semiconductor devices, affecting the cutting efficiency of fuse blades, and unable to withstand much moisture, so as to reduce the increase in the layout area, reduce the effect of moisture permeation and reduce the increase of the layout area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

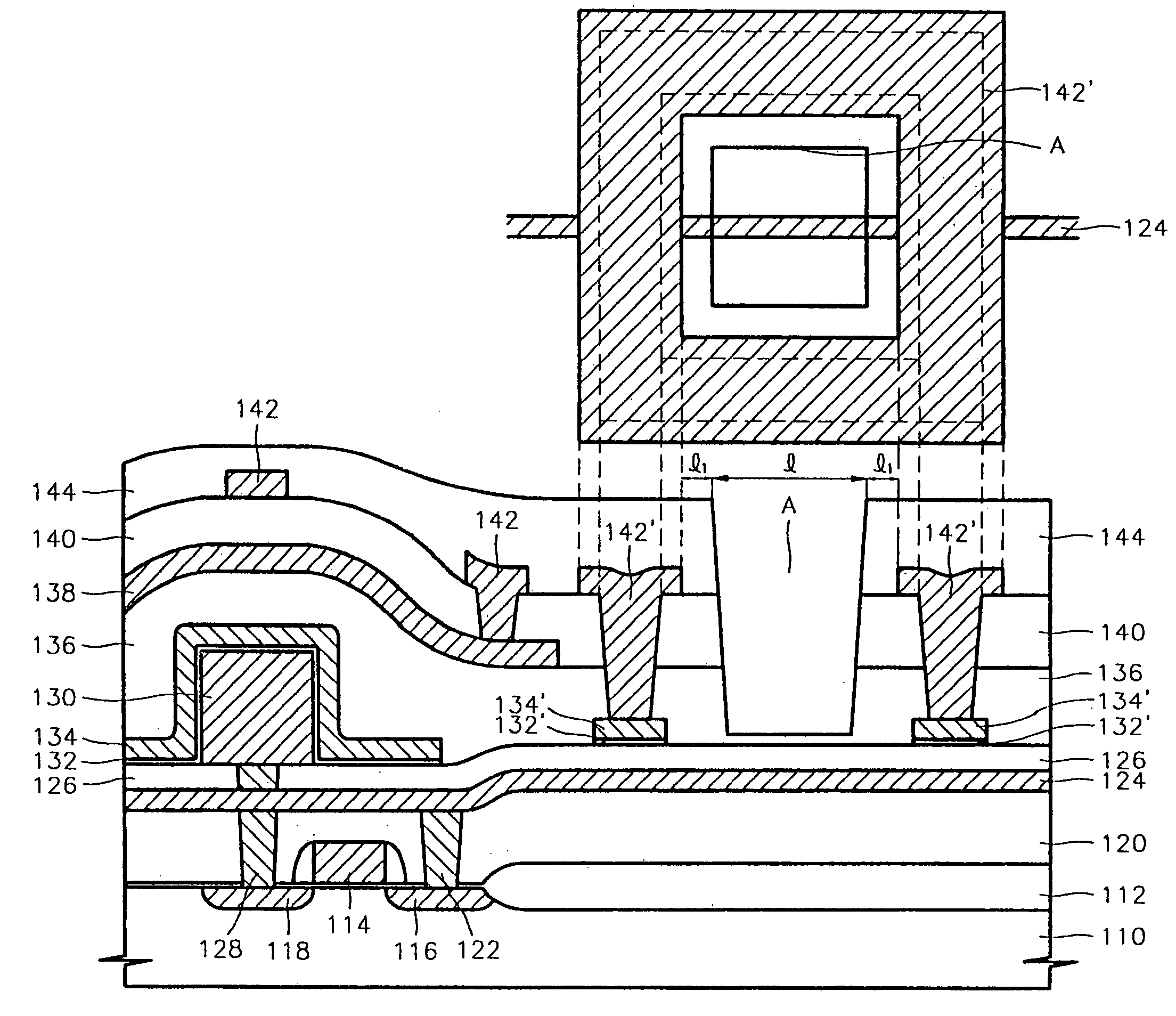

[0030] A portion of a DRAM device is illustrated in FIGS. 3 through 7. FIG. 3 shows a capacitor (130, 132, and 134). A fuse area in this embodiment is concurrently formed with a cell array area. Using conventional techniques, a device isolation film 112 is formed on a substrate 110. Then, a gate electrode 114 and source and drain regions 118 and 116 of a transistor are formed. An interlayer insulating film 120 is deposited on the entire surface of the substrate 110 including the device isolation film 112. Subsequently, the interlayer insulating film 120 is etched to form a contact hole exposing the drain region 116. Next, a conductive material, for example, doped polysilicon, metal silicide or a stacked film of polysilicon and metal silicide, is processed conventionally to form a contact plug 122 in the contact hole and a bit line 124 extending across the region of the device. The bit line 124 on the right of FIG. 3 functions as a fuse line. As described above, instead of the bit li...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More