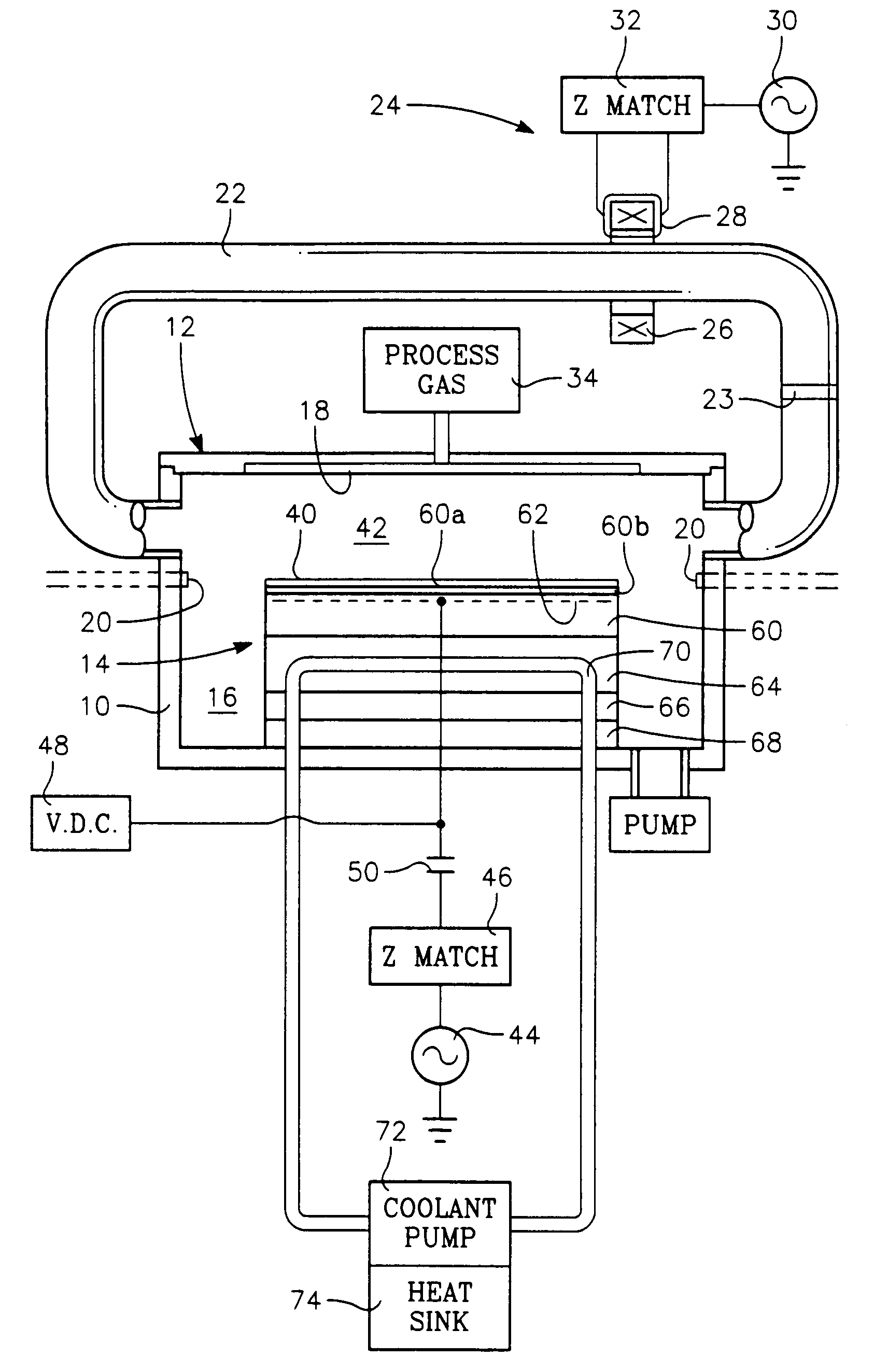

Plasma immersion ion implantation apparatus

a technology of plasma and ion implantation, which is applied in the direction of electrical equipment, electrical discharge tubes, decorative arts, etc., can solve the problems of low quality deposited layer that is less crystalline and more amorphous, rough surface of the wafer, and excessive sheet resistan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

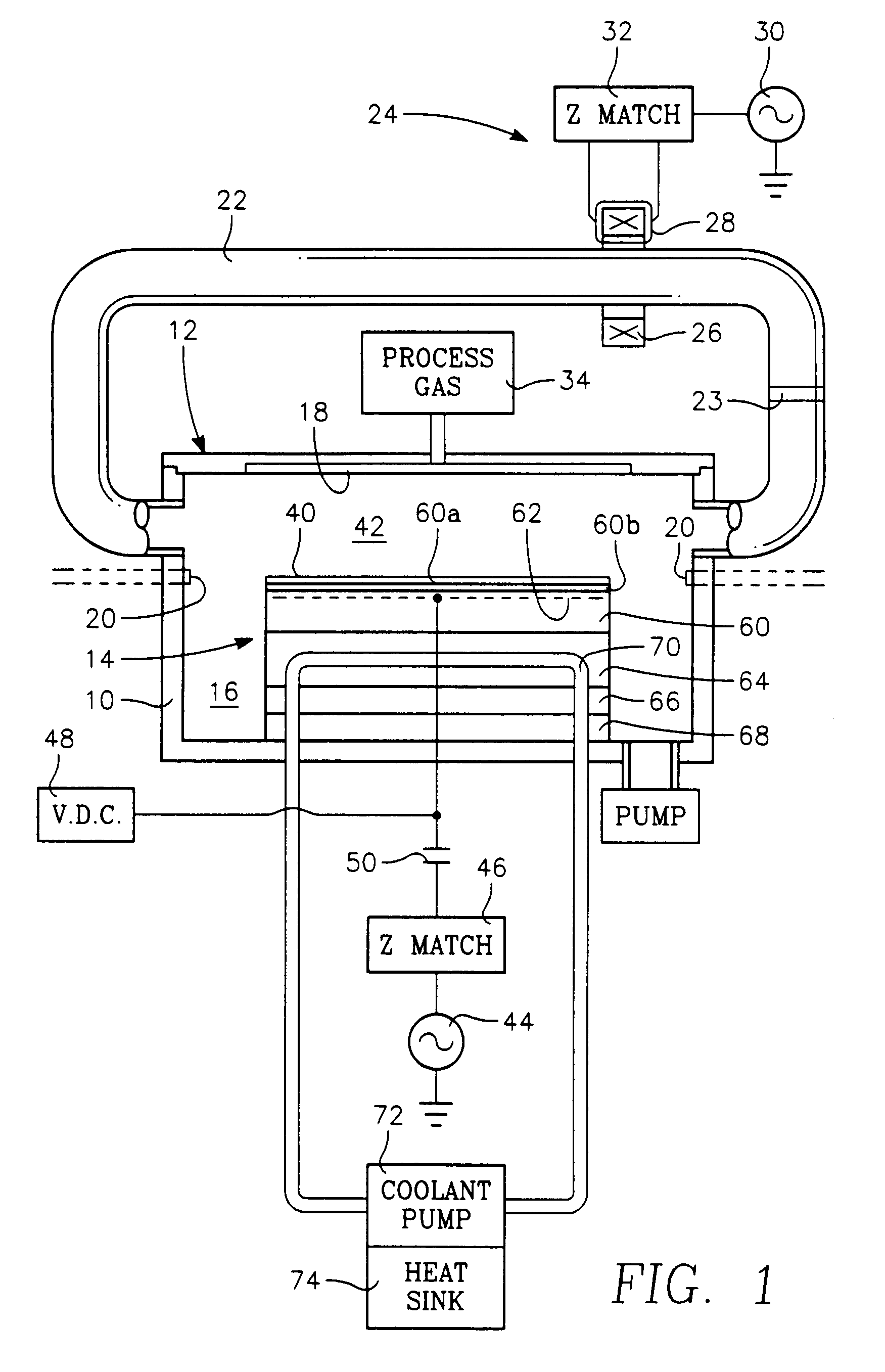

Method used

Image

Examples

working examples

[0092] Plasma immersion ion implantation using a fluoride dopant gas (such as BF3) with a bias voltage of 1 kV can be carried out using ESC temperature in a range between −40 and +60 degrees C., the preferred range being between 0 and +40 degrees C., a chamber wall temperature in the range of 0 to 120 degrees C., the preferred range being 20 to 80 degrees C. If the bias voltage is increased to 8 kV, then the maximum ESC temperature decreases to 60 degrees C. and the preferred maximum ESC temperature decreases to 20 degrees C. The foregoing assumes that Si etching loss be limited to much less than 10 Angstroms. For a hydride dopant gas, the temperature range tends to be higher, because, compared to fluoride dopant gases, hydride dopant gases tend to etch less and promote more deposition: at 1 kV bias and 500 watt source power, the ESC temperature range is 0 to 80 degrees C., the preferred range being 20 to 60 degrees C. At 8 kV, a lower temperature is better, the range being decrease...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Fraction | aaaaa | aaaaa |

| Fraction | aaaaa | aaaaa |

| Temperature | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More