Patents

Literature

84 results about "Metallic contamination" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

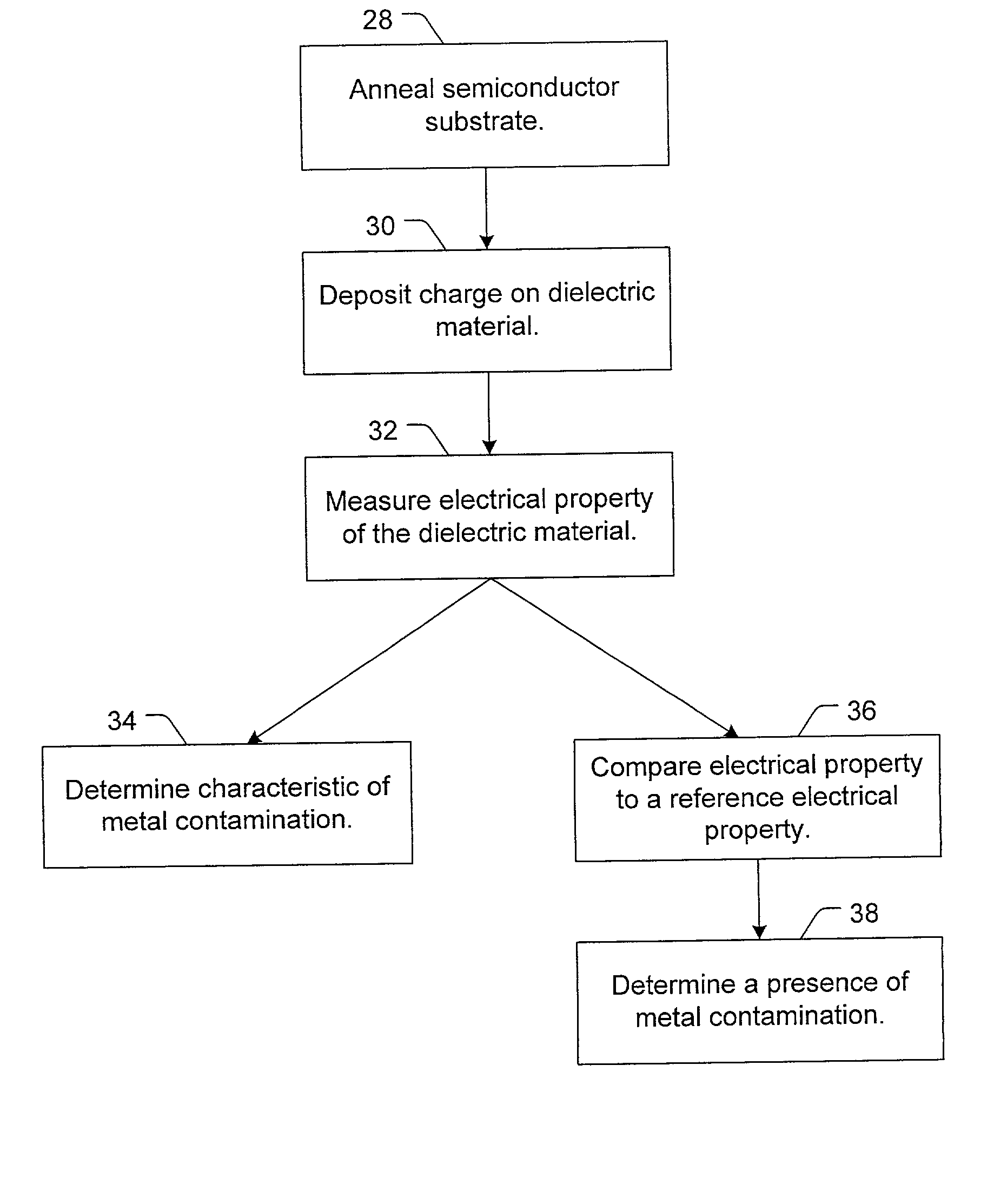

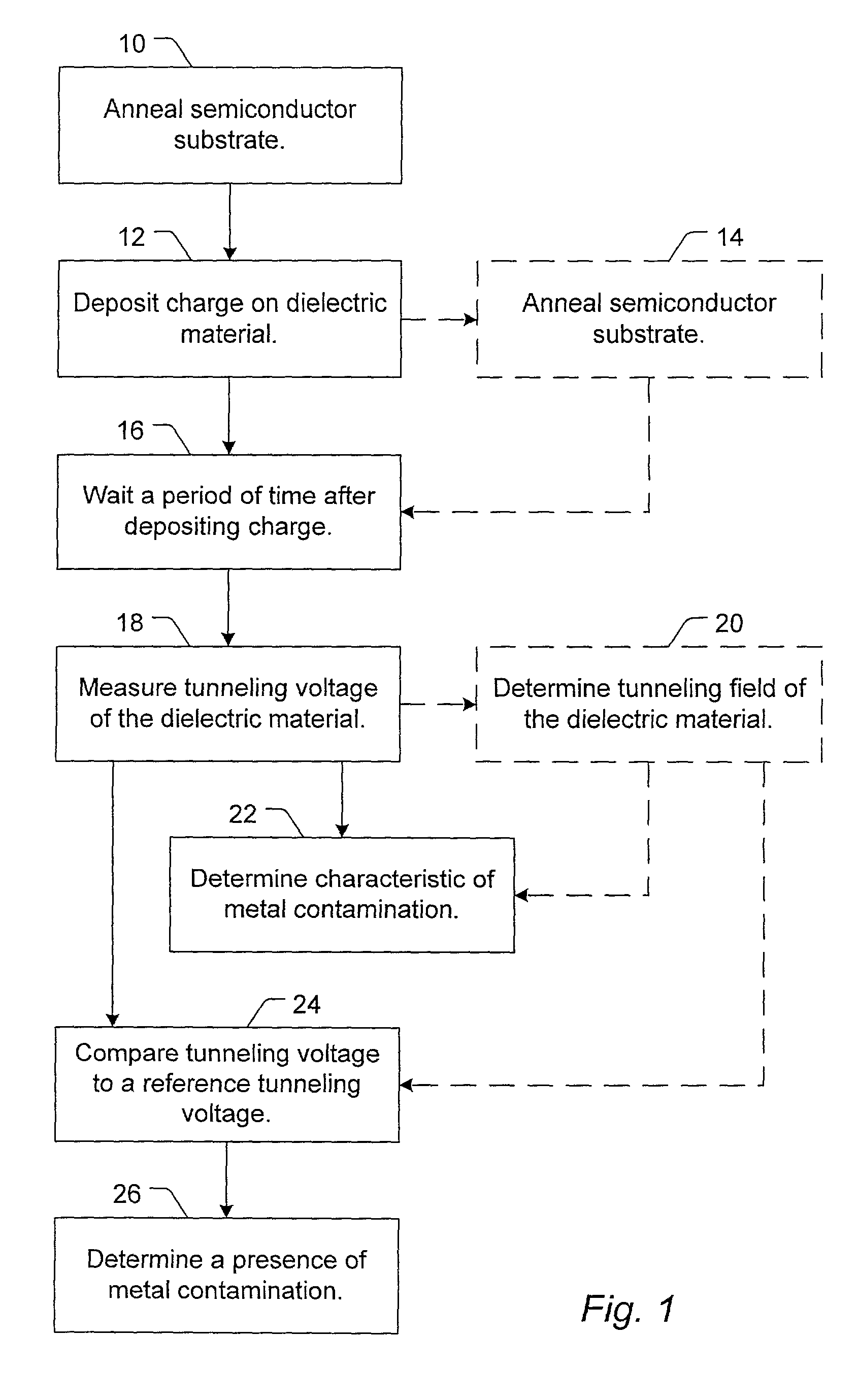

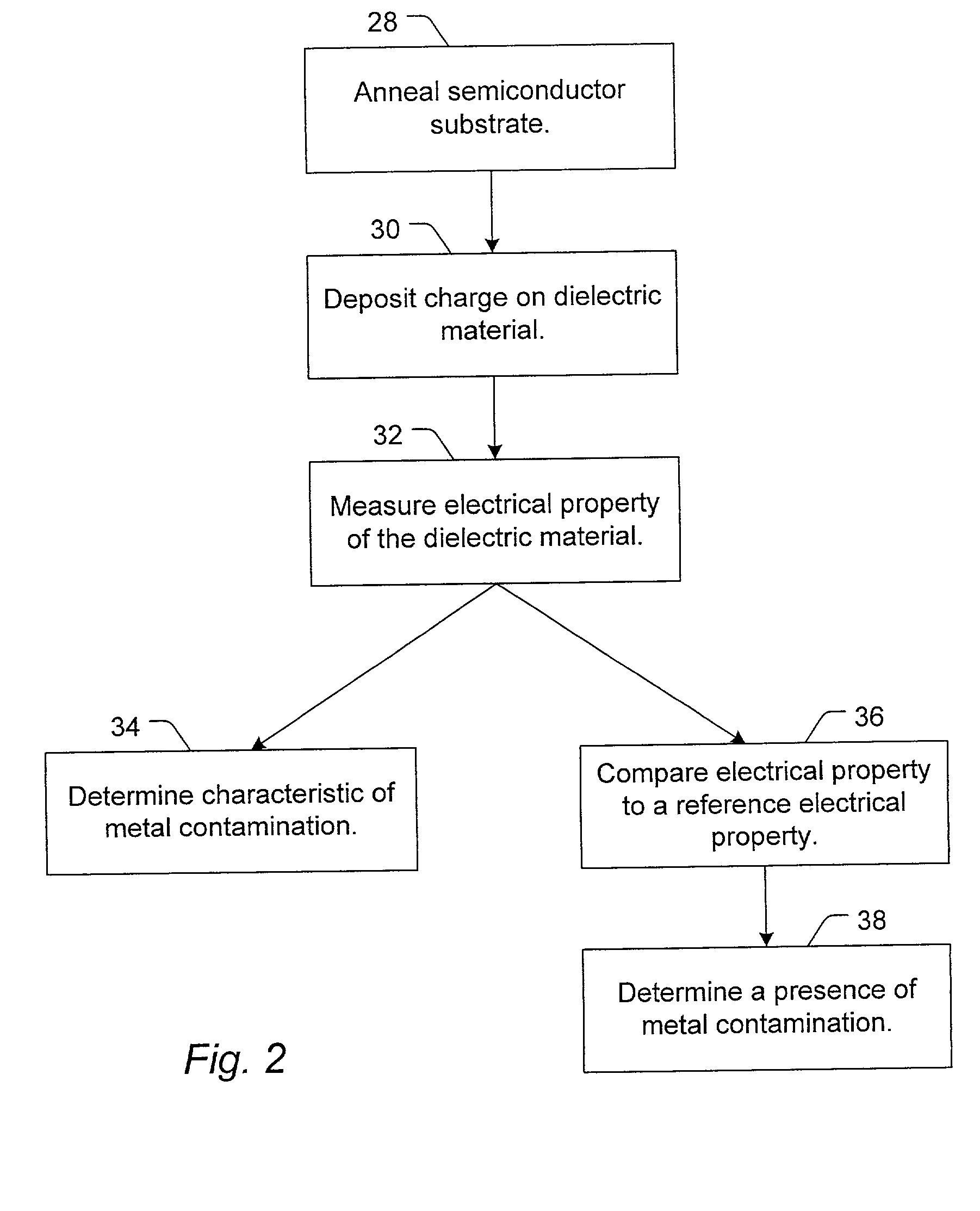

Method and system for detecting metal contamination on a semiconductor wafer

InactiveUS20020090746A1Semiconductor/solid-state device testing/measurementSolid-state devicesElectricityWork function

A method to detect metal contamination on a semiconductor topography is provided. The semiconductor topography may include a semiconductor substrate or a dielectric material disposed upon a semiconductor substrate. The metal contamination may be driven into the semiconductor substrate by an annealing process. Alternatively, the annealing process may drive the metal contamination into the dielectric material. Subsequent to the annealing process, a charge may be deposited upon an upper surface of the semiconductor topography. An electrical property of the semiconductor topography may be measured. A characteristic of at least one type of metal contamination may be determined as a function of the electrical property of the semiconductor topography. The method may be used to determine a characteristic of one or more types of metal contamination on a portion of the semiconductor topography or the entire semiconductor topography. A system configured to detect metal contamination on a semiconductor topography is also provided. An oven may be incorporated into the system and may be used to anneal the semiconductor topography. The system may also include a device that may be configured to deposit a charge on an upper surface of the semiconductor topography. A sensor may also be included in the system. The sensor may use a non-contact work function technique to measure an electrical property of the semiconductor topography.

Owner:KLA TENCOR TECH CORP

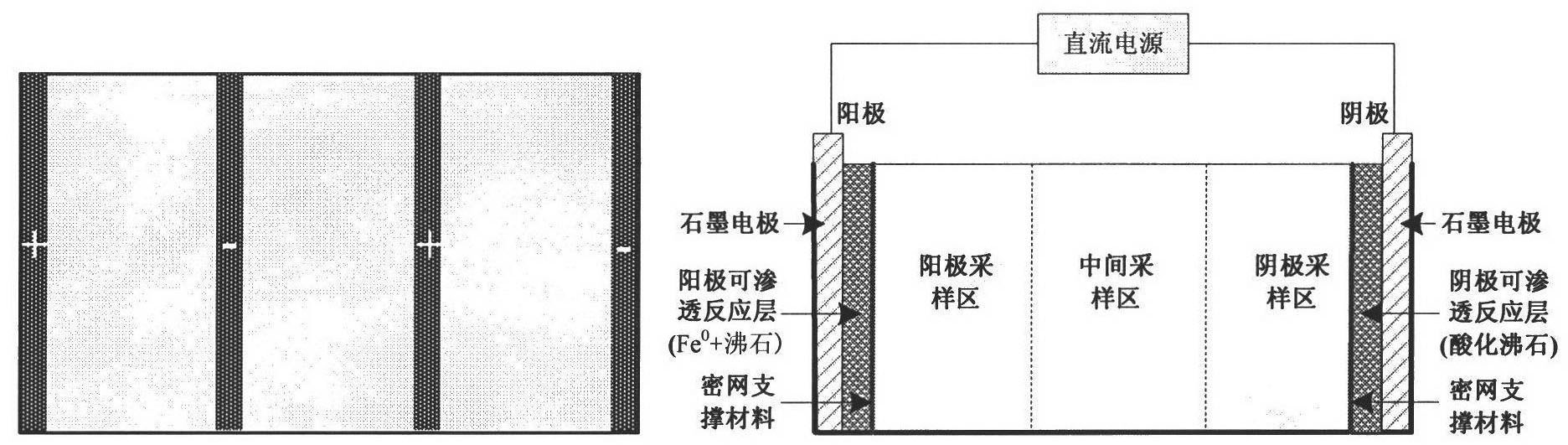

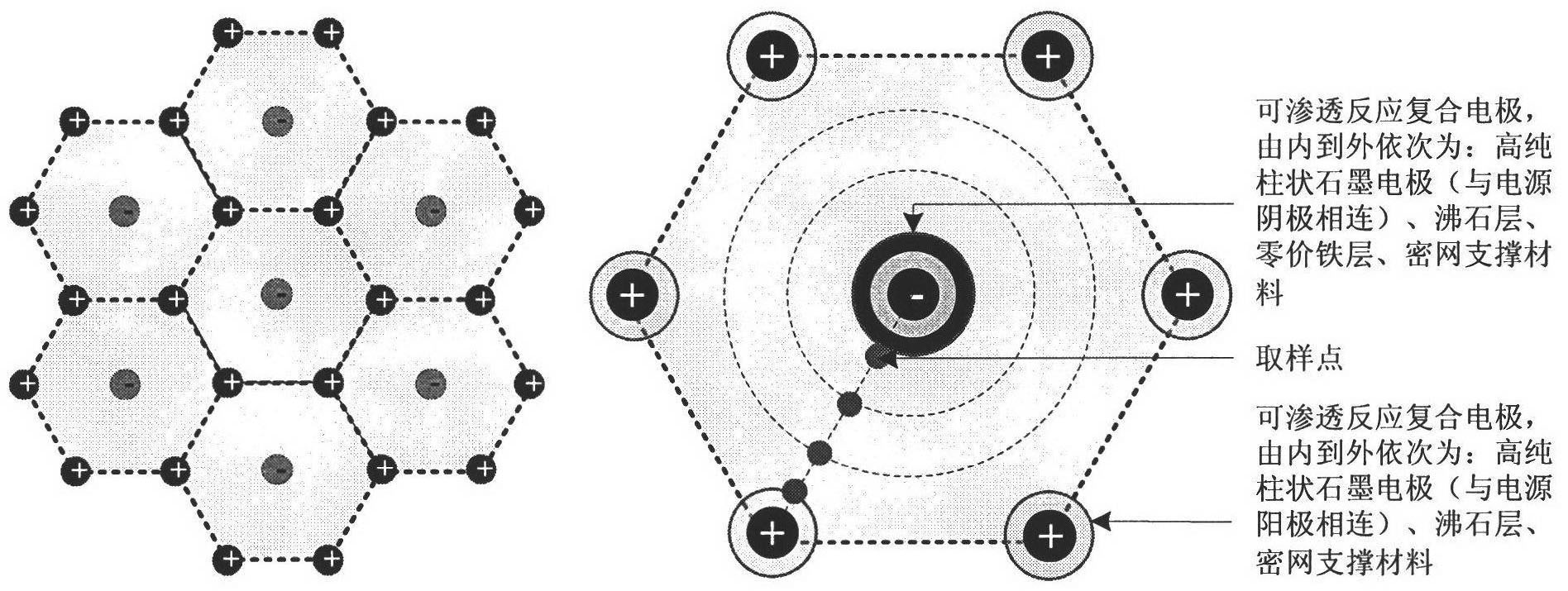

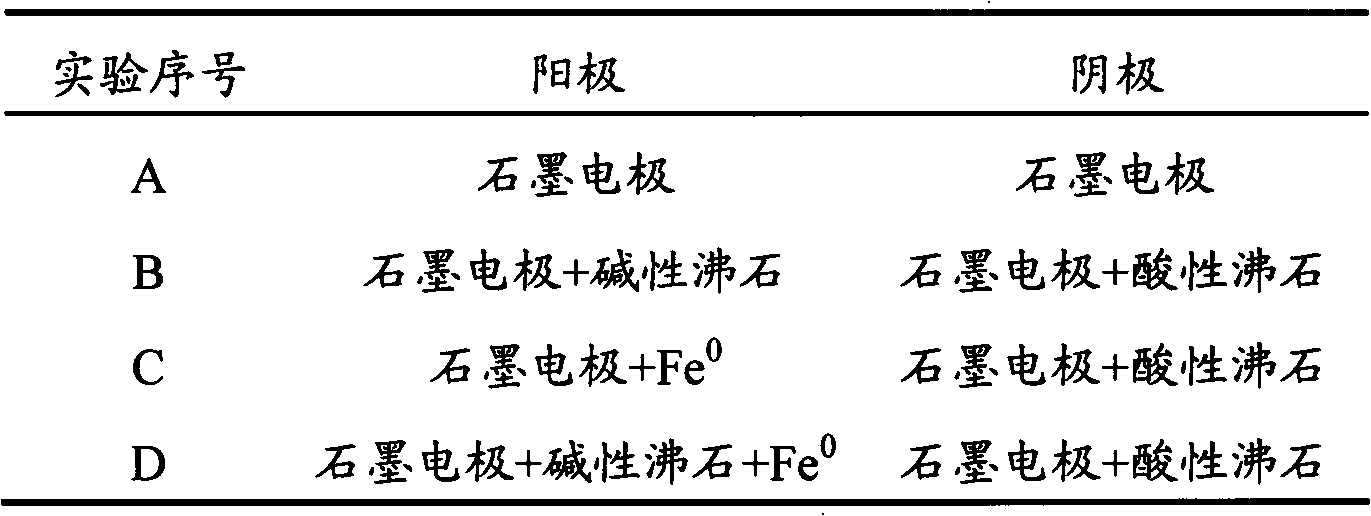

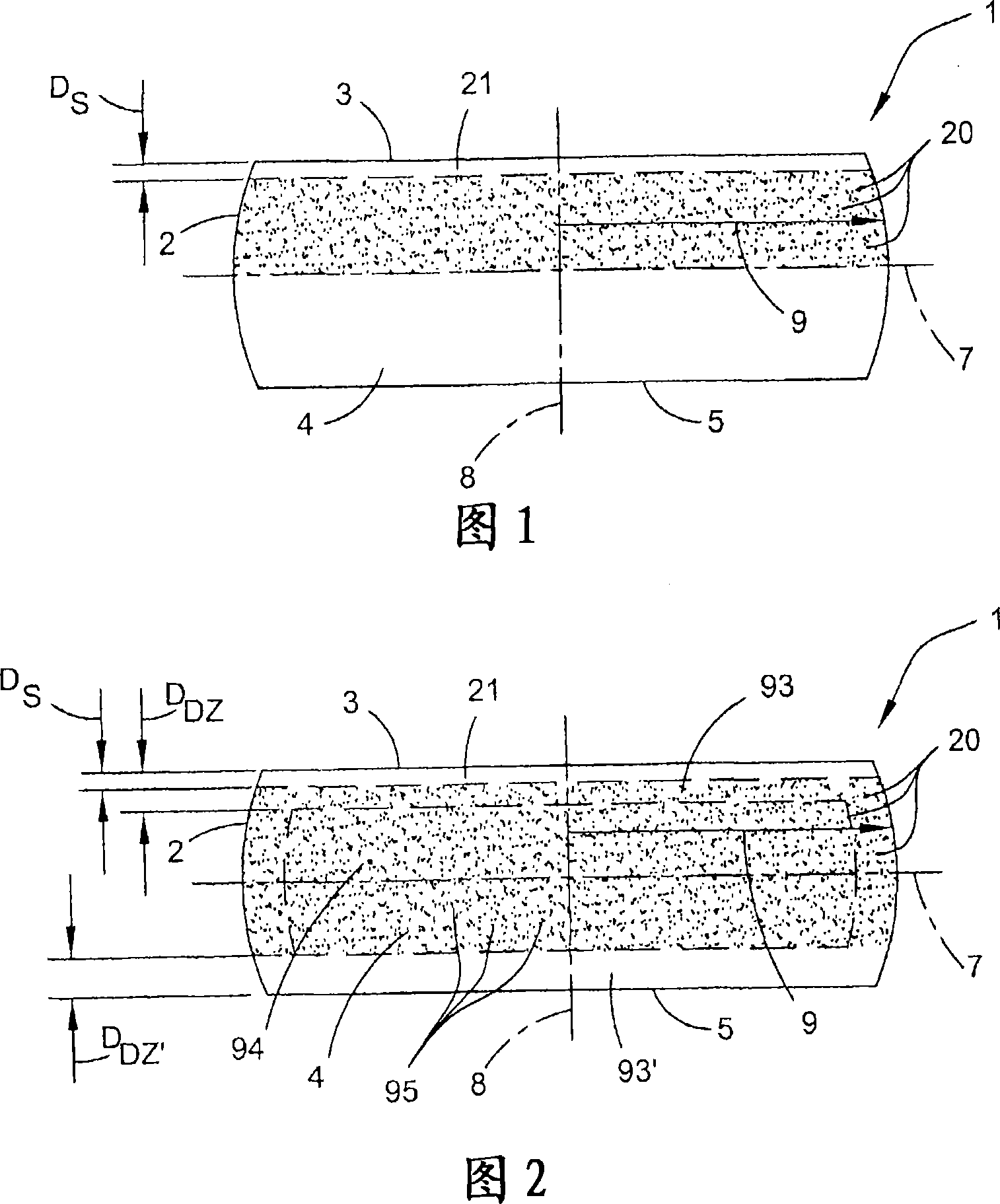

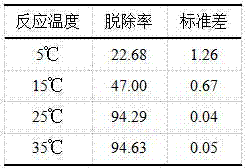

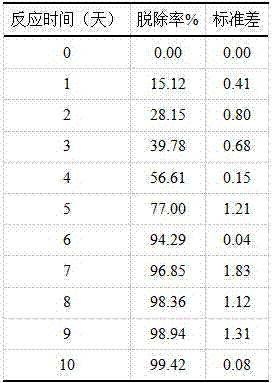

Electrokinetic remediation method of heavy metal polluted soil by composite electrodes

ActiveCN102441564AEffective pH controlWeaken the big changeContaminated soil reclamationGraphite electrodeElectrokinetic remediation

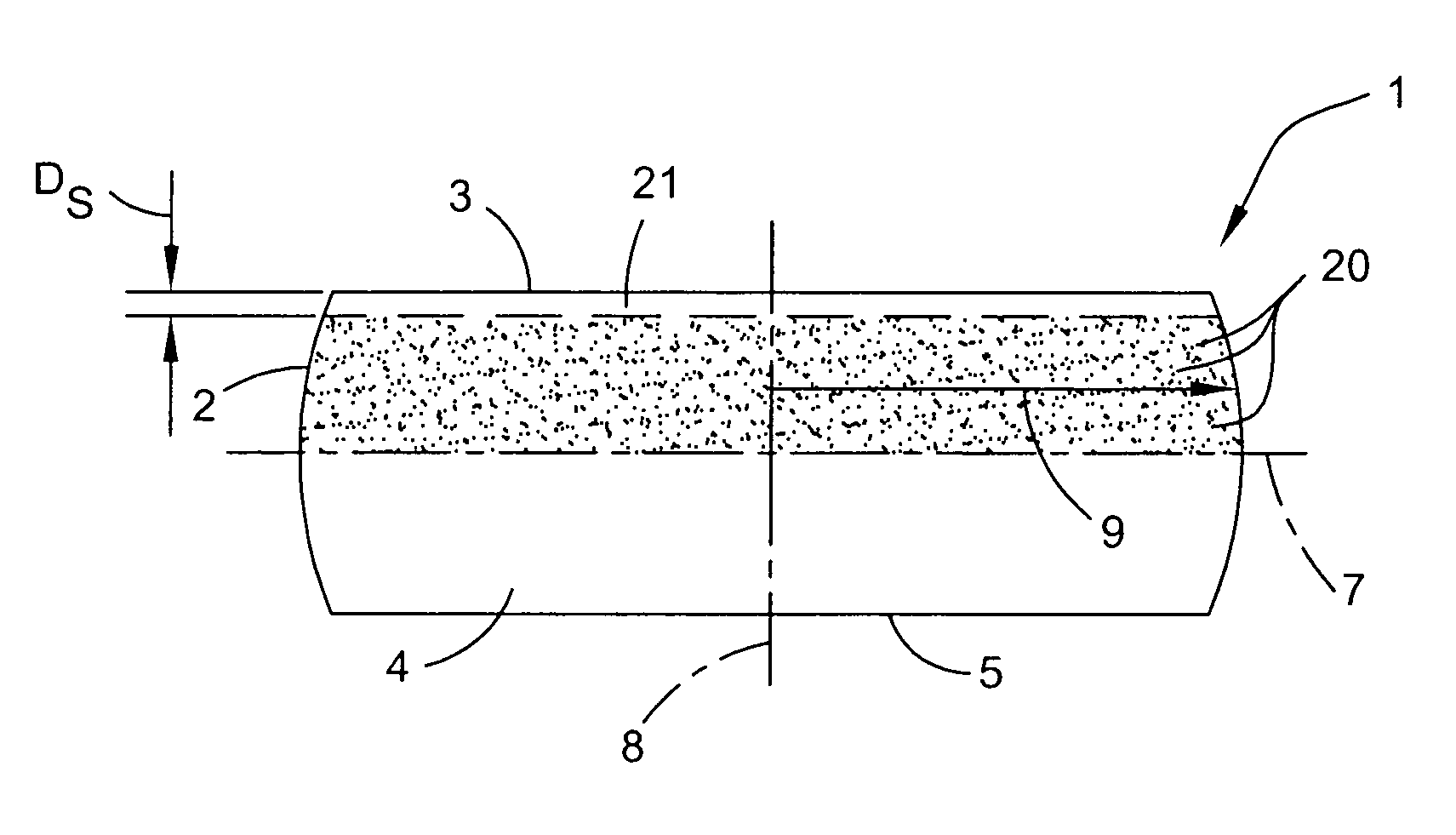

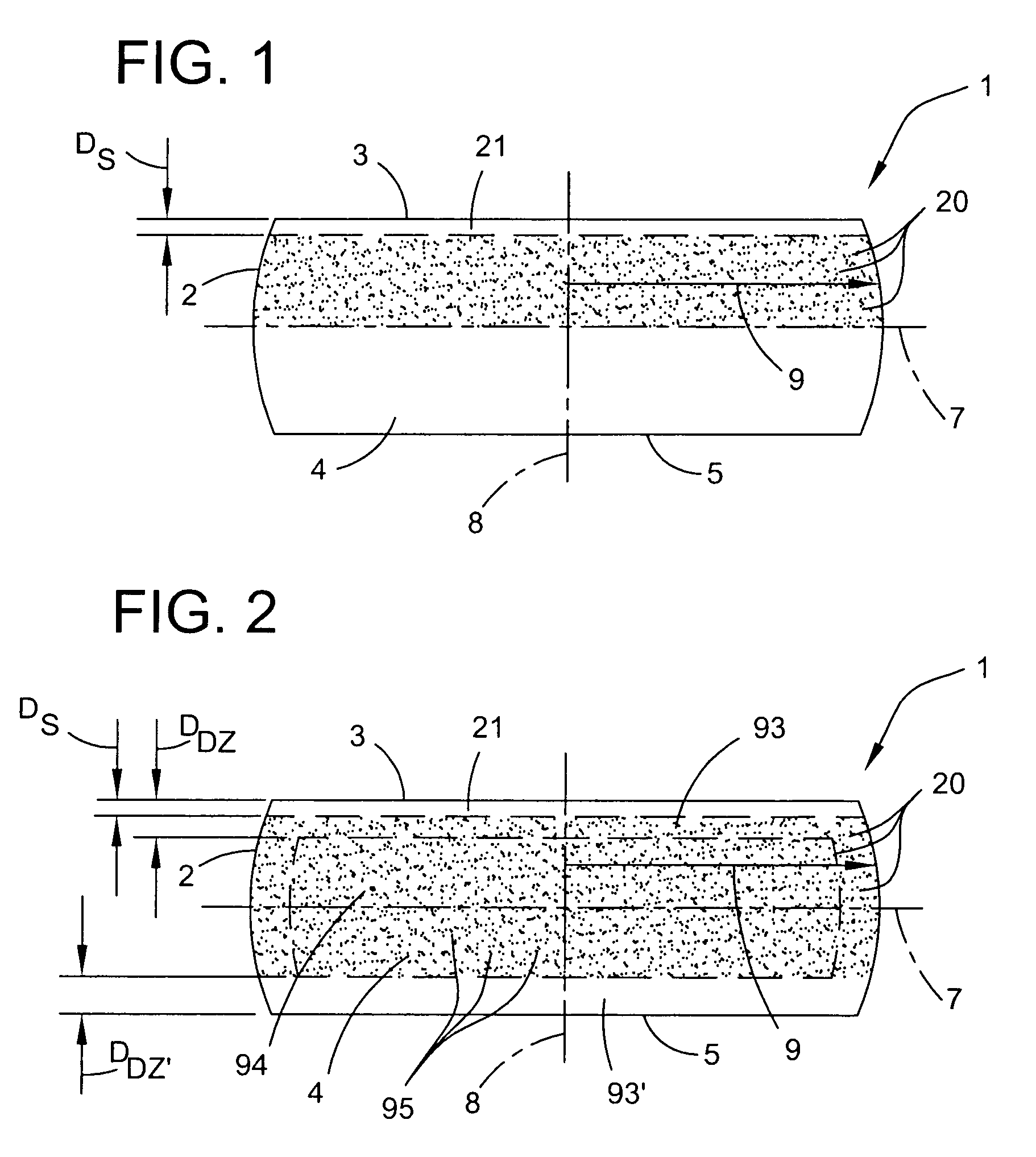

The invention relates to composite electrodes and an electrokinetic remediation method of heavy metal polluted soil by using the composite electrodes. According to the electrodes, an active material layer is adhered to the surface of graphite electrodes or metal electrodes of an anode and a cathode so as to form integrated composite electrodes with permeable reactive performance. By the permeablereactive layer, on one hand, H<+> and OH<-> generated from the electrode reaction can be neutralized and adsorbed, the pH value of the soil can be effectively controlled, and the heavy metal can be prevented from being prematurely deposited in the soil. On the other hand, migrated heavy metal pollutants can be captured, and in situ removal of the heavy metal pollutants in the soil can be realizedby removing the composite electrodes.

Owner:上海环境保护有限公司

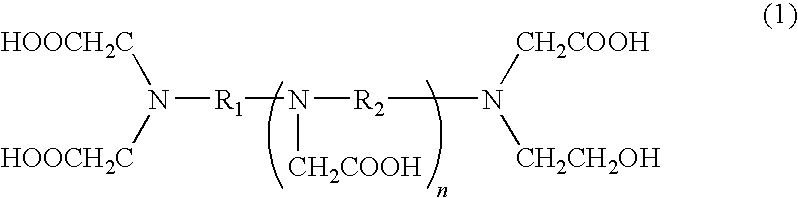

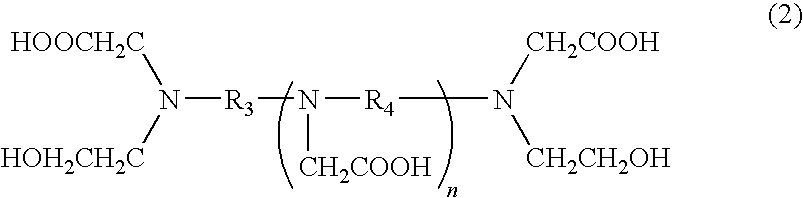

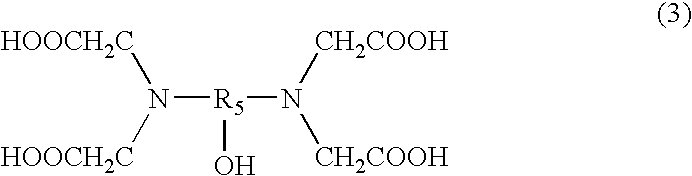

Cleaning solution for substrate for semiconductor device and cleaning method

InactiveUS20060270573A1Good water rinsabilityEasy to cleanOrganic detergent compounding agentsDetergent mixture composition preparationDevice materialOrganic base

To provide a cleaning solution for a substrate for a semiconductor device capable of removing particle contamination, organic contamination and metal contamination at the same time without corroding the substrate surface, and further having good water rinsability and capable of making the substrate surface highly clean in a short time, and a cleaning method. A cleaning solution for a substrate for a semiconductor device, which comprises an organic acid as component (a), an organic alkaline component as component (b), a surfactant as component (c) and water as component (d) and which has a pH of at least 1.5 and less than 6.5. A method for cleaning a substrate for a semiconductor device, which comprises cleaning a substrate for a semiconductor device having a Cu film and a low dielectric constant insulating film on its surface and having CMP treatment applied thereto, by means of the above cleaning solution for a substrate for a semiconductor device.

Owner:MITSUBISHI CHEM CORP

Process for metallic contamination reduction in silicon wafers

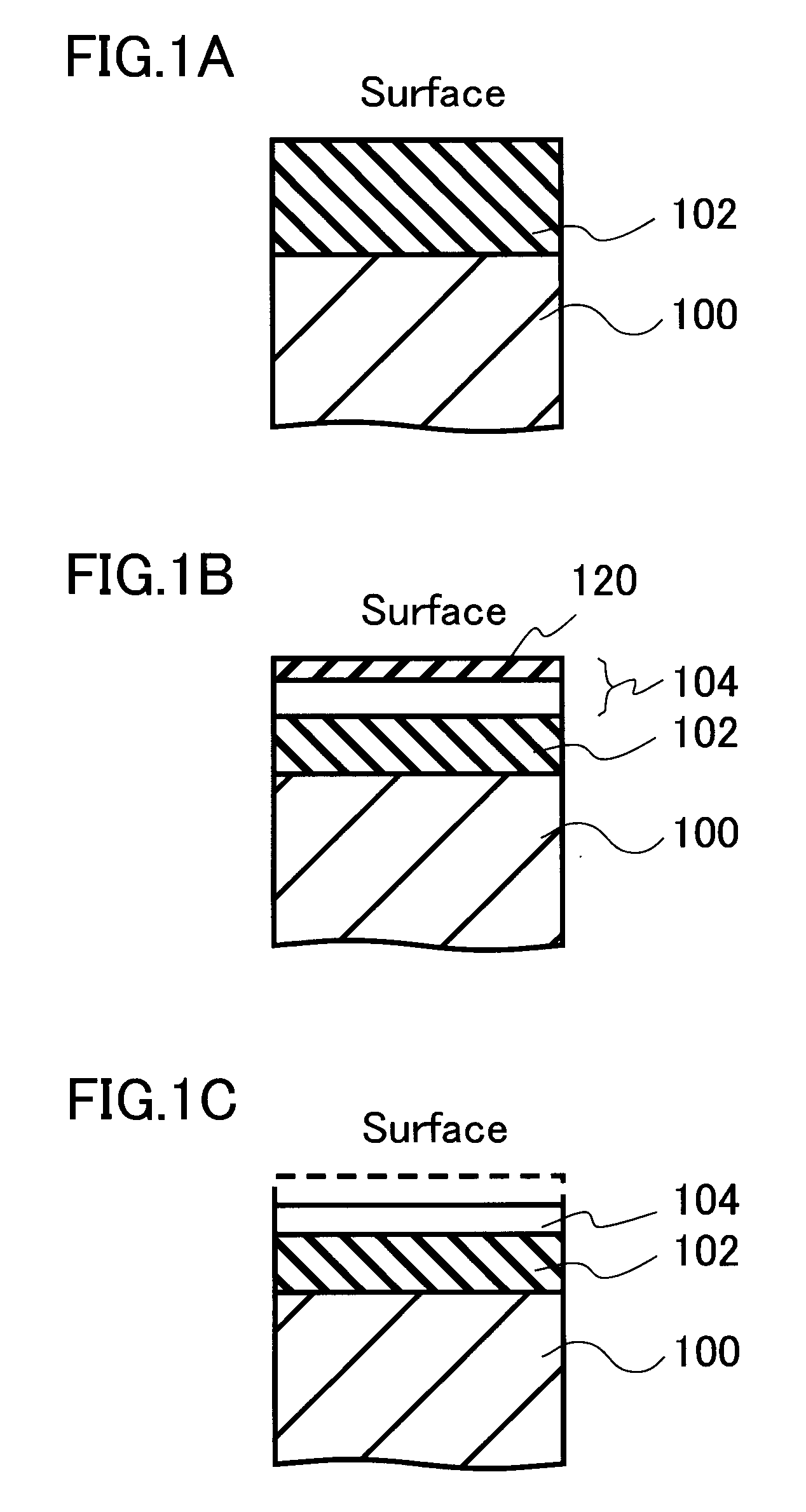

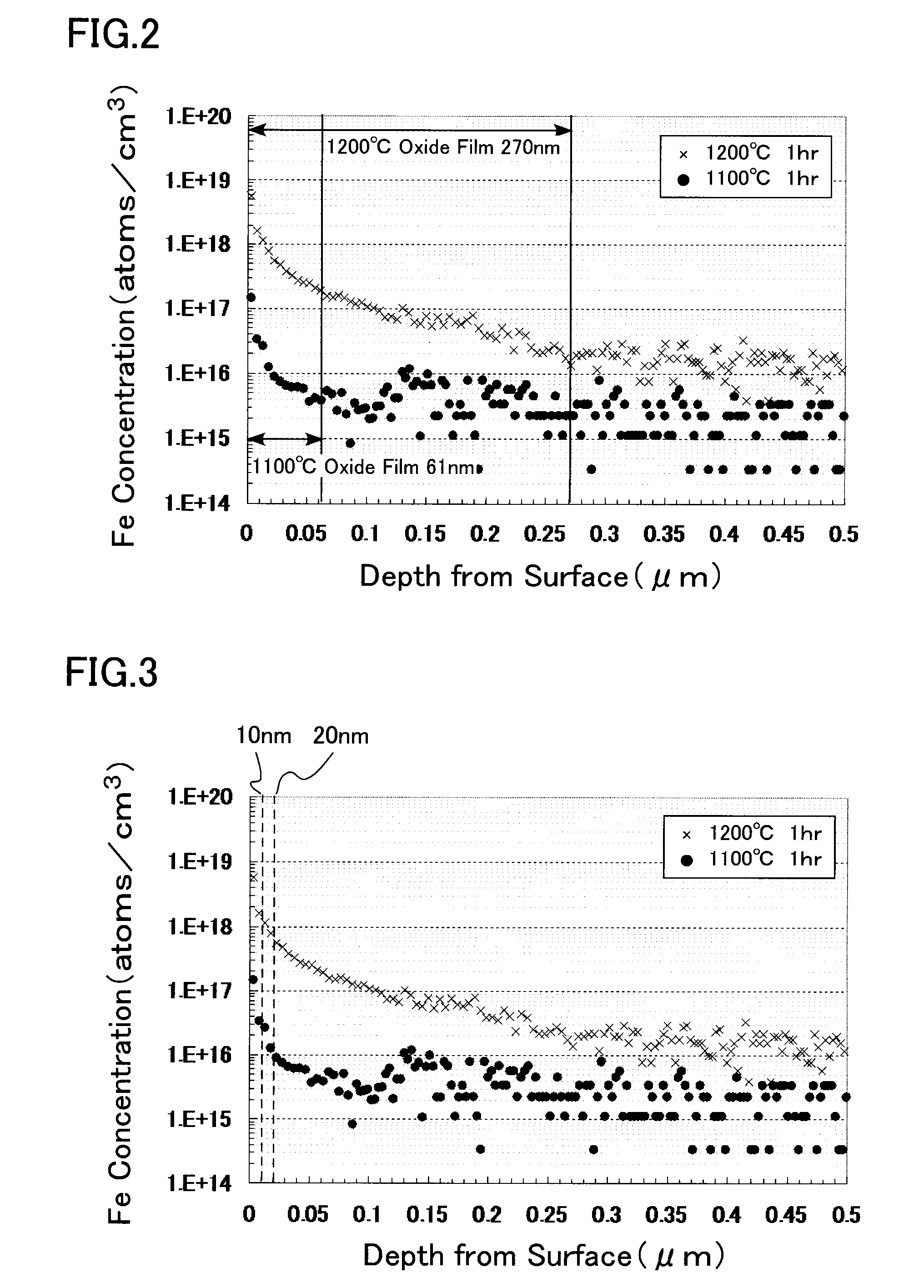

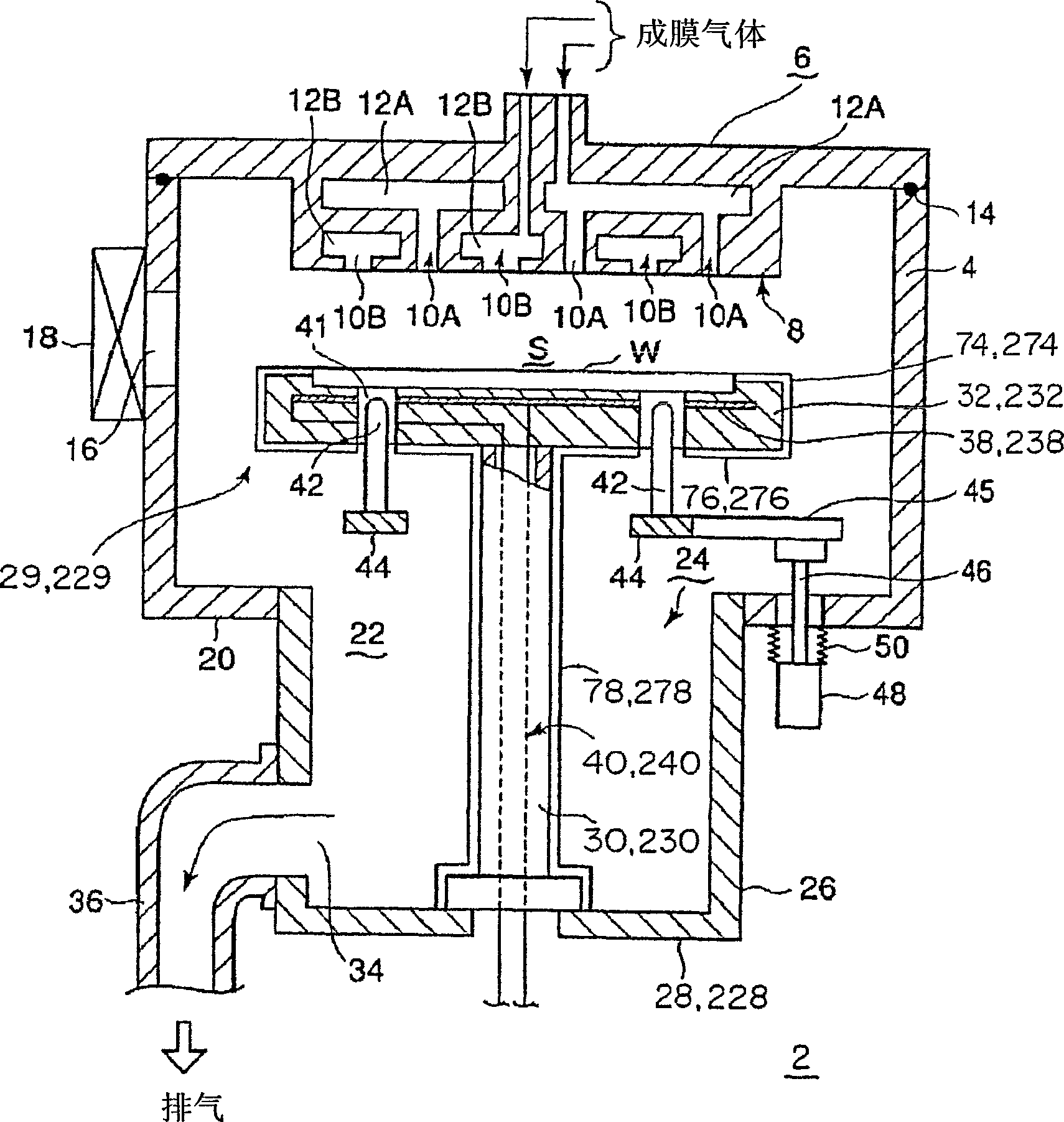

ActiveUS20050250297A1Promote migrationSmall sizeSemiconductor/solid-state device manufacturingCopperOxygen

A process for removing a contaminant selected from among copper, nickel, and a combination thereof from a silicon wafer having a surface and an interior. The process comprises cooling the silicon wafer in a controlled atmosphere from a temperature at or above an oxidation initiation temperature and initiating a flow of an oxygen-containing atmosphere at said oxidation initiation temperature to create an oxidizing ambient around the silicon wafer surface to form an oxide layer on the silicon wafer surface and a strain layer at an interface between the oxide layer and the silicon wafer interior. The cooling of the wafer is also controlled to permit diffusion of atoms of the contaminant from the silicon wafer interior to the strain layer. Then the silicon wafer is then cleaned to remove the oxide layer and the strain layer, thereby removing said contaminant having diffused to the strain layer.

Owner:GLOBALWAFERS CO LTD

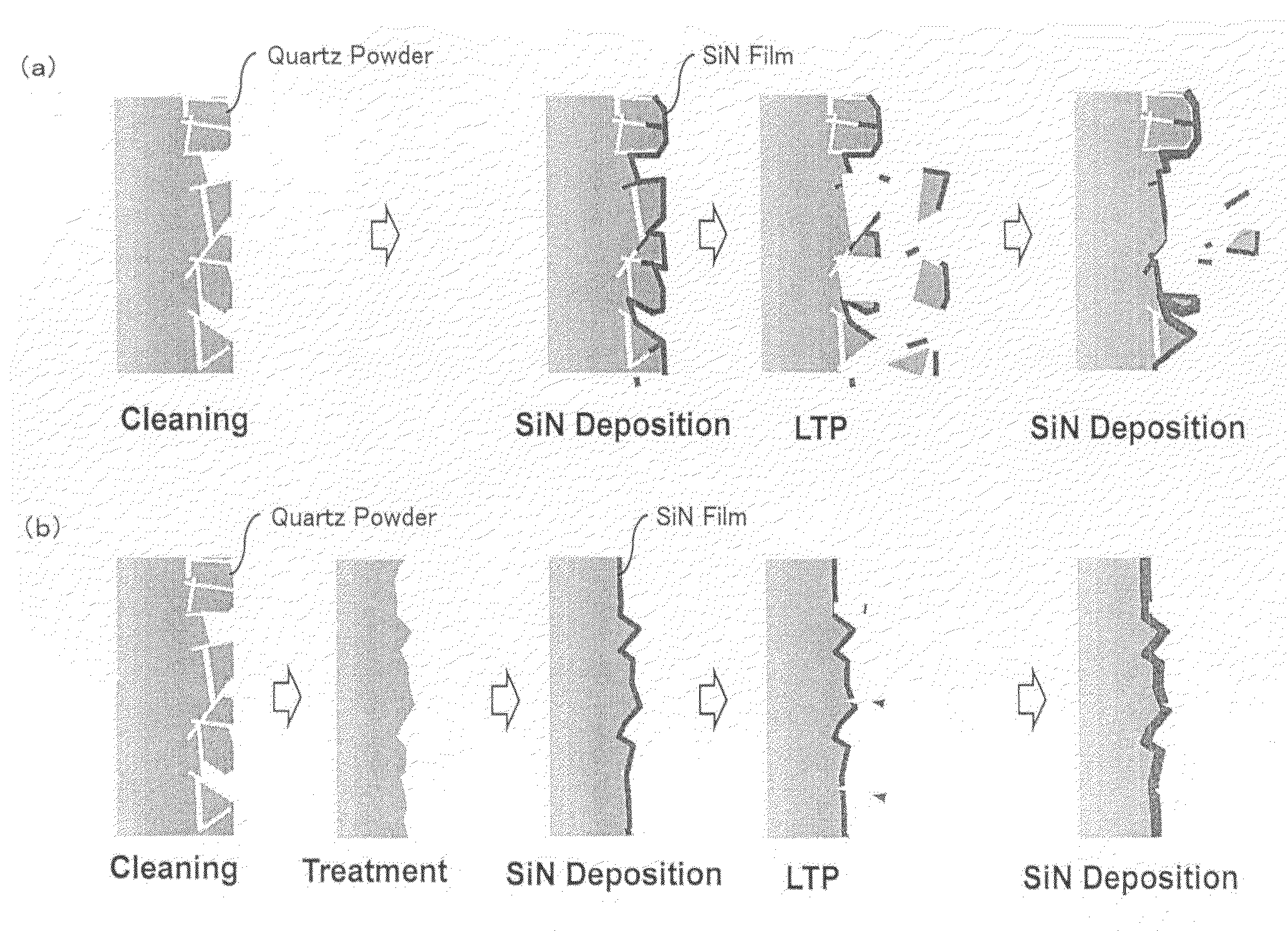

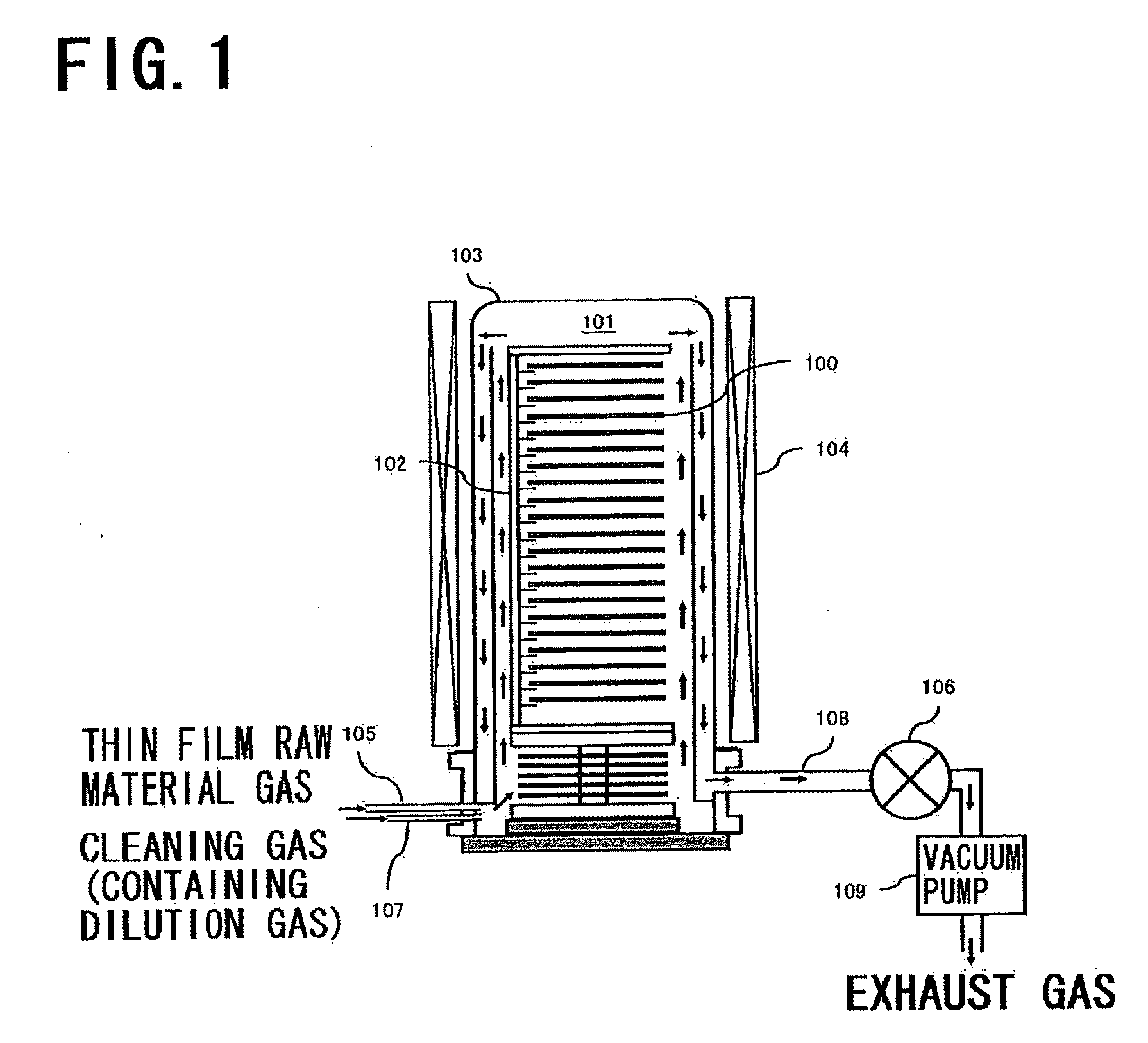

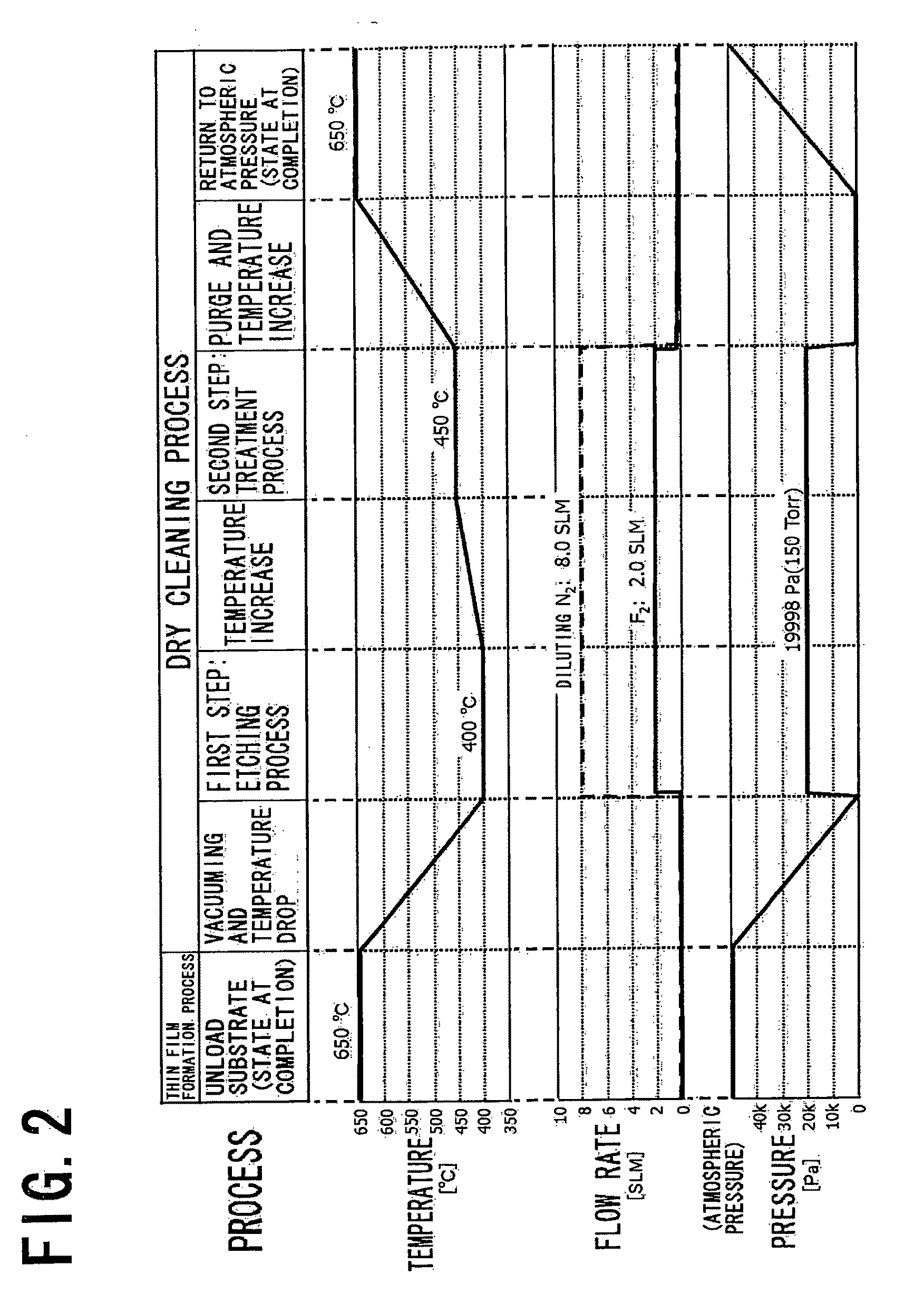

Method for manufacturing semiconductor device and substrate processing apparatus

InactiveUS20090149032A1Sufficient etching rateLiquid surface applicatorsSemiconductor/solid-state device manufacturingProduct gasInert gas dilution

The present invention suppresses metallic contamination in a processing chamber and a breakage of a quartz member, while suppressing decrease in film formation rate in a thin film formation process immediately after dry cleaning of the inside of the processing chamber, and enhances the operation rate of a apparatus. The method according to the invention includes the steps of: removing the thin film on the inside of the processing chamber by supplying a fluorine gas solely or a fluorine gas diluted by an inert gas solely, as the cleaning gas, to the inside of the processing chamber heated to a first temperature; and removing an adhered material remaining on the inside of the processing chamber after removing the thin film by supplying a fluorine gas solely or a fluorine gas diluted by an inert gas solely, as the cleaning gas, to the inside of the processing chamber heated to a second temperature.

Owner:KOKUSA ELECTRIC CO LTD

Cleaning agent for electronic materials

InactiveUS20110245127A1Improve device reliabilityHigh yieldOrganic detergent compounding agentsOrganic chemistryActive agentSulfamic acid

Provided is a cleaning agent for electronic materials, which enables very efficient advanced cleaning such that yield in the production of the electronic materials is improved and cleaning in a short period of time becomes possible, the cleaning agent having excellent cleaning power for fine-grained particles and organic matter and being able to reduce metallic contamination on the substrate. The cleaning agent for electronic materials comprises sulfamic acid (A), an anionic surfactant having at least one sulfonic acid group or a salt thereof in the molecule (B), a chelating agent (C), and water, wherein the pH at 25 C is preferably not more than 3.0 and the (B) is preferably a polymeric anionic surfactant (B1) having a weight average molecular weight of 1,000 to 2,000,000.

Owner:SANYO CHEM IND LTD

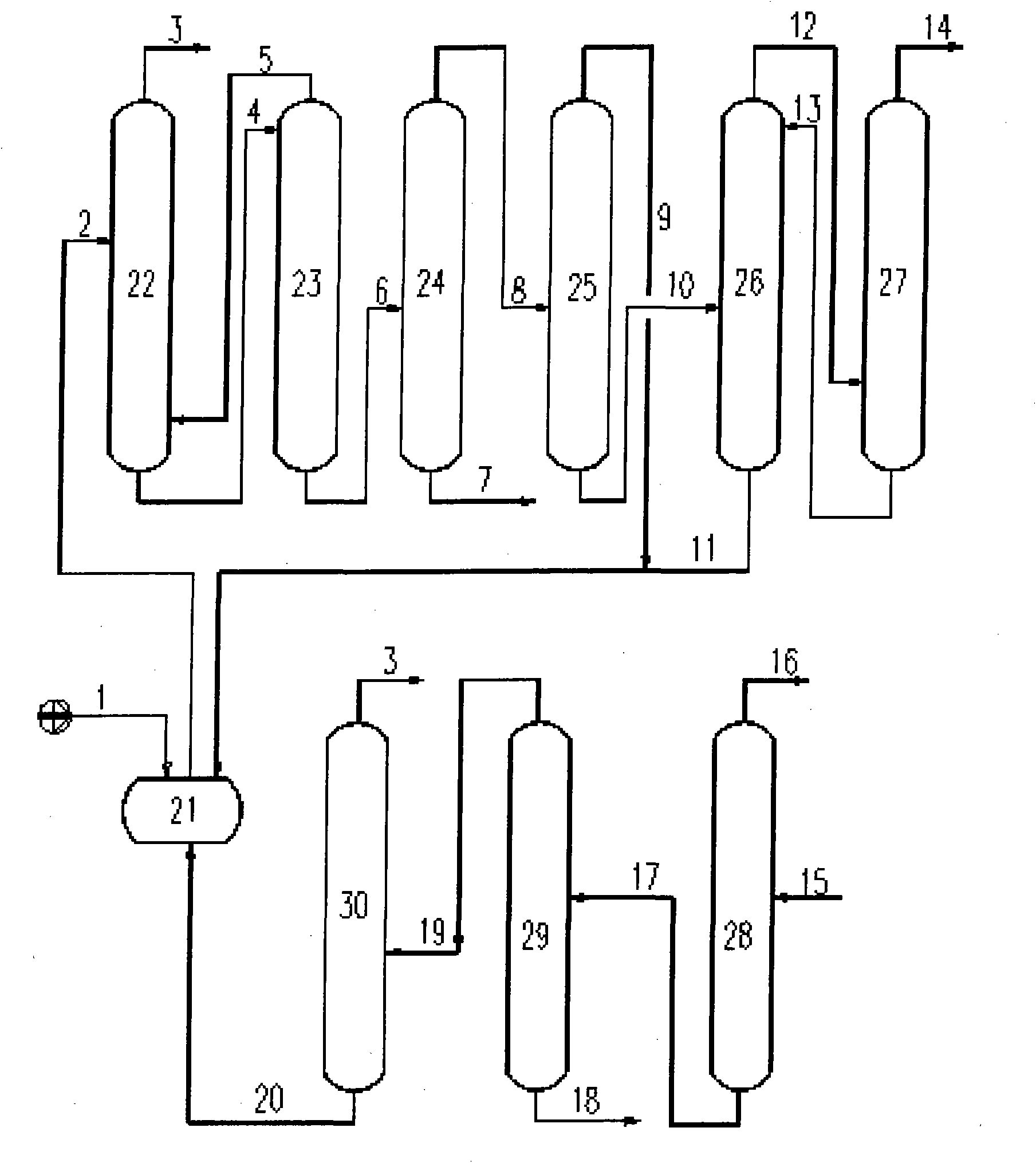

System for separating and purifying trichlorosilane in production process of polysilicon and operation method thereof

ActiveCN101538044ALow impurity contentMeet production requirementsChemical industryHalogenated silanesProcess engineeringTower

The invention provides a system for separating and purifying trichlorosilane in production process of polysilicon and an operation method thereof. The system consists of a rectification working section and a recovery refining working section; wherein, the rectification working section comprises six towers, and the recovery refining working section includes three towers; the connection mode of the six towers of the rectification working section is that a lightness-removing tower I, a lightness-removing tower II, a weight-removing tower, a secondary lightness-removing tower, a secondary weight-removing tower I and a secondary weight-removing tower II are sequentially connected with each other; the connection mode of the three towers of the recovery refining working section is that a lower-removing tower, a higher-removing tower and a product refining tower are sequentially connected with each other. Chlorsilane rectification technical equipment can be one of main technical bottlenecks limiting the production of the high-quality polysilicon material in China. The invention can achieve the separation requirements and energy-saving aim under the condition that the mass flow rate elastic ratio between feeding of the rectification working section and feeding of the recovery working section is 1:1-1:5. The rectification technique is simplified and optimized, the separation efficiency is improved, the energy consumption of rectification products is reduced, the reliability and stability of system operation can be enhanced, and the content of phosphorus, arsenic, boron and metallic contamination in the rectification products can be lowered.

Owner:TIANJIN UNIV

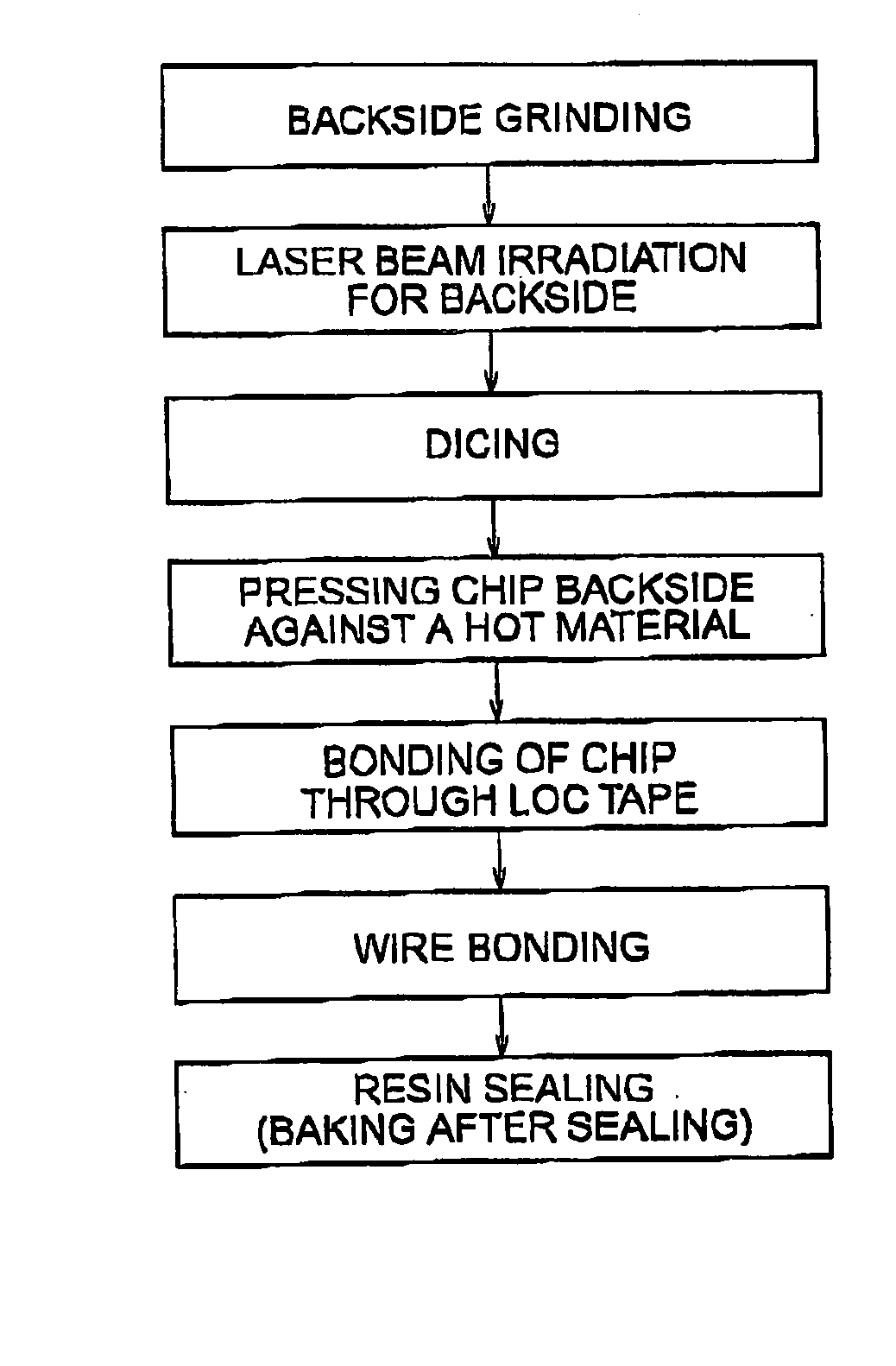

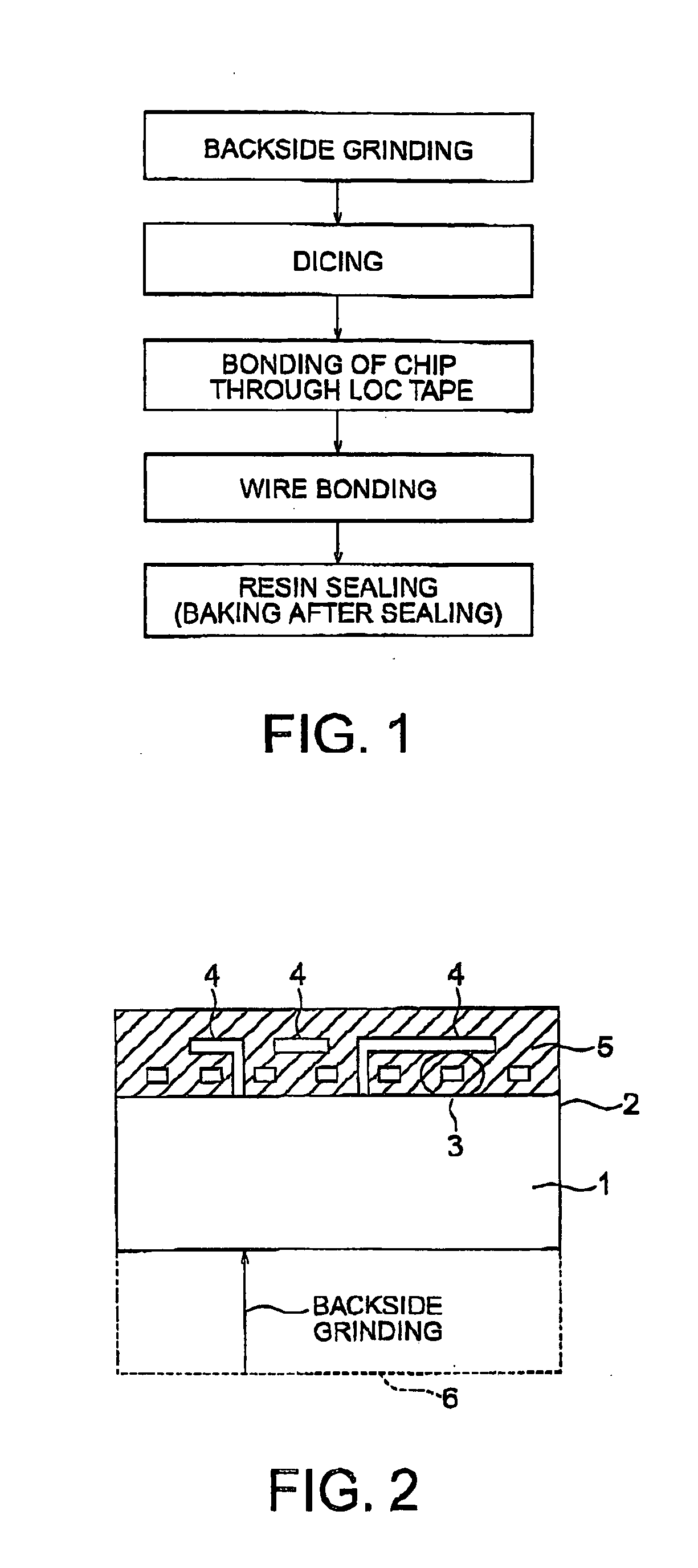

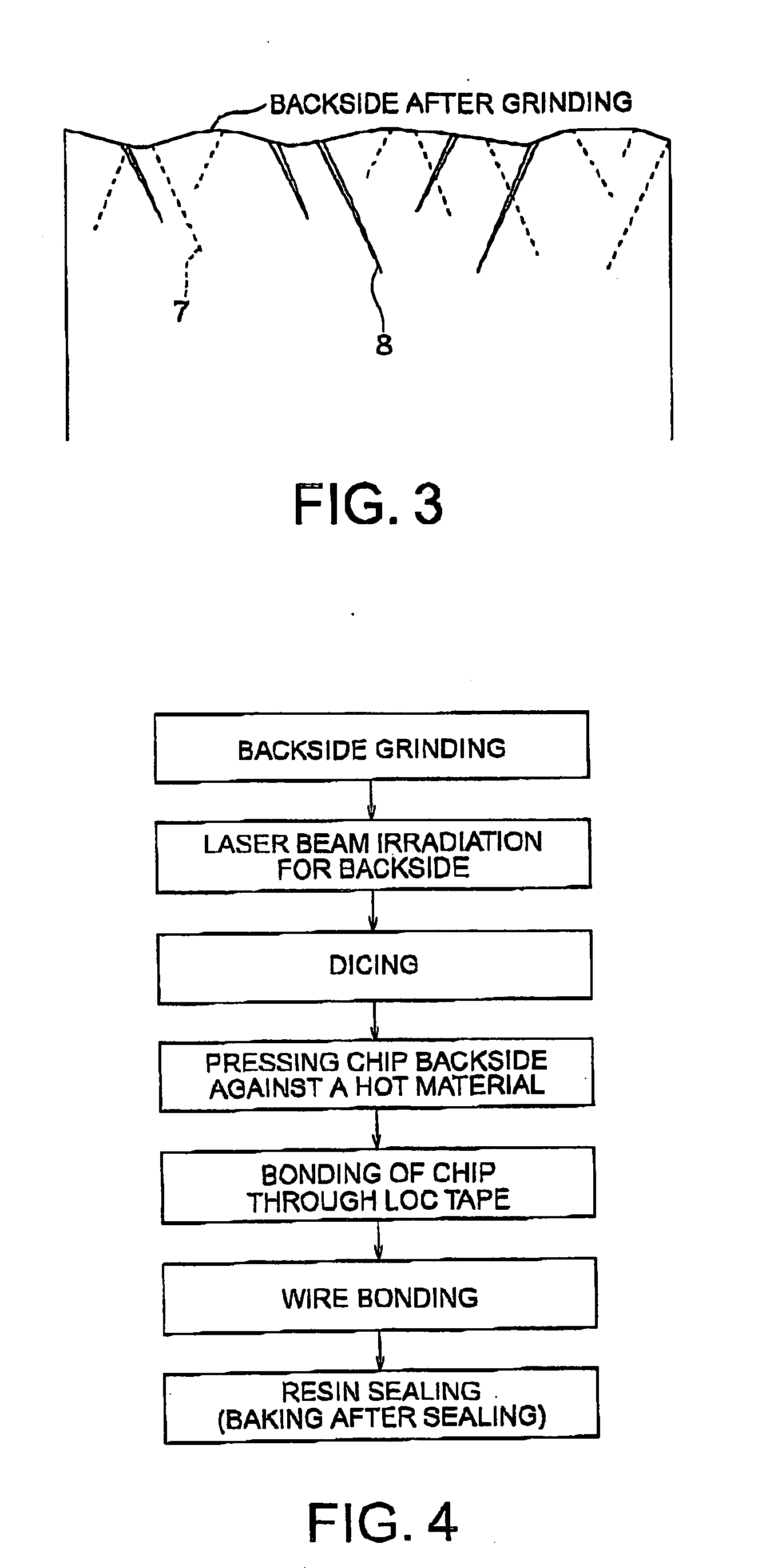

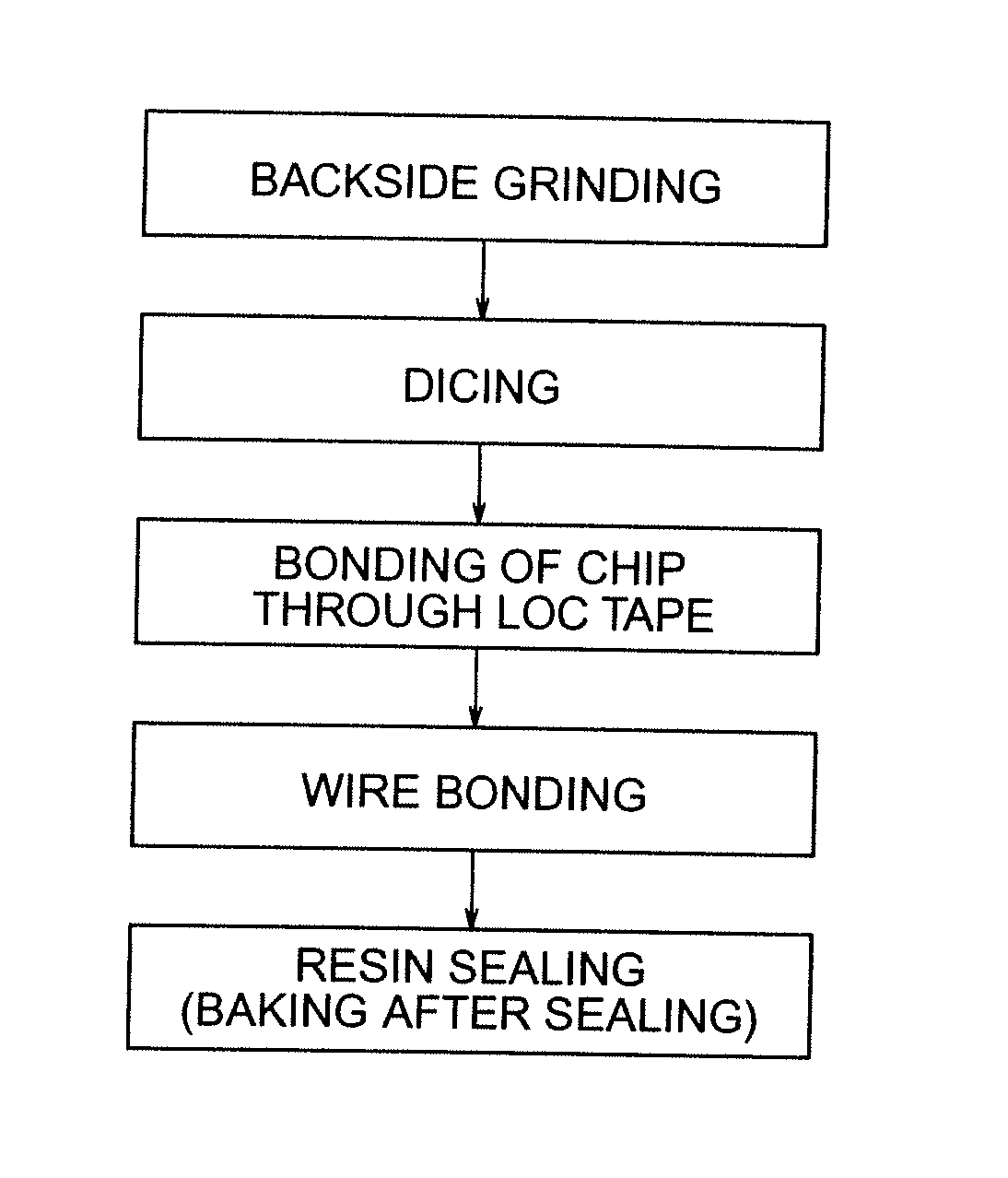

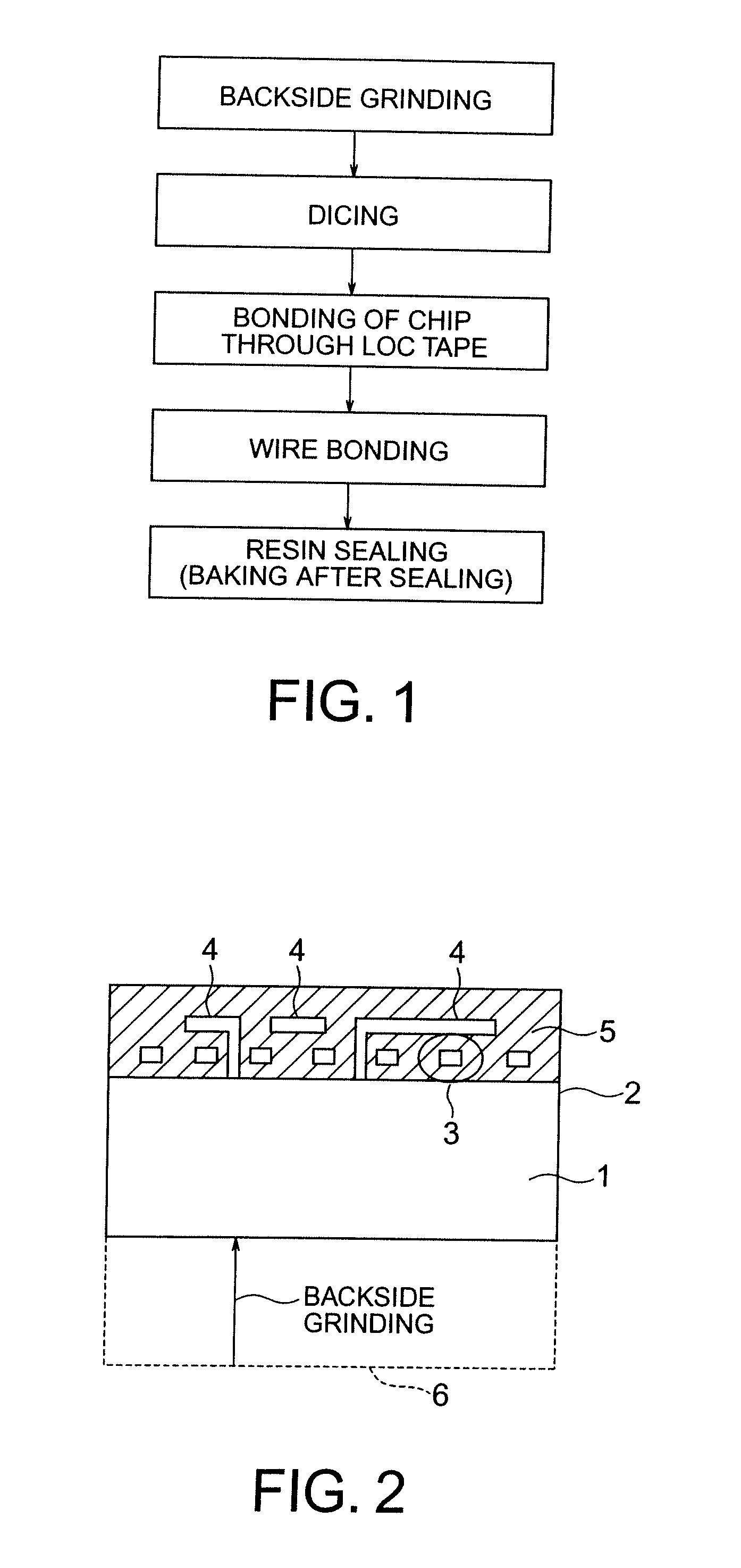

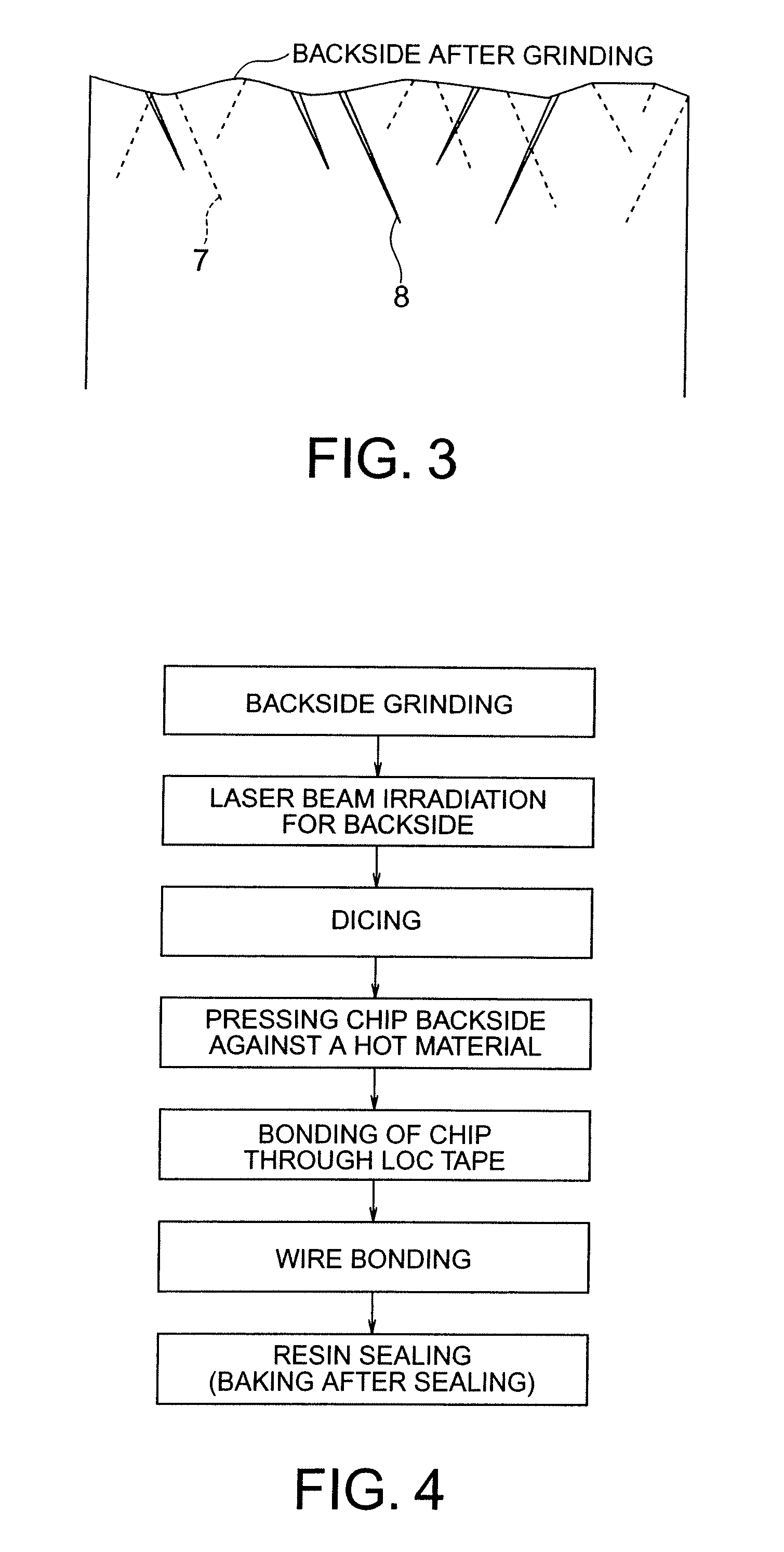

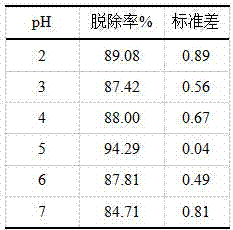

Semiconductor device and manufacturing method thereof

InactiveUS20050214973A1Prevent characteristic deteriorationReduce concentrationSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

In manufacturing a semiconductor device, the first gettering layer is formed on the backside of a wafer, and the second gettering layers are then formed on the backside and side surfaces of a chip, allowing these gettering layers to serve as trapping sites against metallic contamination that generated after backside grinding in assembly processes.

Owner:ELPIDA MEMORY INC

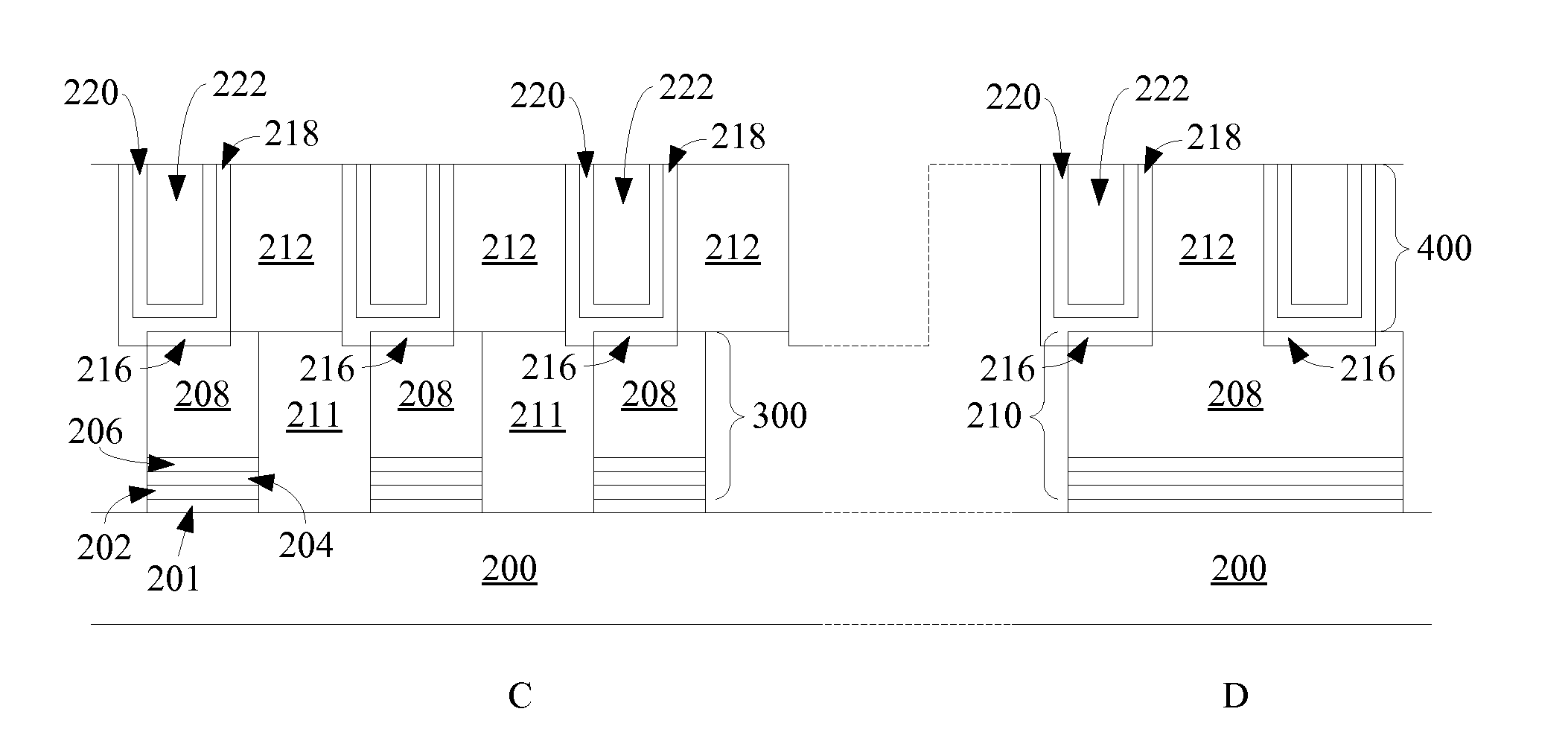

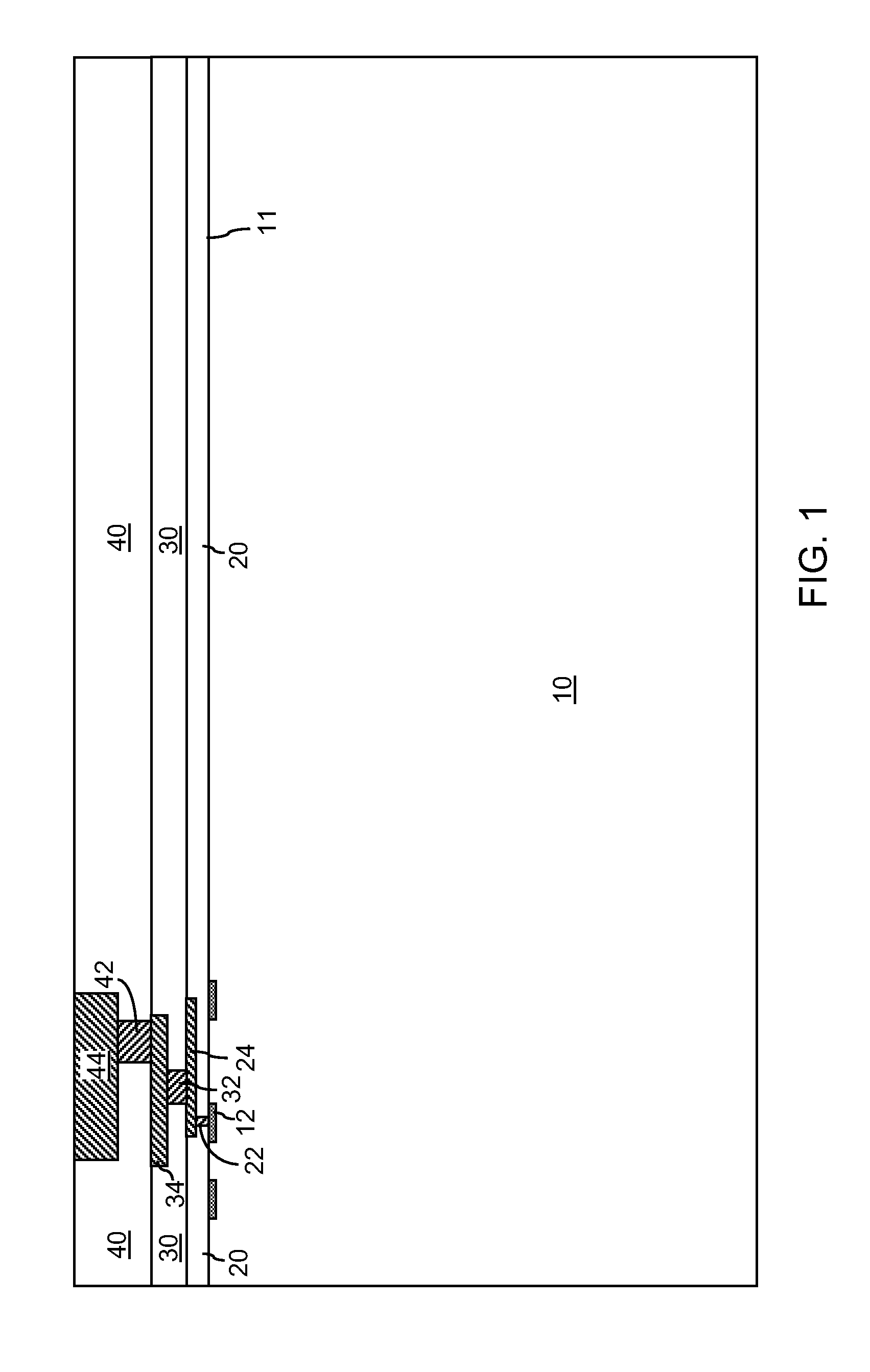

Trench metal-insulator-metal (MIM) capacitors and method of fabricating same

The present invention relates to a semiconductor device that contains a trench metal-insulator-metal (MIM) capacitor and a field effect transistor (FET). The trench MIM capacitor comprises a first metallic electrode layer located over interior walls of a trench in a substrate, a dielectric layer located in the trench over the first metallic electrode layer, and a second metallic electrode layer located in the trench over the dielectric layer. The FET comprises a source region, a drain region, a channel region between the source and drain regions, and a gate electrode over the channel region. The trench MIM capacitor is connected to the FET by a metallic strap. The semiconductor device of the present invention can be fabricated by a process in which the trench MIM capacitor is formed after the FET source / drain region but before the FET source / drain metal silicide contacts, for minimizing metal contamination in the FET.

Owner:GLOBALFOUNDRIES US INC

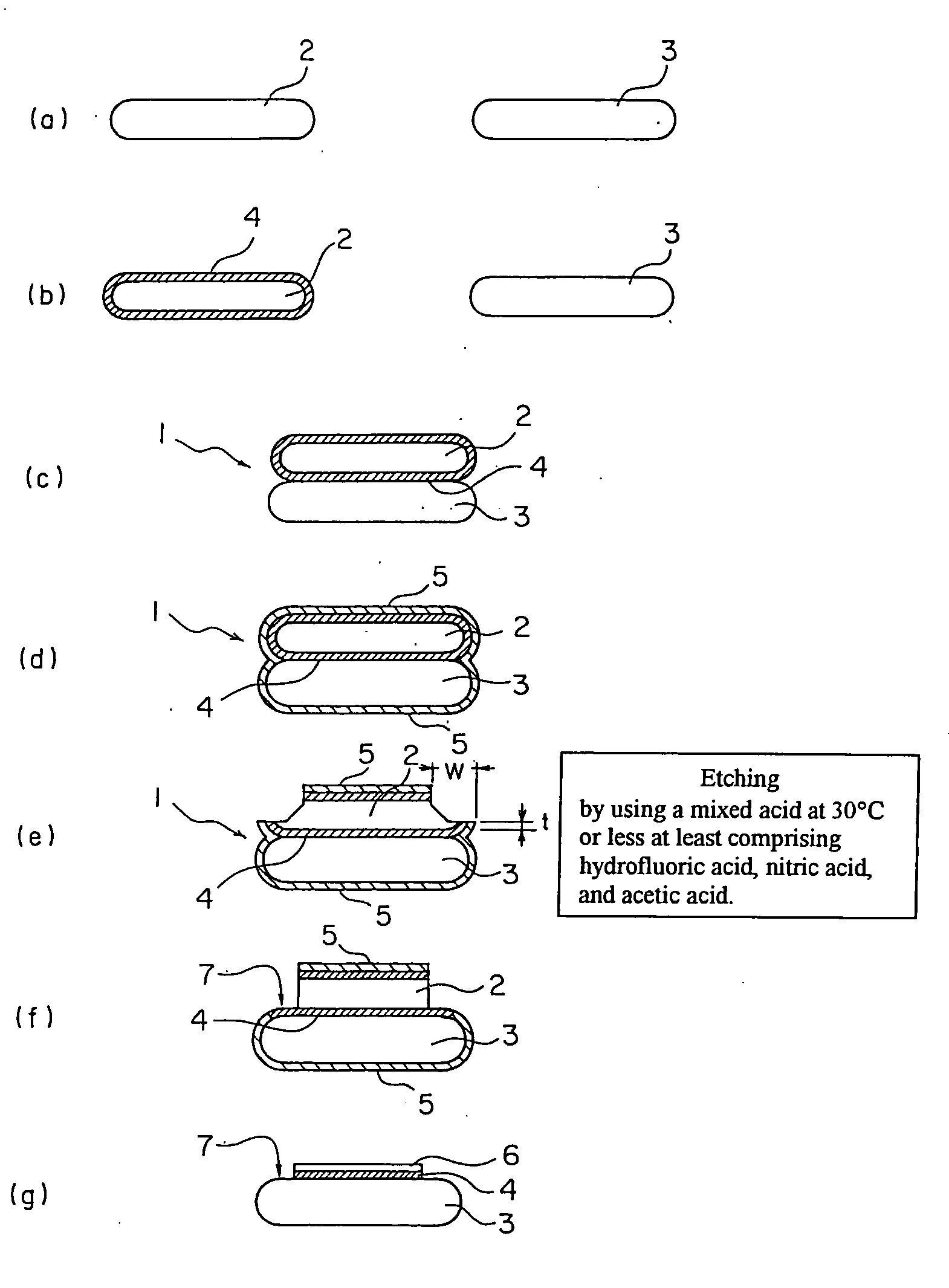

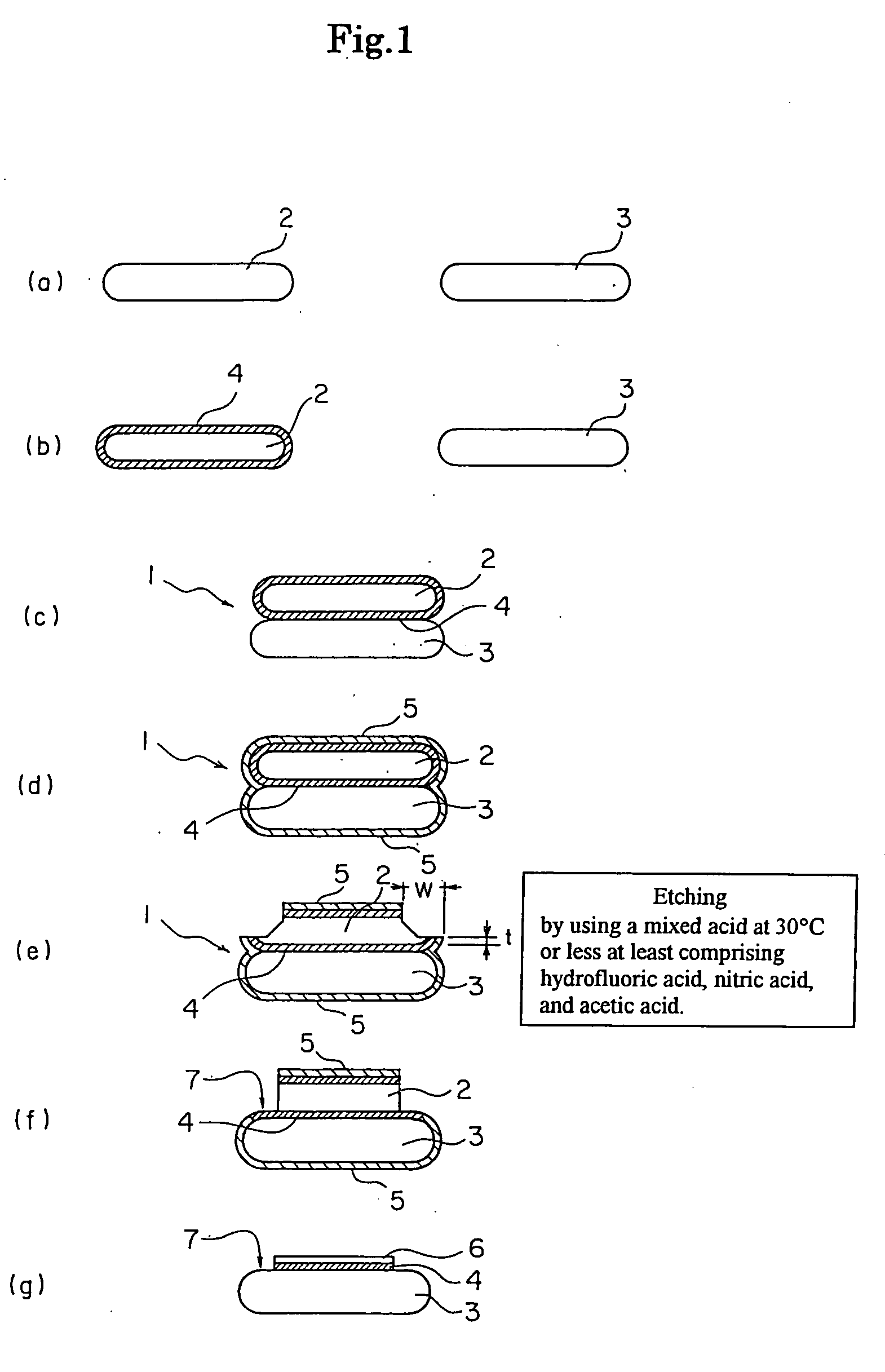

Method for manufacturing bonded wafer

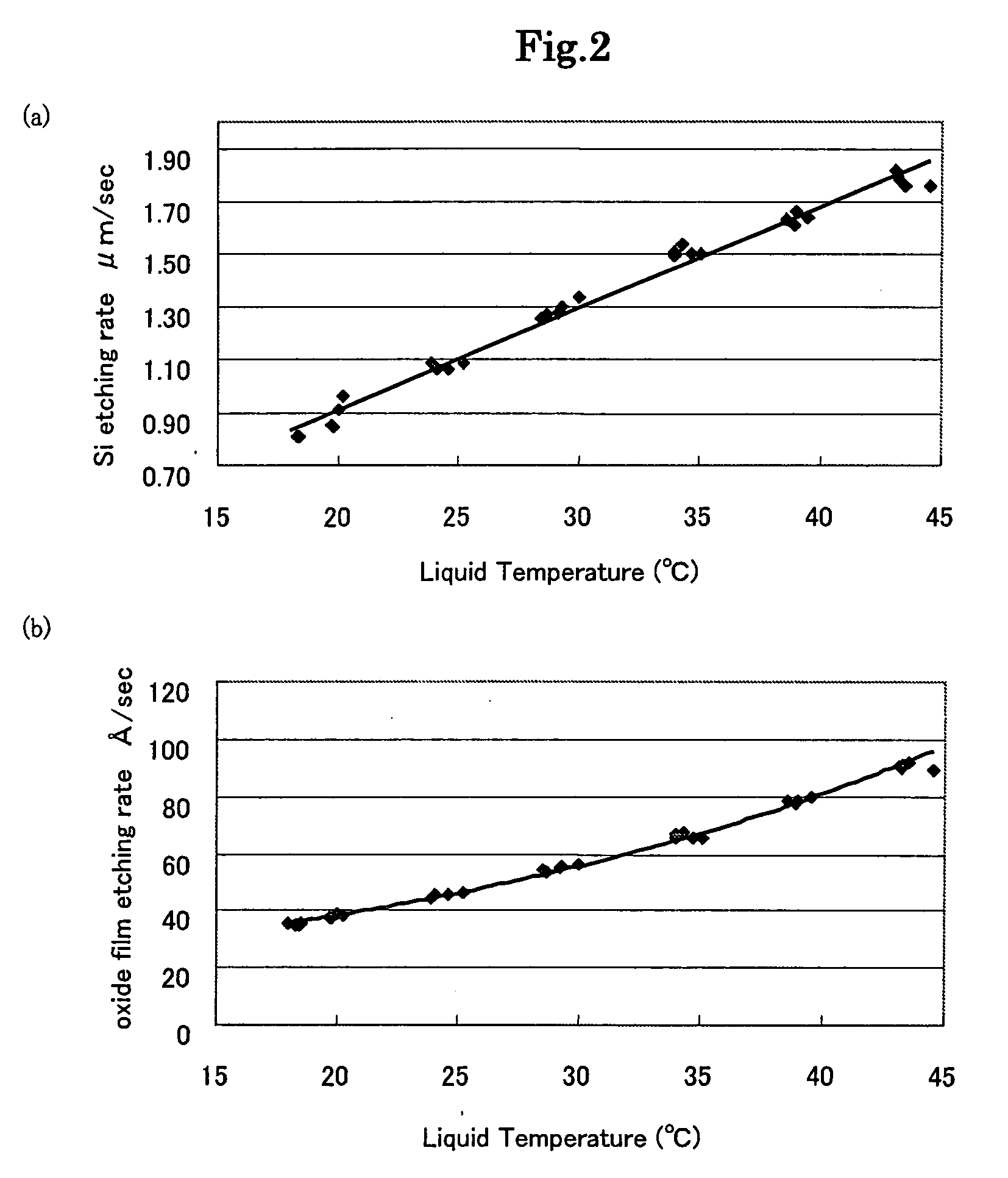

ActiveUS20090111245A1Reduce etch rateNot to damageSemiconductor/solid-state device manufacturingHydrofluoric acidEtching

The present invention provides a method for manufacturing a bonded wafer comprising steps of forming an oxide film on at least a surface of a base wafer or a surface of a bond wafer; bringing the base wafer and the bond wafer into close contact via the oxide film; subjecting these wafers to a heat treatment under an oxidizing atmosphere to bond the wafers together; grinding and removing the outer periphery of the bond wafer so that the outer periphery has a predetermined thickness; subsequently removing an unbonded portion of the outer periphery of the bond wafer by etching; and then thinning the bond wafer so that the bond wafer has a desired thickness, wherein the etching is conducted by using a mixed acid at 30° C. or less at least comprising hydrofluoric acid, nitric acid, and acetic acid. Thus there is provided a method for manufacturing a bonded wafer by which unbonded portions of the outer periphery of the bond wafer are removed with a high selectivity ratio (RSi / RSiO2) without causing metallic contamination.

Owner:SHIN-ETSU HANDOTAI CO LTD

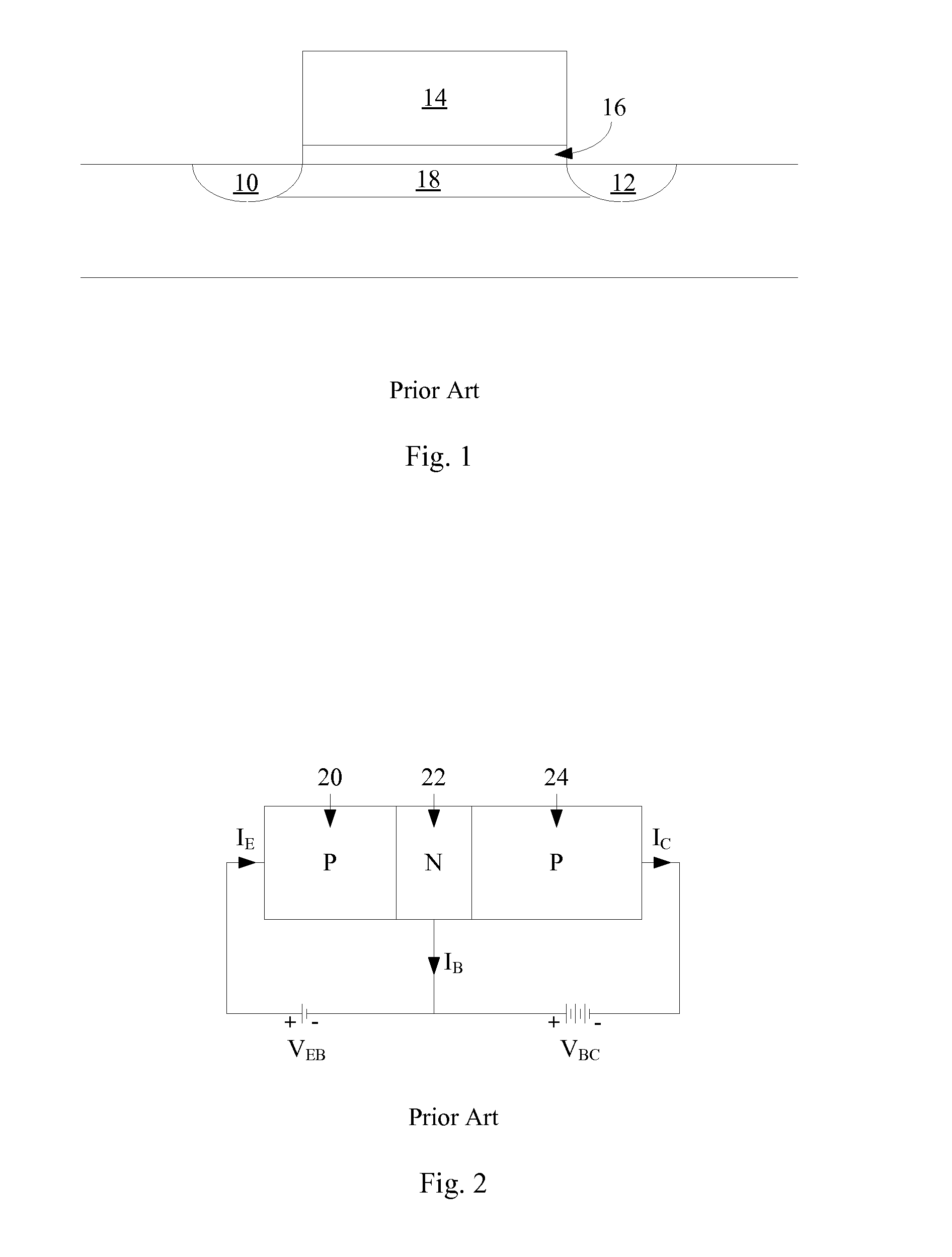

Method to form low-defect polycrystalline semiconductor material for use in a transistor

ActiveUS20080311710A1Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductor materialsGermanide

A method is described for forming a thin film transistor having its current-switching region in polycrystalline semiconductor material which has been crystallized in contact with titanium silicide, titanium silicide-germanide, or titanium germanide. The titanium silicide, titanium silicide-germanide, or titanium germanide is formed having feature size no more than 0.25 micron in the smallest dimension. The small feature size tends to inhibit the phase transformation from C49 to C54 phase titanium silicide. The C49 phase of titanium silicide has a very close lattice match to silicon, and thus provides a crystallization template for the silicon as it forms, allowing formation of large-grain, low-defect silicon. Titanium does not tend to migrate through the silicon during crystallization, limiting the danger of metal contamination. In preferred embodiments, the transistors thus formed may be, for example, field-effect transistors or bipolar junction transistors.

Owner:SANDISK TECH LLC

Preparation of metal doped diamond-like surface ion liquid lubricant self-assembled lubricating film

InactiveCN101463466AImprove tribological propertiesExcellent friction reductionVacuum evaporation coatingSputtering coatingCarbon filmDiamond-like carbon

The invention discloses a method for preparing a metallic contamination adamantine surface ionic liquid lubricant self-assembly lubricative film. The method takes ionic liquid lubricant as raw material, adopts magnetron sputtering equipment to prepare a metallic contamination adamantine carbon film and assembles the liquid lubricant film which is stable, uniform and ordered on the carbon film. The method is characterized in that the preparation process is operated at normal temperature, and the requirements for the material and the shape of a substrate are lower; the film is stable and uniform, and has lower surface roughness; the film also has good performances on antifriction, wear resistance and adhesion resistance. The test of friction and wear proves that the ionic liquid lubricant and adamantine has good combining performance and better performances on antifriction, wear resistance and adhesion resistance, so that the lubricative film is expected to become the effective means of solving the problems of protecting and lubricating materials I the technical fields such as space machinery, information technology, etc.

Owner:LANZHOU INST OF CHEM PHYSICS CHINESE ACAD OF SCI

Polishing Composition for Silicon Wafer

InactiveUS20090127501A1Avoid Metal ContaminationHigh removal rateOther chemical processesSemiconductor/solid-state device manufacturingWaferingCopper contamination

The present invention relates to a polishing composition for silicon wafer comprising silica, a basic compound, a polyaminopolycarboxylic acid compound having hydroxy group, and water. The polishing composition can prevent metal contamination by nickel, chromium, iron, copper or the like, particularly copper contamination in polishing of silicon wafer.

Owner:NISSAN CHEM IND LTD

Process for metallic contamination reduction in silicon wafers

A process for removing a contaminant selected from among copper, nickel, and a combination thereof from a silicon wafer having a surface and an interior. The process comprises cooling the silicon wafer in a controlled atmosphere from a temperature at or above an oxidation initiation temperature and initiating a flow of an oxygen-containing atmosphere at said oxidation initiation temperature to create an oxidizing ambient around the silicon wafer surface to form an oxide layer on the silicon wafer surface and a strain layer at an interface between the oxide layer and the silicon wafer interior. The cooling of the wafer is also controlled to permit diffusion of atoms of the contaminant from the silicon wafer interior to the strain layer. Then the silicon wafer is then cleaned to remove the oxide layer and the strain layer, thereby removing said contaminant having diffused to the strain layer.

Owner:MEMC ELECTONIC MATERIALS INC

Etchant, etching method and semiconductor silicon waffer

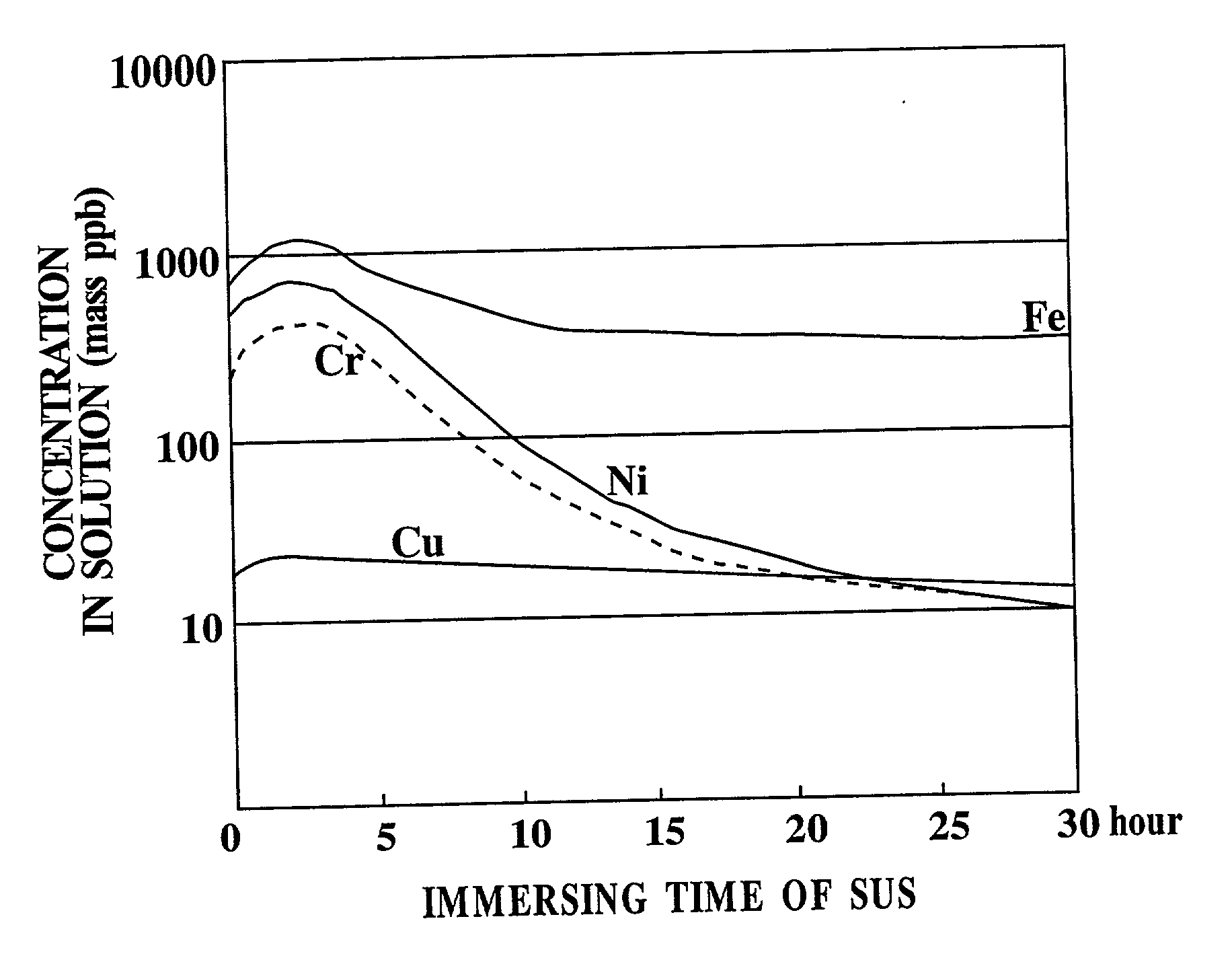

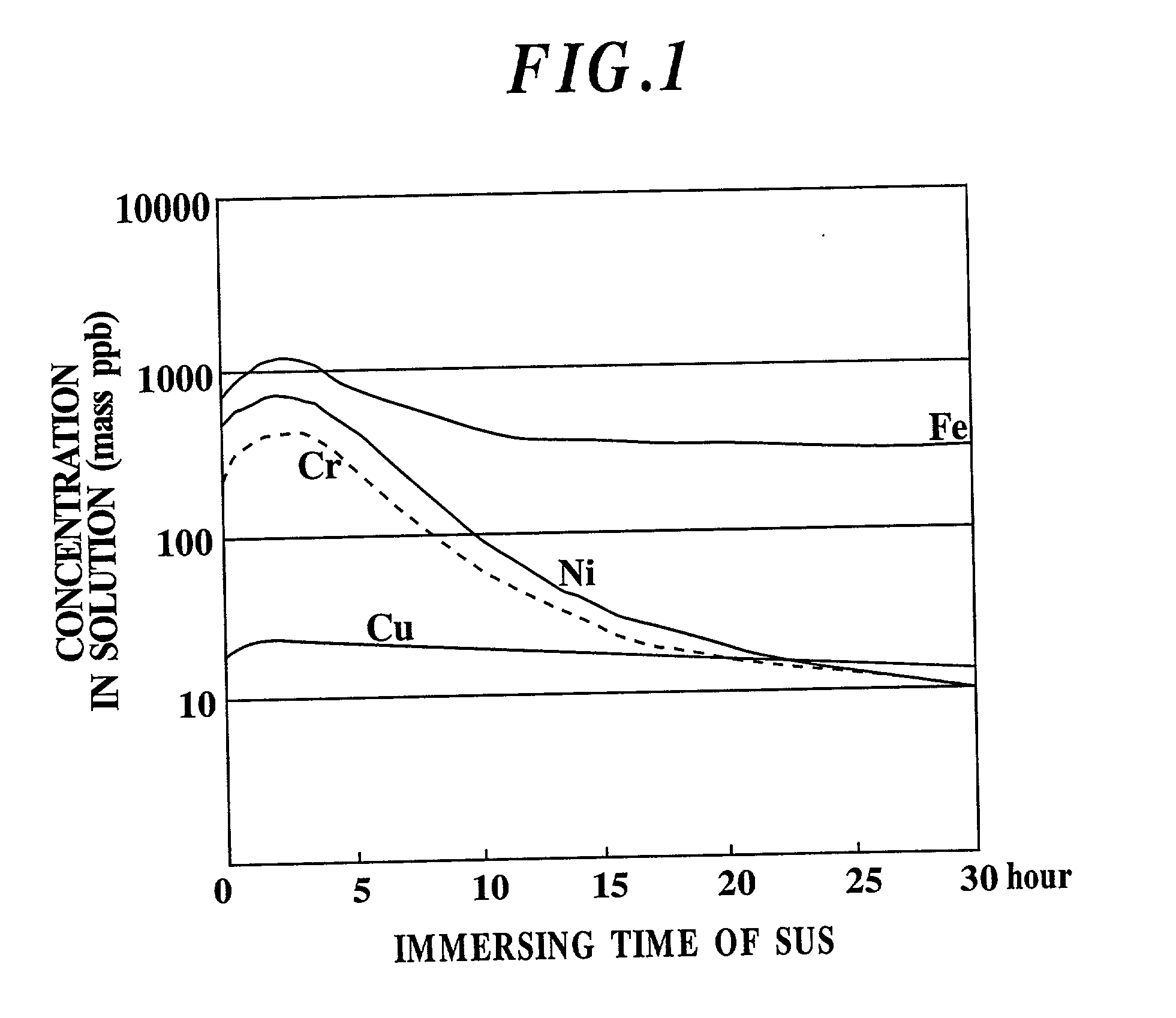

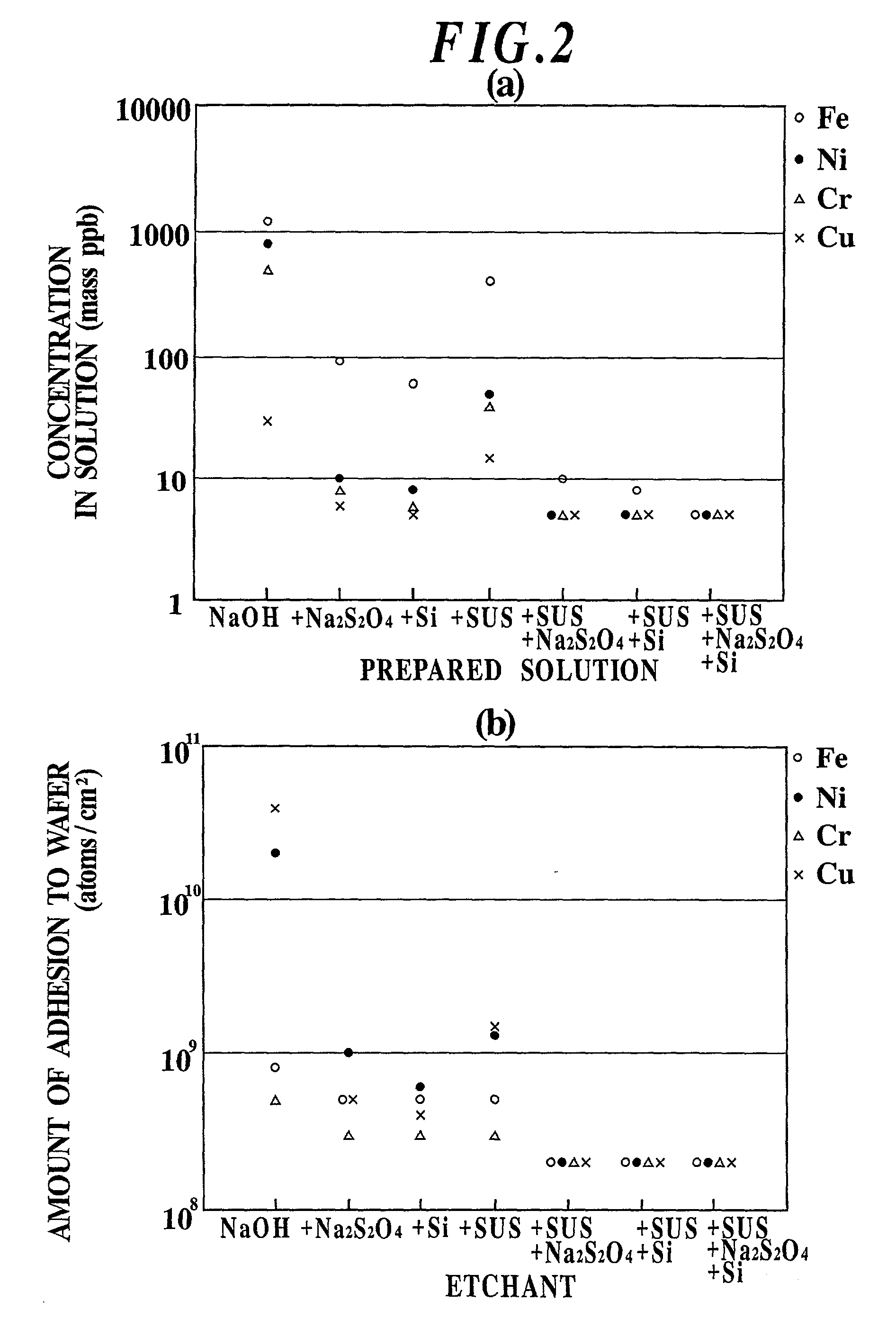

InactiveUS20030008504A1Reduce metal pollutionReduce concentrationPolycrystalline material growthAfter-treatment detailsMetal contaminationAqueous solution

An etchant and an etching method that contribute to prevention of metal contamination of a semiconductor silicon wafer, and a semiconductor silicon wafer in which metal contamination is extremely reduced, are provided. The etchant according to the present invention is prepared by immersing stainless steel in an alkali aqueous solution for not less than 10 hours. In the etching method according to the present invention, a semiconductor silicon wafer is etched by using the etchant. Thereby, the semiconductor silicon wafer according to the present invention, in which metal contamination is extremely reduced, is obtained.

Owner:SHIN-ETSU HANDOTAI CO LTD

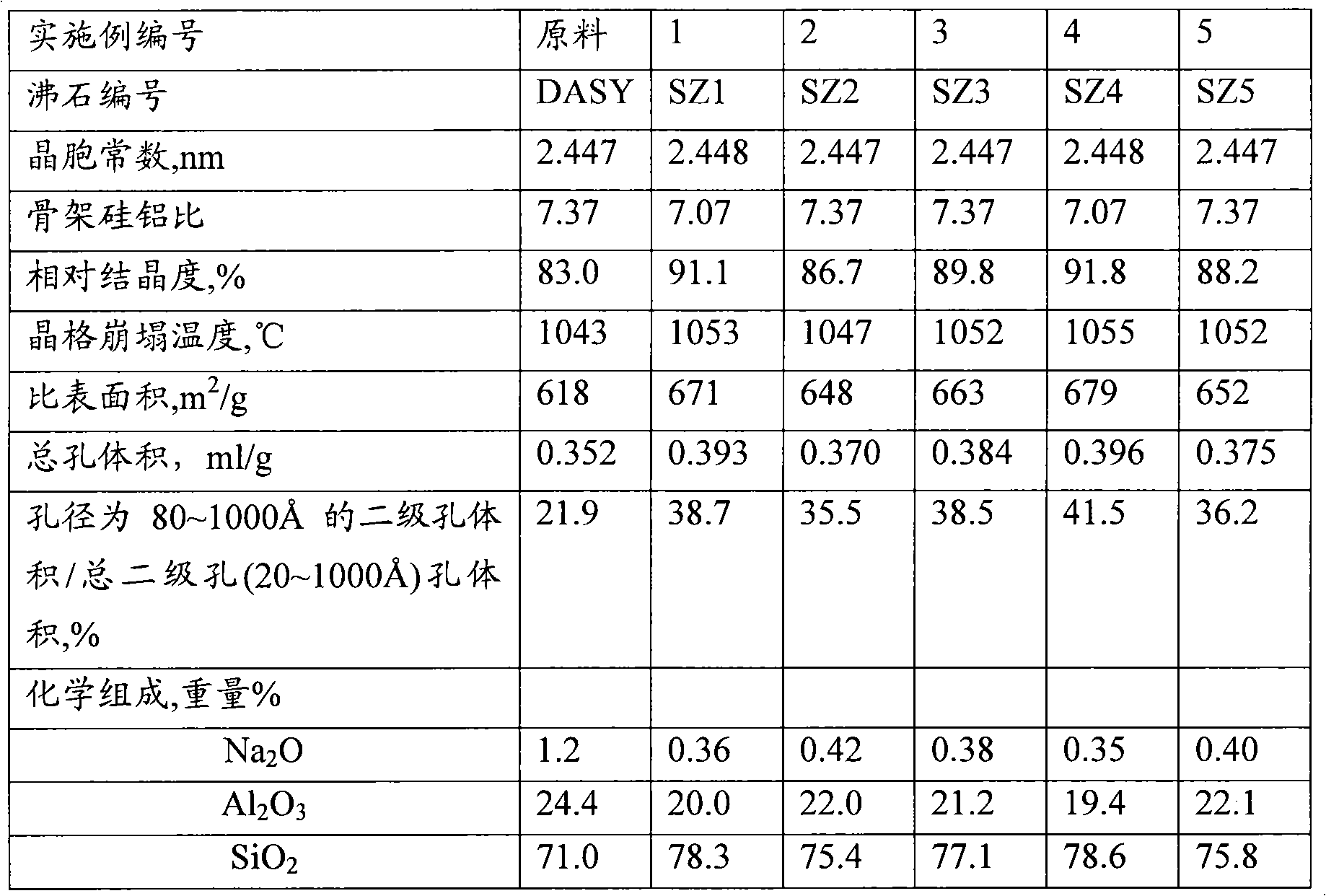

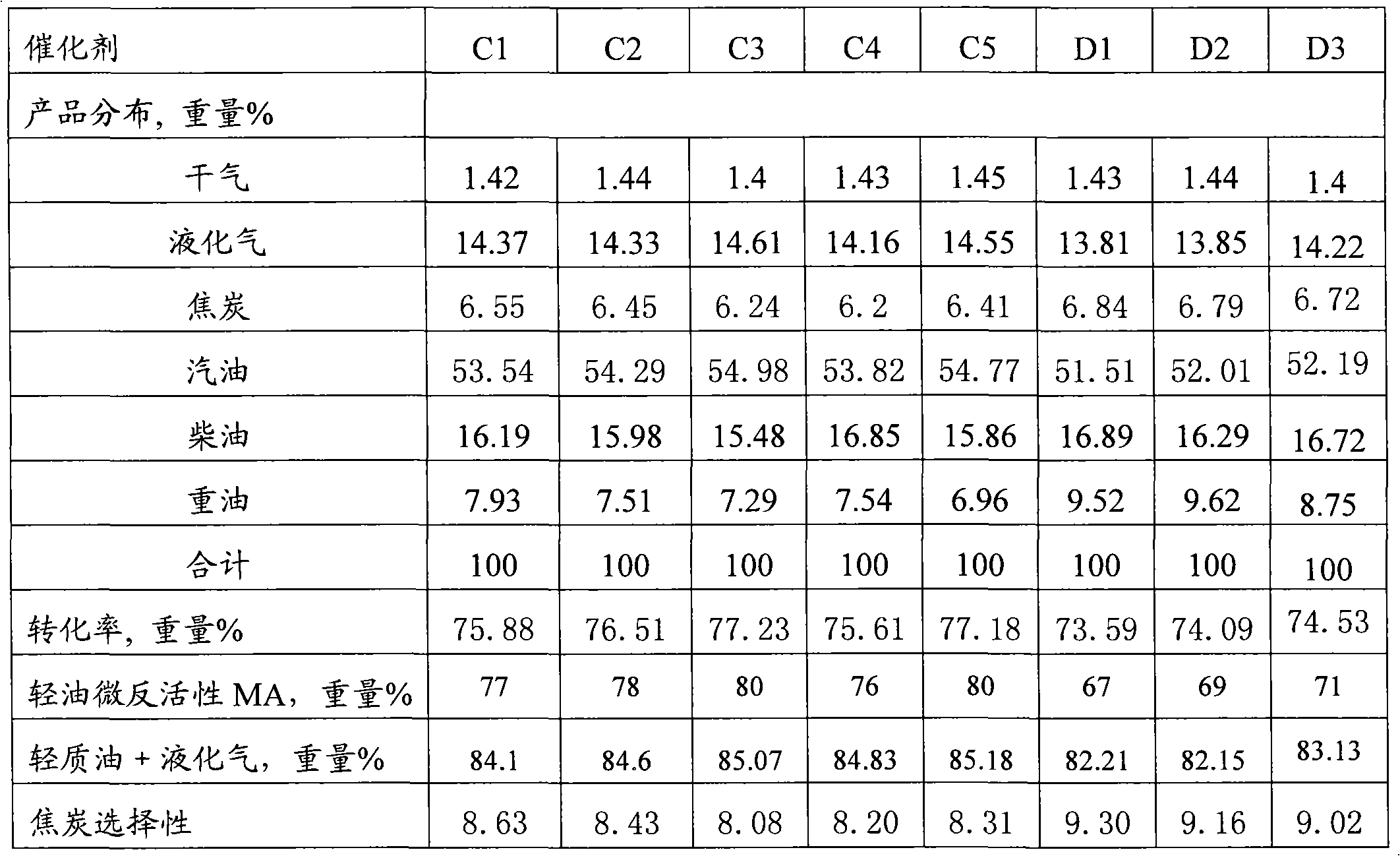

Heavy-oil cracking catalyst and preparation and application method thereof

ActiveCN101773845AImprove conversion abilityStrong resistance to heavy metalsCatalytic crackingMolecular sieve catalystsGasolineSlurry

The invention relates to a heavy-oil cracking catalyst and a preparation and application method thereof. The catalyst contains modified ultrastable Y-type zeolite and a composition, wherein the composition contains 45-94.9 percent of rectorite and 5-50 percent of first heatproof inorganic oxides by weight percent and 0.1-20 percent of assistant selected from compounds of Mn, P and Ce by element weight percent; and the ratio of silicate to aluminum of modified ultrastable Y-type zeolite is 6-15, the lattice constant is 2.440-2.458nm, and secondary holes with aperture of 80-100 account for 30-60 percent of the total secondary holes. The preparation method of the catalyst comprises that the composition is prepared, the composition and the modified ultrastable Y-type zeolite are mixed and are crushed into slurry, and the slurry is spayed and dried. The anti-metallic contamination capacity of the catalyst is high, the coke selectivity is good, the catalyst can be used for heavy-oil catalytic cracking, the heavy-oil conversion rate is high, the gasoline yield is high and the total yield of liquefied gas, gasoline and diesel is high.

Owner:CHINA PETROLEUM & CHEM CORP +1

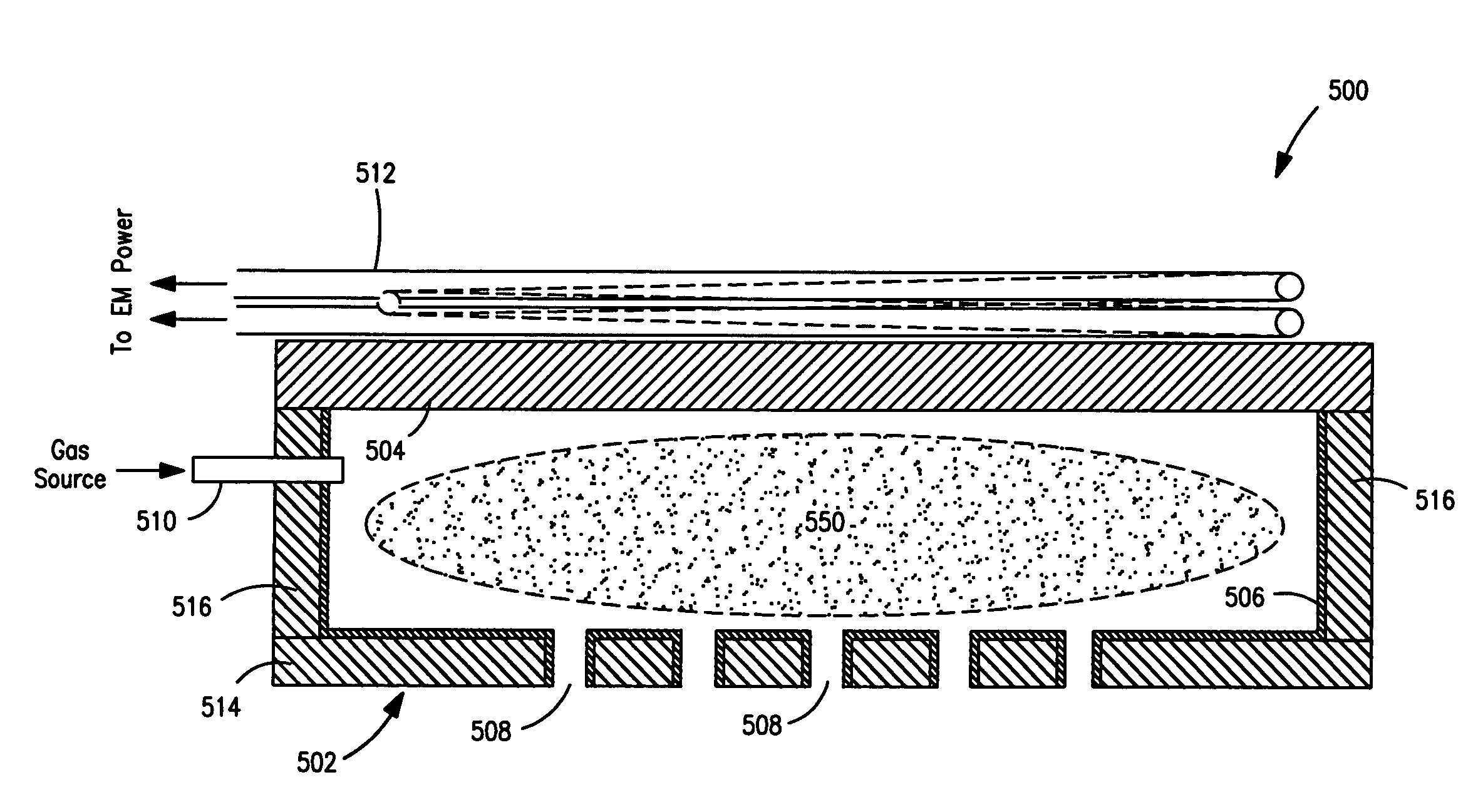

RF electron source for ionizing gas clusters

InactiveUS20090166555A1Eliminating contributorMaterial analysis by optical meansIon beam tubesGas cluster ion beamInductively coupled plasma

The present invention discloses a system and method for generating gas cluster ion beams (GCIB) having very low metallic contaminants. Gas cluster ion beam systems are plagued by high metallic contamination, thereby affecting their utility in many applications. This contamination is caused by the use of thermionic sources, which impart contaminants and are also susceptible to short lifecycles due to their elevated operating temperatures. While earlier modifications have focused on isolating the filament from the source gas cluster as much as possible, the present invention represents a significant advancement by eliminating the thermionic source completely. In the preferred embodiment, an inductively coupled plasma and ionization region replaces the thermionic source and ionizer of the prior art. Through the use of RF or microwave frequency electromagnetic waves, plasma can be created in the absence of a filament, thereby eliminating a major contributor of metallic contaminants.

Owner:VARIAN SEMICON EQUIP ASSOC INC

Cleaning agent for electronic materials

InactiveUS8324143B2Improve reliabilityHigh yieldOrganic detergent compounding agentsOrganic chemistrySulfamic acidCleansing Agents

Provided is a cleaning agent for electronic materials, which enables very efficient advanced cleaning such that yield in the production of the electronic materials is improved and cleaning in a short period of time becomes possible, the cleaning agent having excellent cleaning power for fine-grained particles and organic matter and being able to reduce metallic contamination on the substrate. The cleaning agent for electronic materials comprises sulfamic acid (A), an anionic surfactant having at least one sulfonic acid group or a salt thereof in the molecule (B), a chelating agent (C), and water, wherein the pH at 25 C is preferably not more than 3.0 and the (B) is preferably a polymeric anionic surfactant (B1) having a weight average molecular weight of 1,000 to 2,000,000.

Owner:SANYO CHEM IND LTD

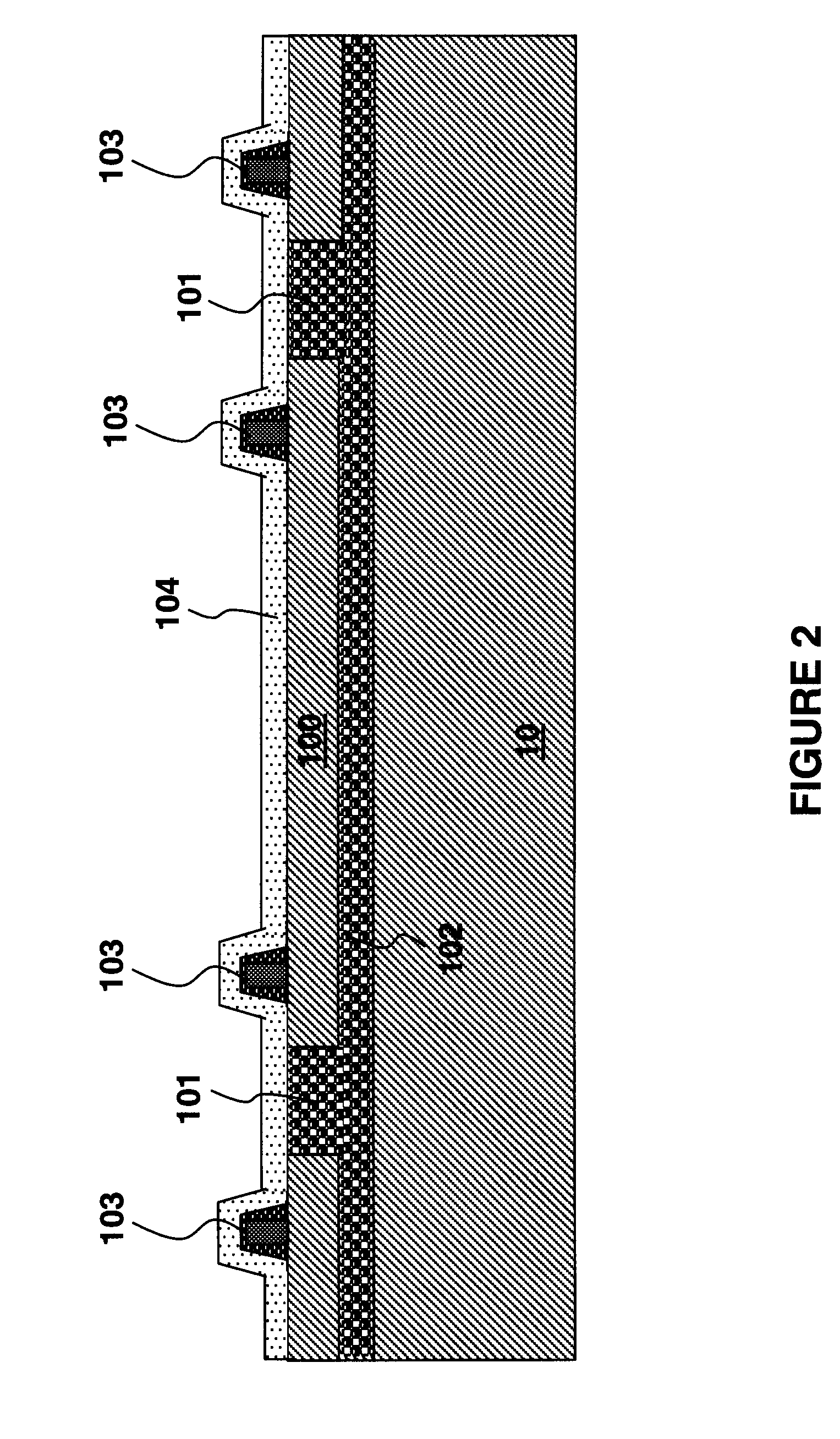

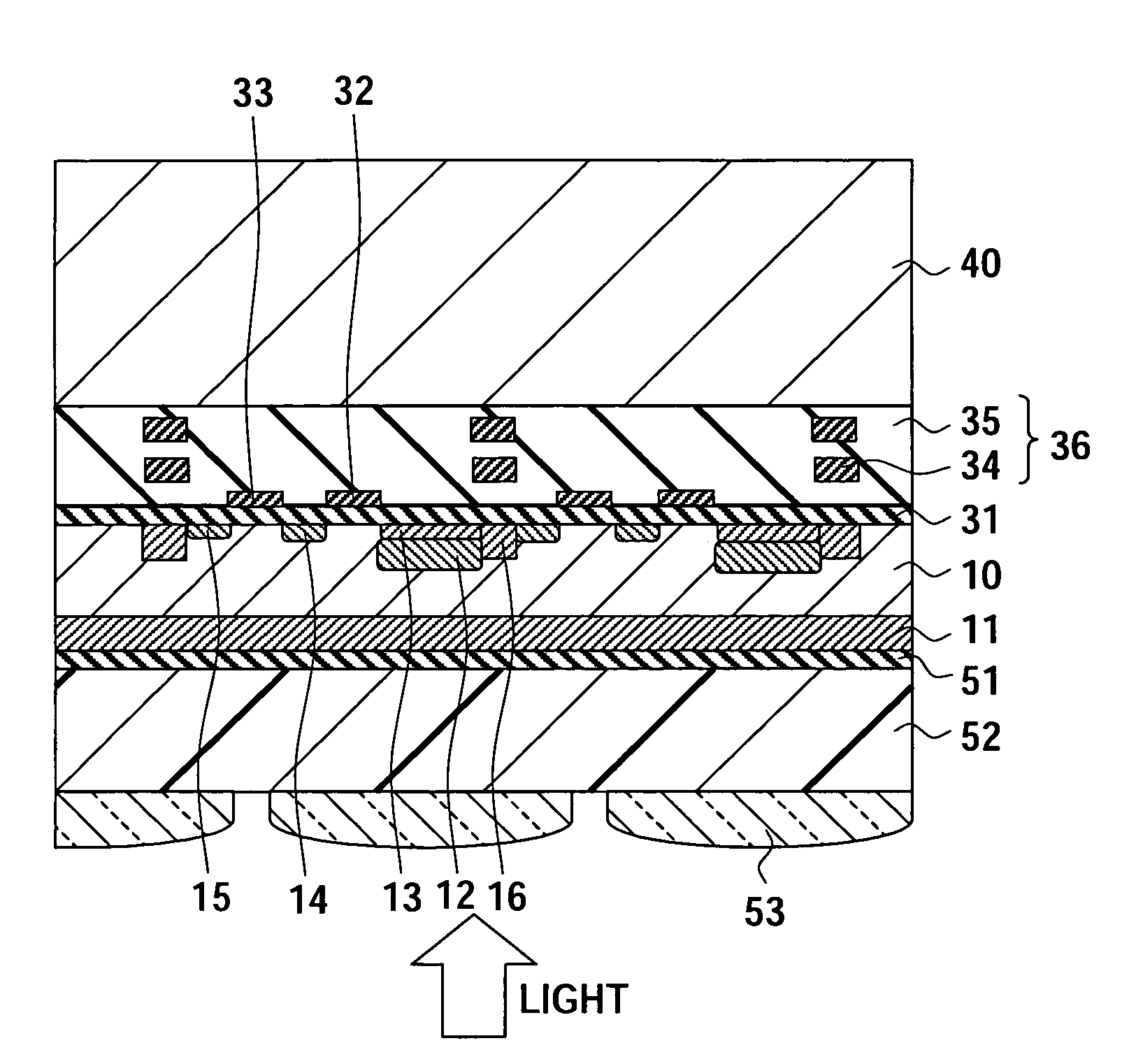

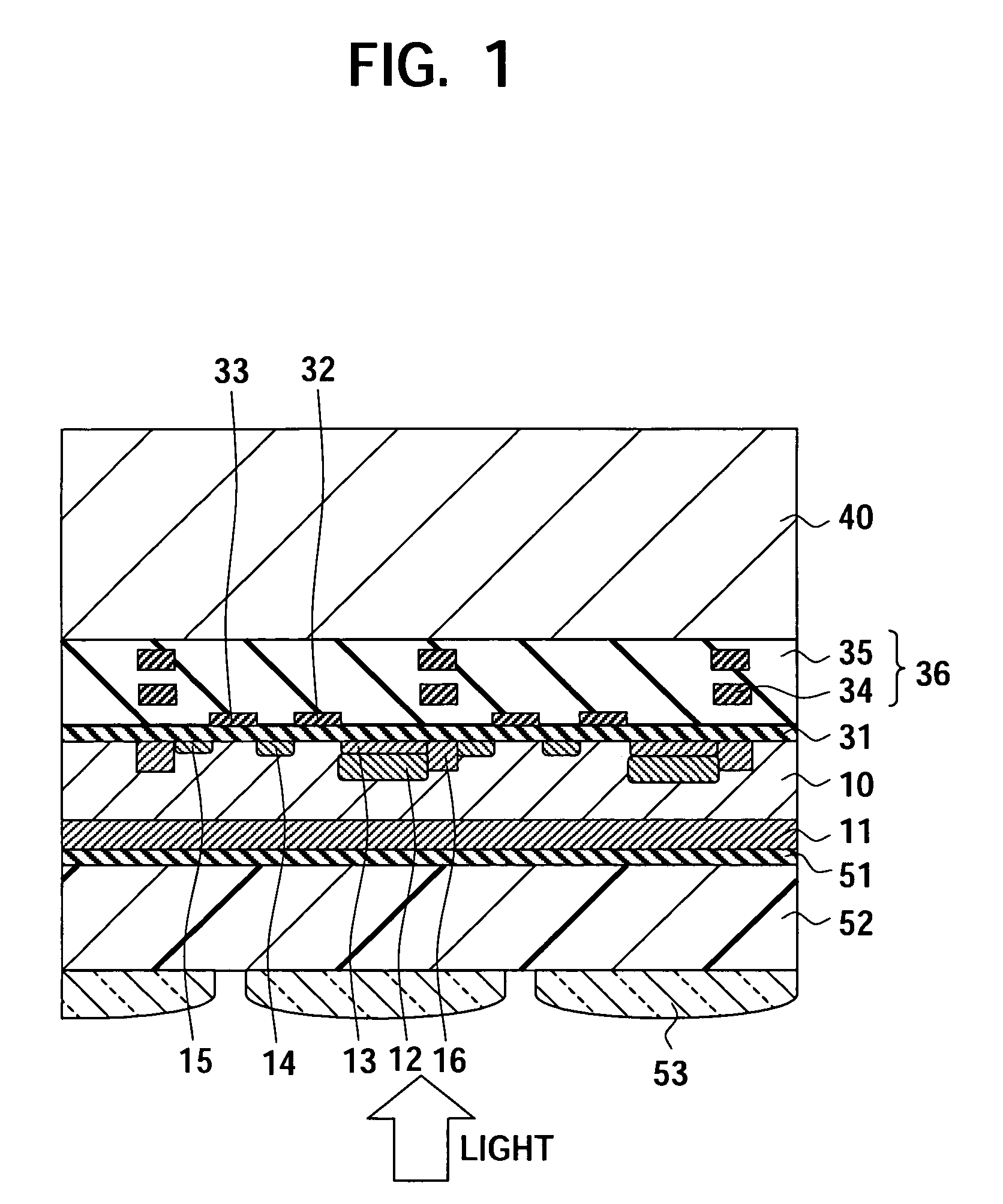

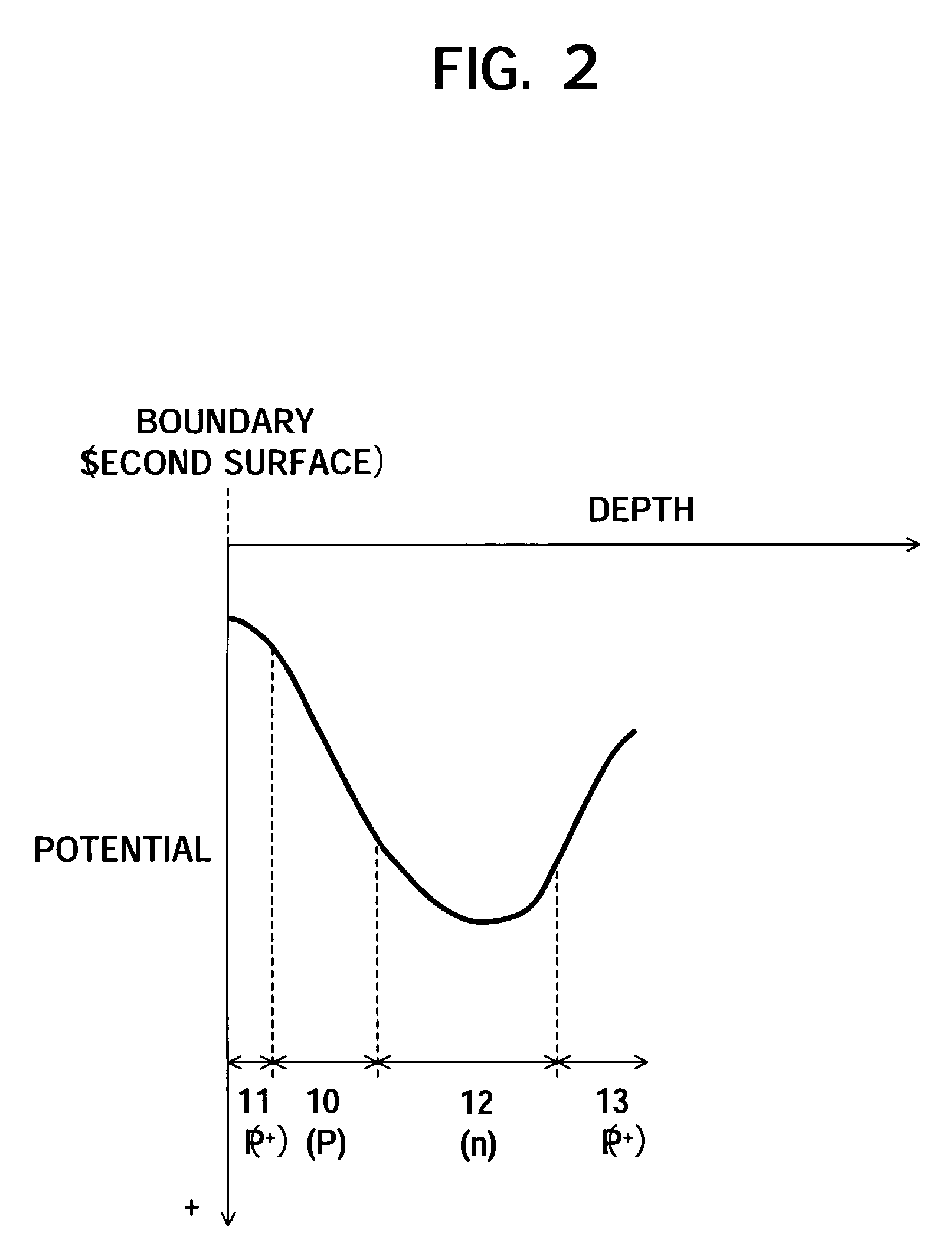

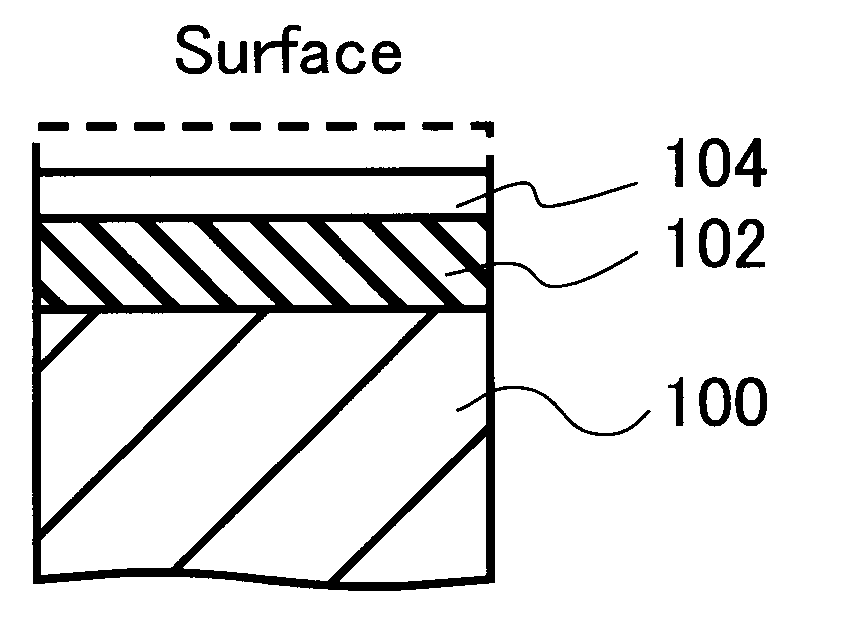

Solid-state imaging device, camera and method of producing the solid-state imaging device

InactiveUS7452742B2Suppress occurrenceSuppress of of sensibilityTelevision system detailsSolid-state devicesQuantum efficiencyPhotoelectric conversion

Owner:SONY CORP

Surface cleaning method of semiconductor wafer heat treatment boat

InactiveUS20080237190A1Efficiently and easily removing metallic contaminationKeep down production timeDecorative surface effectsSurface treatment compositionsSurface cleaningCleaning methods

A surface cleaning method of a semiconductor wafer heat treatment boat that can prevent metallic contamination to semiconductor wafers and keep down a production time and manufacturing costs of semiconductor wafers by efficiently and easily removing metallic impurities in an oxide film on an SiC boat surface is provided. A surface cleaning method of a semiconductor wafer heat treatment boat according to an embodiment of the present invention is a surface cleaning method of a semiconductor wafer heat treatment boat whose surface is formed of SiC, includes oxidizing the surface of the heat treatment boat by thermal oxidation and etching a portion of the oxide film formed after oxidation is removed.

Owner:COVALENT MATERIALS CORP

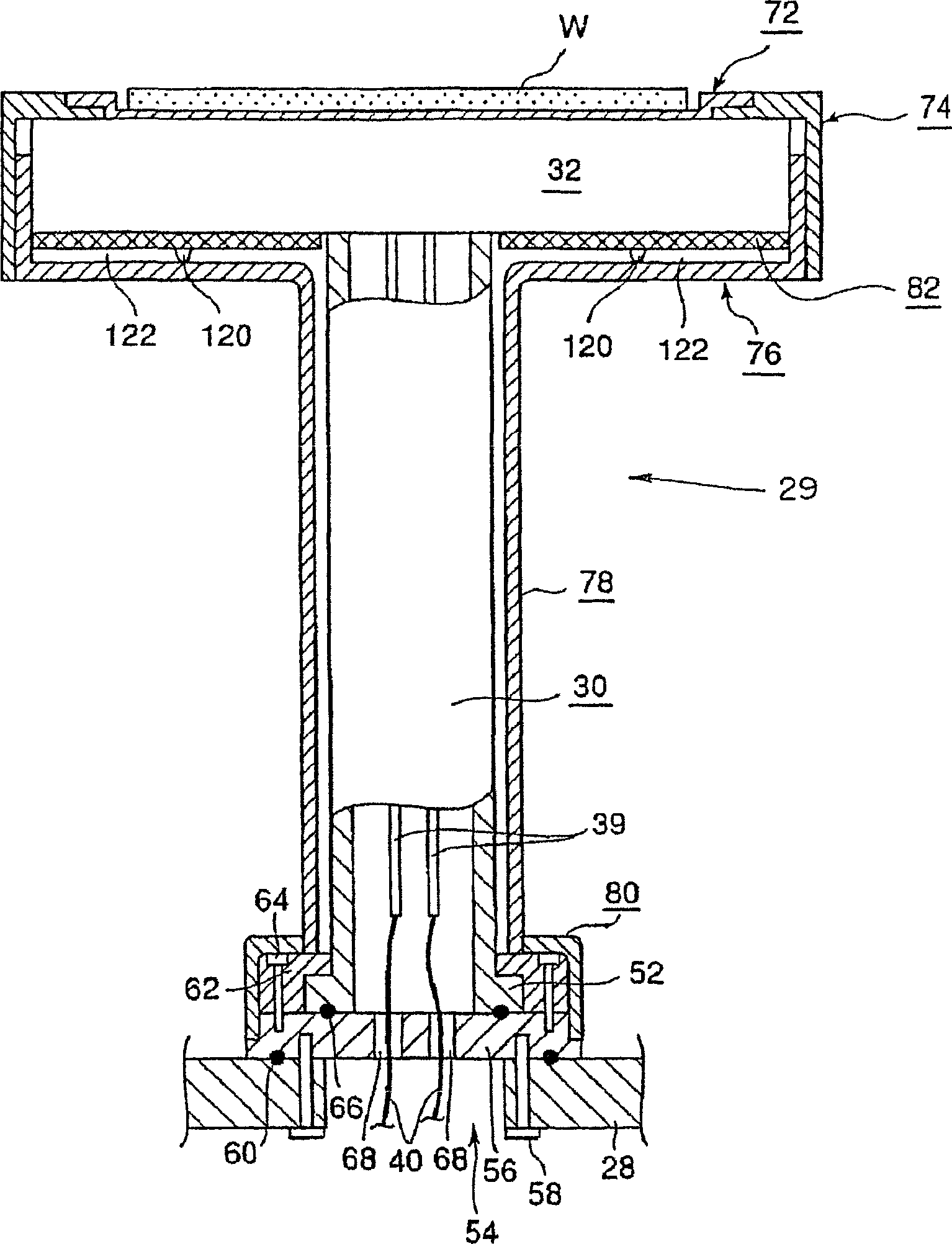

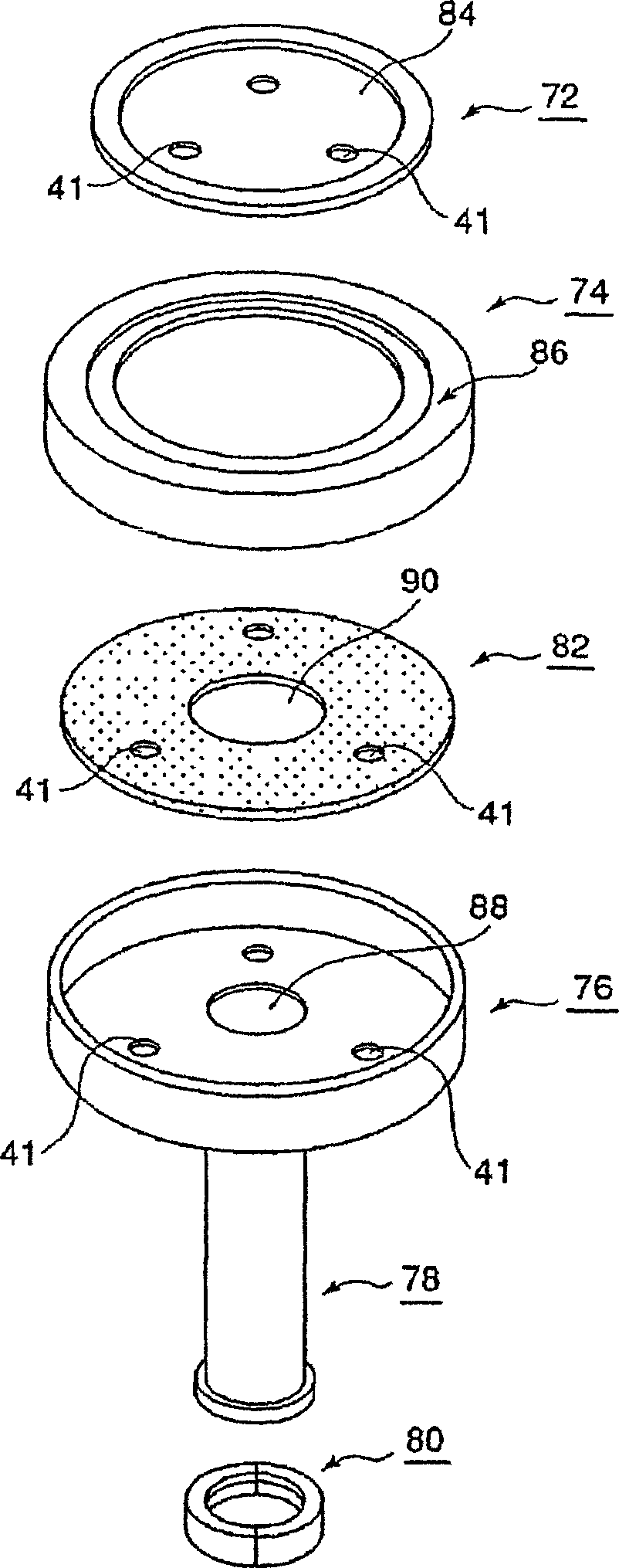

Loading table and heat treating apparatus having the loading table

InactiveCN1833312ASemiconductor/solid-state device manufacturingCharge manipulationHeat resistanceEngineering

A heat treating apparatus, wherein a treated body (W) is placed on the upper surface of a loading table (32) which is erected from the bottom part of a treatment container (4) through a column and in which a heating means (38) is buried and a specified heat treatment is applied to the treated body. Insulating cover members (72), (74), and (76) are installed on the upper surface, side surface, and lower surface of the loading table. Thus, since metallic atoms causing contamination can be prevented from being thermo-diffused from the loading table, various contaminations such as metallic contamination and organic substance contamination can be prevented from occurring.

Owner:TOKYO ELECTRON LTD

Polishing composition for silicon wafer and polishing method

ActiveUS20180066161A1Reducing LPDAvoid pollutionOther chemical processesSemiconductor/solid-state device manufacturingWater solubleCopper

To perform polishing while reducing an LPD and preventing contamination with metals, particularly nickel and copper, in final polishing of a silicon wafer. A polishing composition contains abrasives, a water-soluble polymer, a basic compound, a chelating agent, and water, in which, when the particle diameter equivalent to a particle diameter at a cumulative volume of 10% from a smaller particle diameter side is defined as D10, the particle diameter equivalent to a particle diameter at a cumulative volume of 50% from the smaller particle diameter side is defined as D50, and the particle diameter equivalent to a particle diameter at a cumulative volume of 90% from the smaller particle diameter side is defined as D90 in a particle size distribution of particles present in the polishing composition, a value of a coarse particle frequency parameter A defined by (Expression 1) illustrated below is less than 1.7, A=(D90−D50) / (D50−D10) and the polishing composition is used for final polishing in silicon wafer polishing.

Owner:FUJIMI INCORPORATED

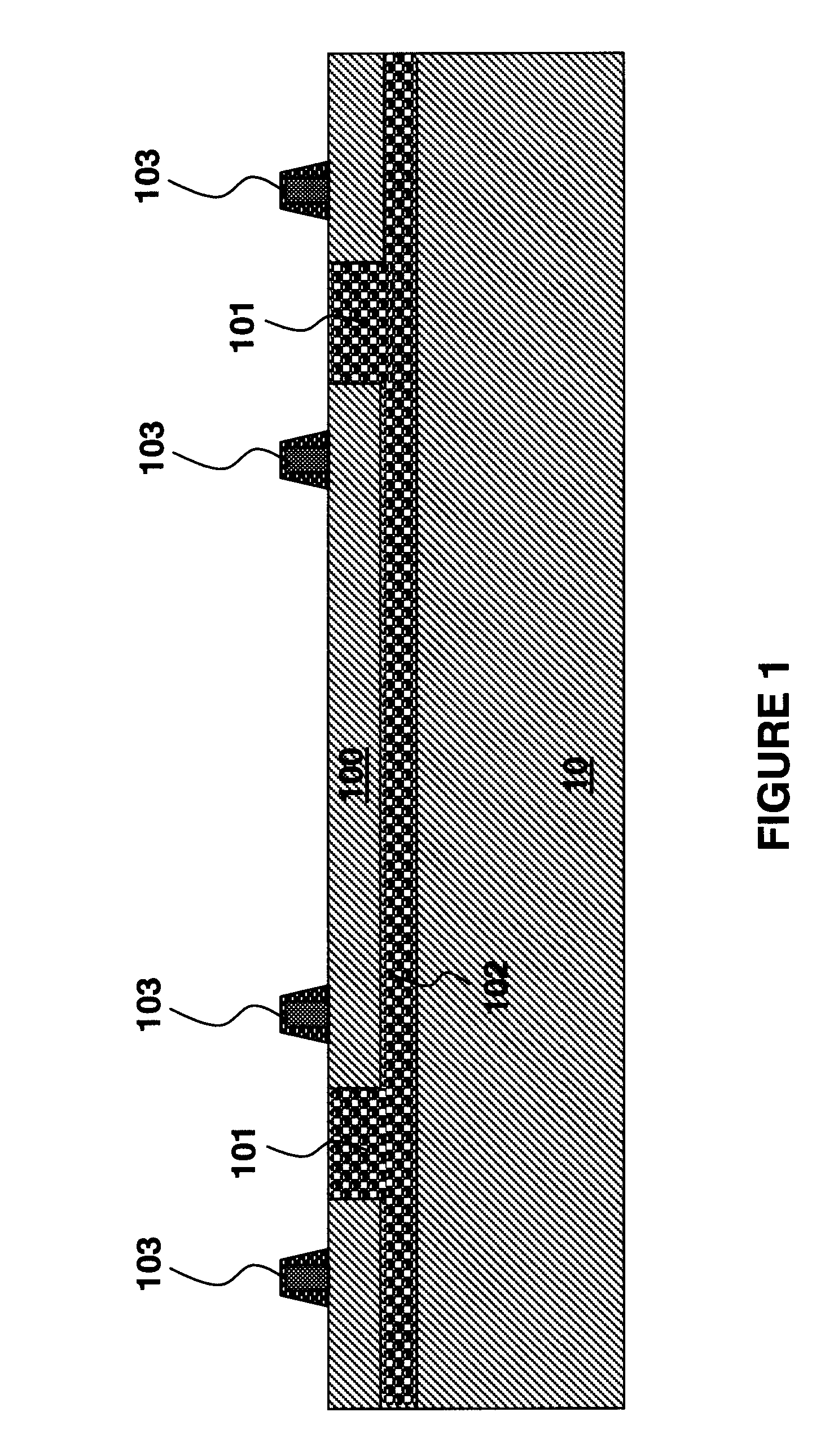

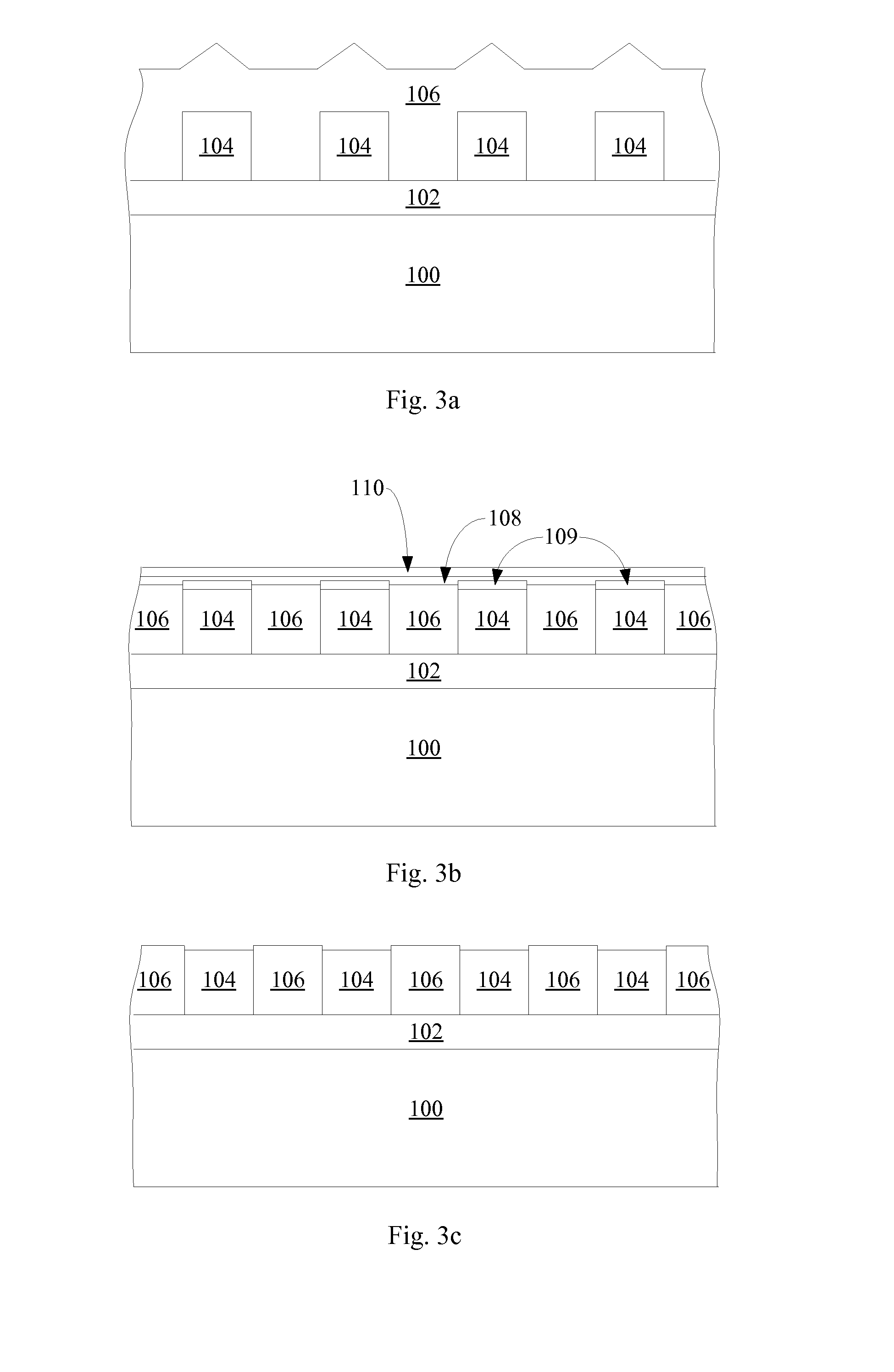

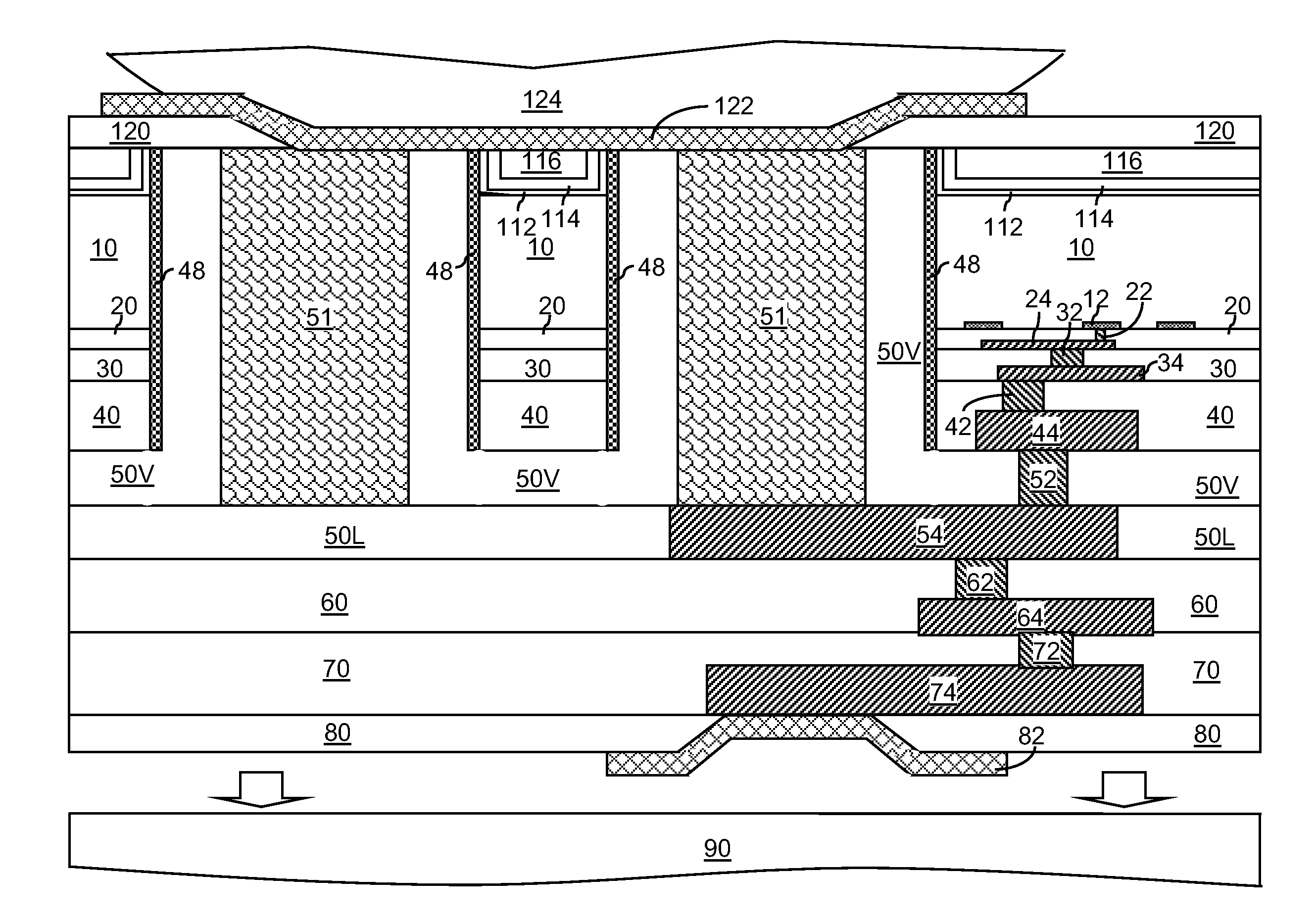

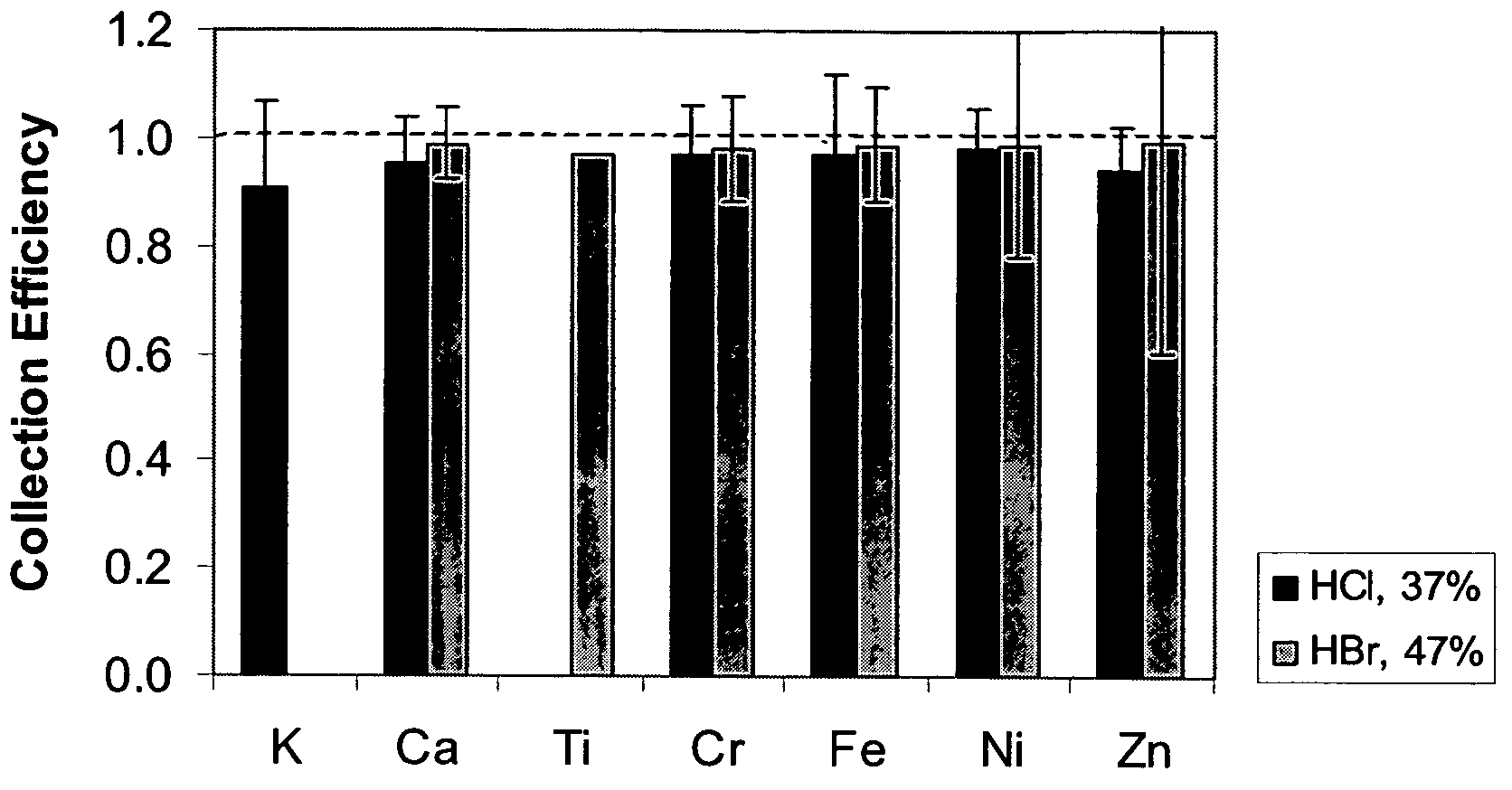

Metal-contamination-free through-substrate via structure

ActiveUS20130143400A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor materialsMetallic materials

A through-substrate via (TSV) structure that is immune to metal contamination due to a backside planarization process is provided. After forming a through-substrate via (TSV) trench, a diffusion barrier liner is conformally deposited on the sidewalls of the TSV trench. A dielectric liner is formed by depositing a dielectric material on vertical portions of the diffusion barrier liner. A metallic conductive via structure is formed by subsequently filling the TSV trench. Horizontal portions of the diffusion barrier liner are removed. The diffusion barrier liner protects the semiconductor material of the substrate during the backside planarization by blocking residual metallic material originating from the metallic conductive via structure from entering into the semiconductor material of the substrate, thereby protecting the semiconductor devices within the substrate from metallic contamination.

Owner:GLOBALFOUNDRIES U S INC

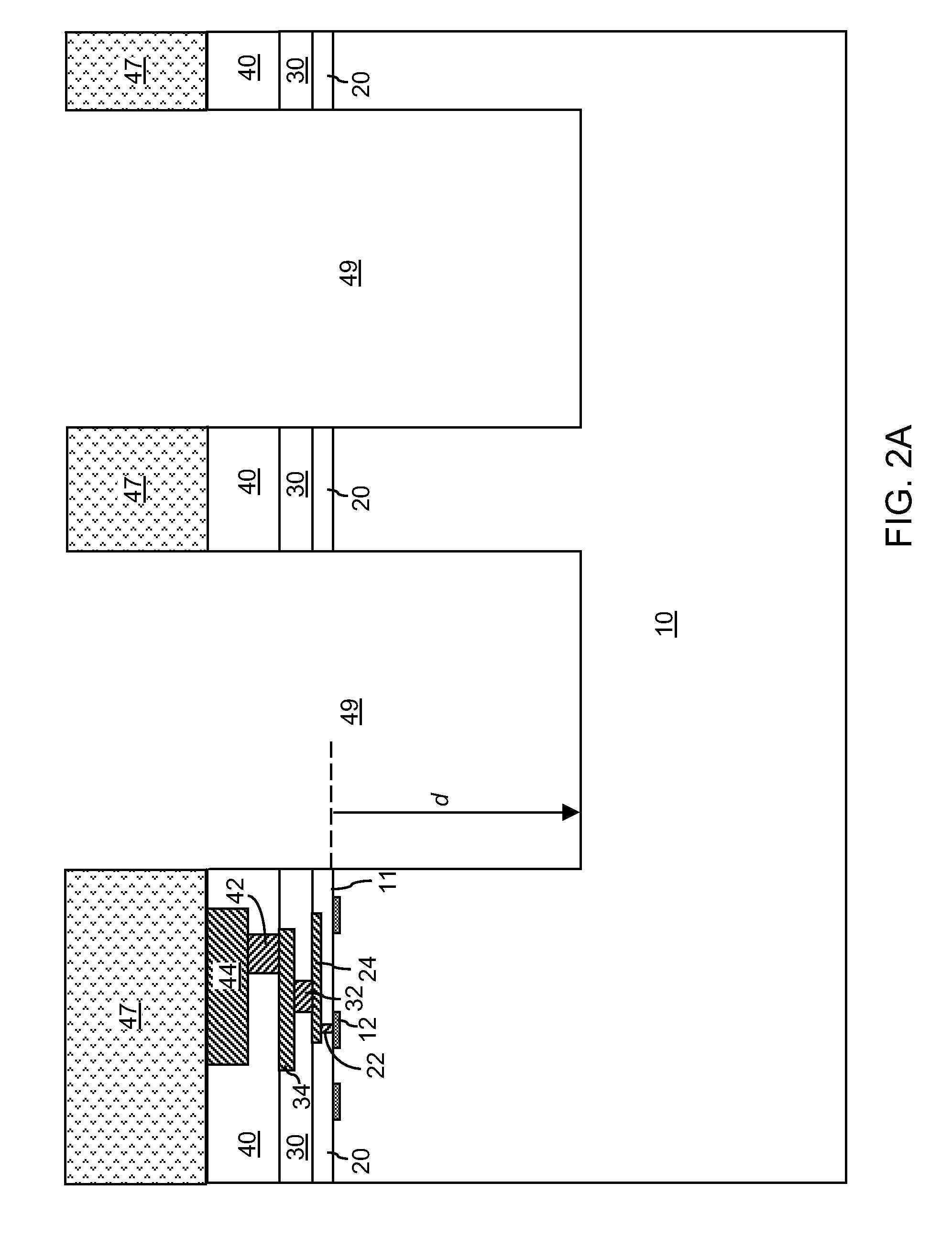

Solar cell boron diffusion method and boron diffusion device

ActiveCN106129177AAchieve even distributionImprove intra-chip uniformityFinal product manufacturePhotovoltaic energy generationMetal pollutionBoron diffusion

The invention discloses a solar cell boron diffusion method and a boron diffusion device, and belongs to the technical field of manufacturing of solar cells. The method comprises the following steps: putting a silicon wafer which needs to be subjected to boron diffusion into a diffusion furnace and carrying out warming; introducing a boron source, dichloroethylene, oxygen and nitrogen for boron diffusion; stopping introducing the boron source, the oxygen and the dichloroethylene and keeping the temperature at 900-960 DEG in a nitrogen atmosphere for 15-40min, wherein the nitrogen flow is 10-20L / min; and carrying out cooling, taking out the silicon wafer and finishing the diffusion process. The dichloroethylene is introduced in a high temperature diffusion process of a BBr3 liquid source, so that the on-chip uniformity and the inter-chip uniformity of the boron diffusion can be improved; corrosion of B2O3 to a quartz device in the furnace is retarded; the service lifetime of the quartz device is prolonged; and metal pollution of the silicon wafer in the high-temperature process is avoided.

Owner:BAODING TIANWEI YINGLI NEW ENERGY RESOURCES

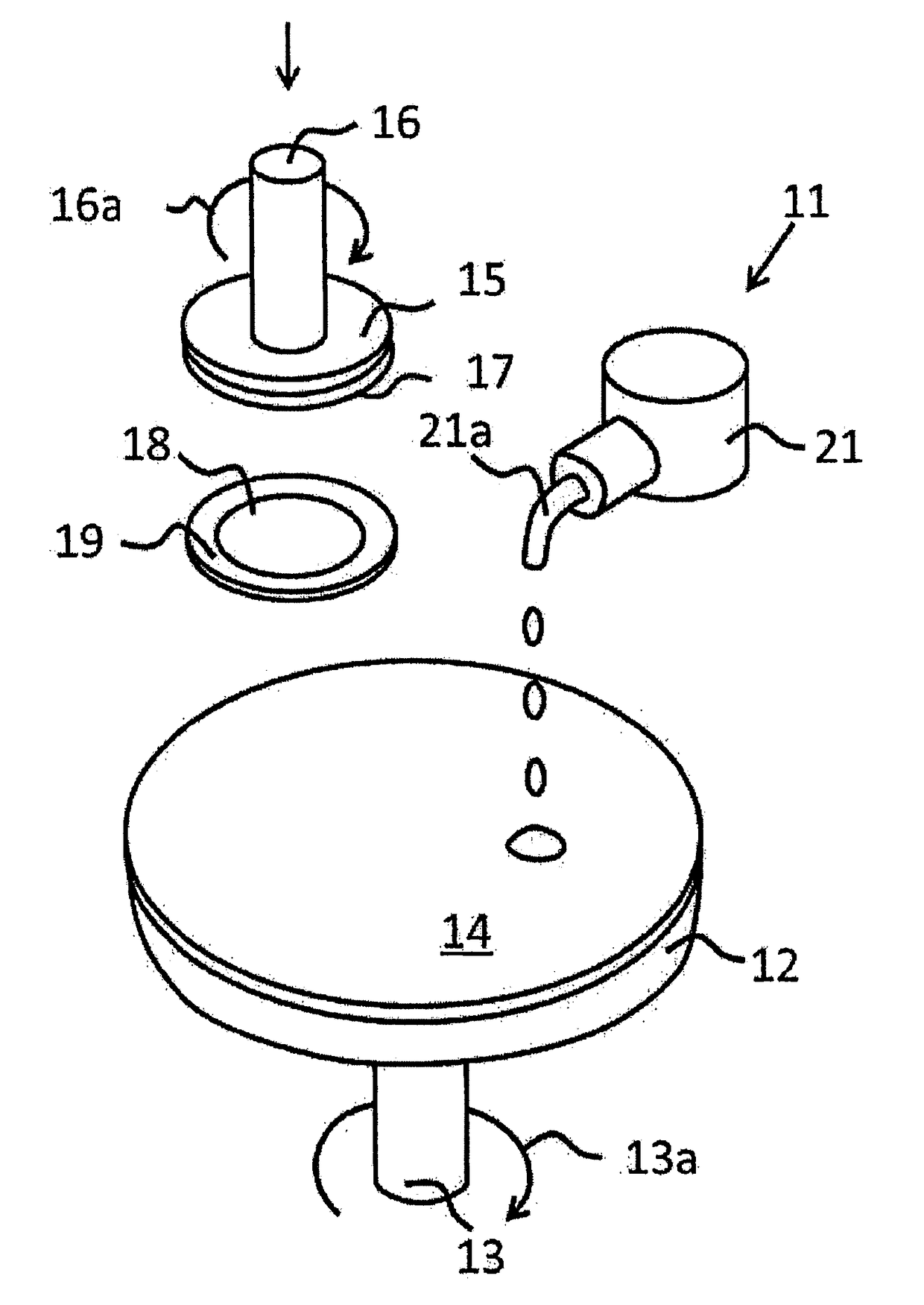

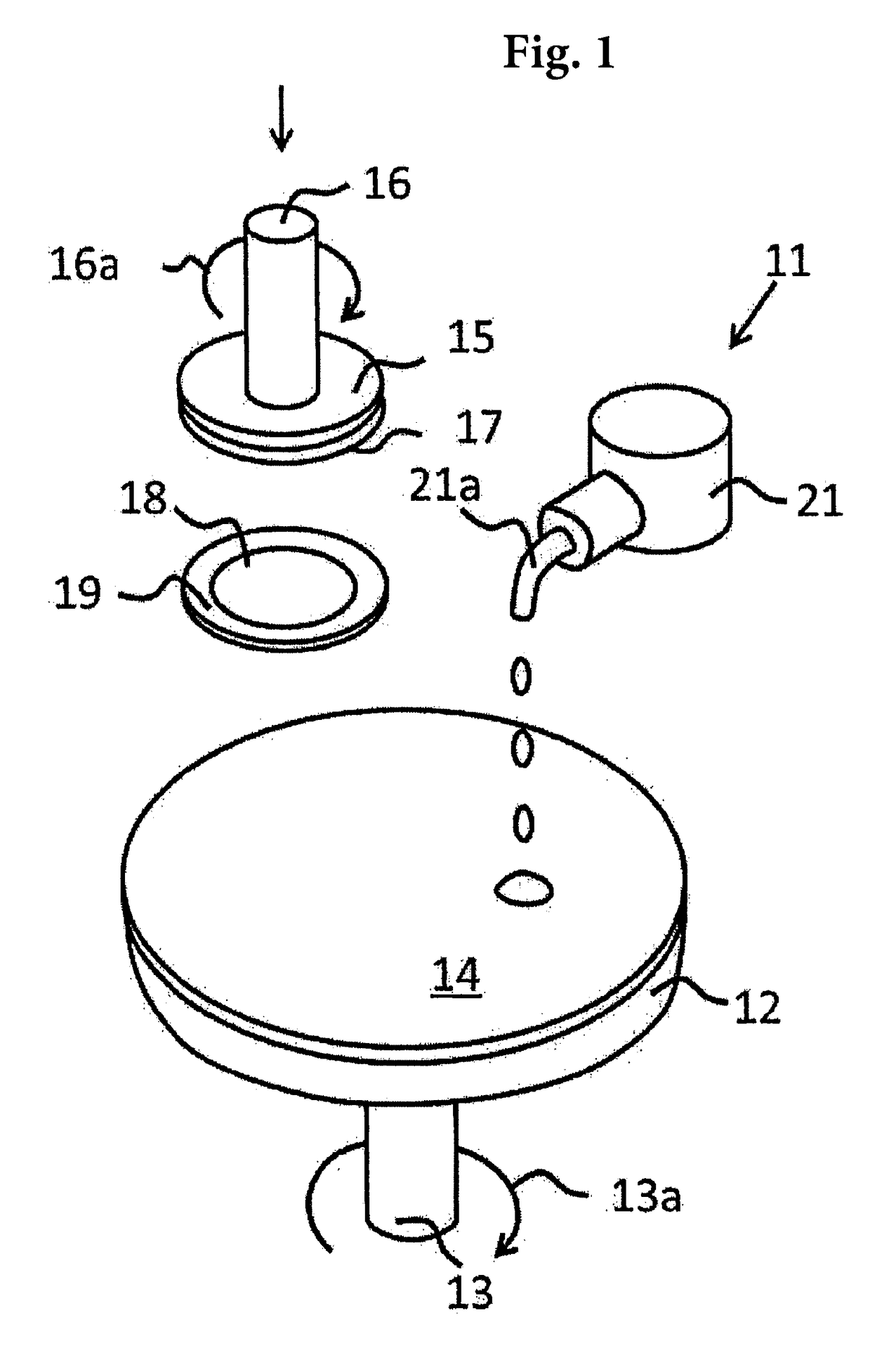

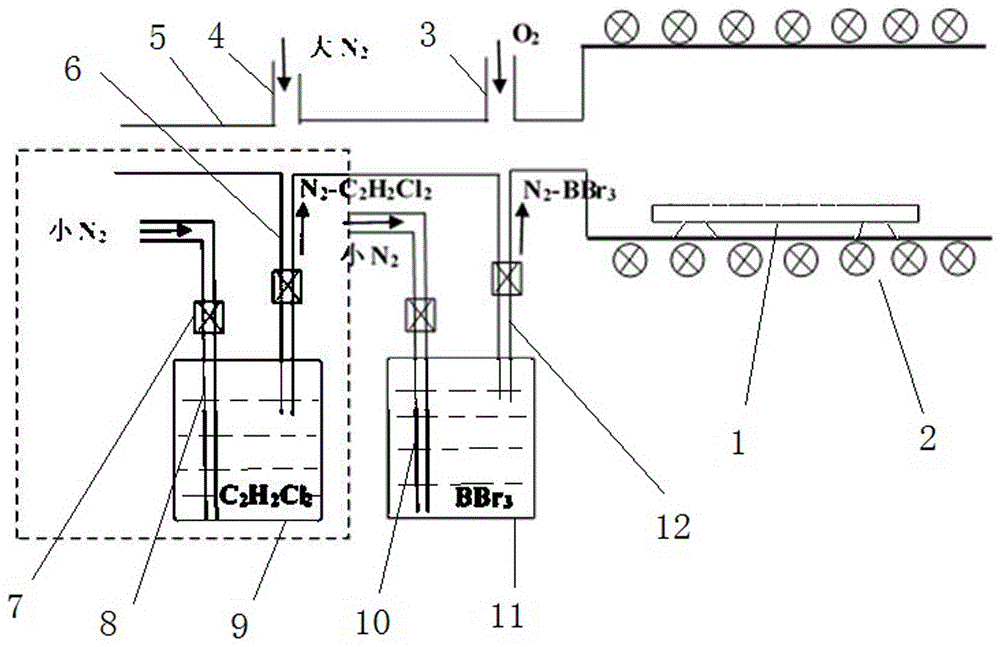

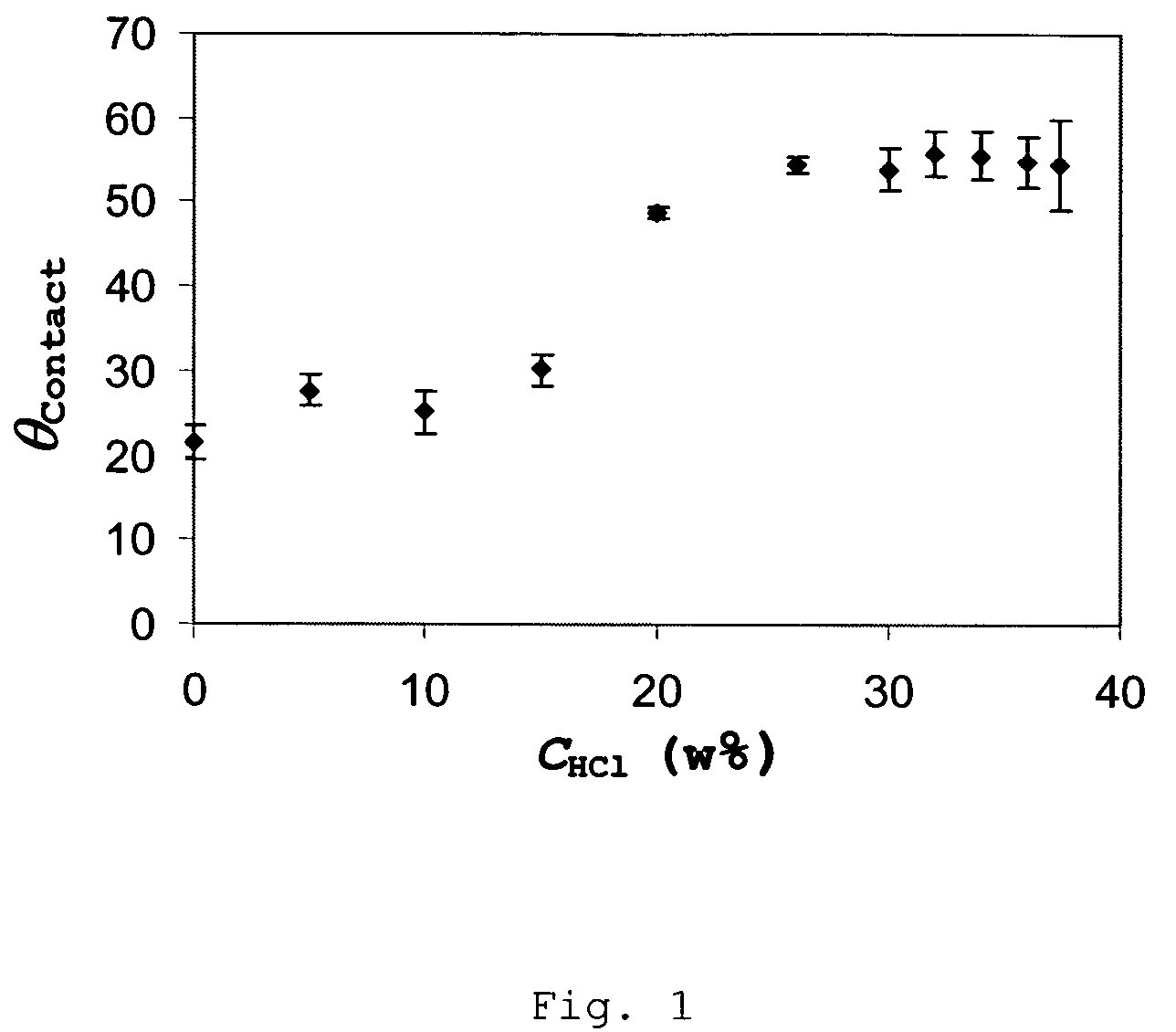

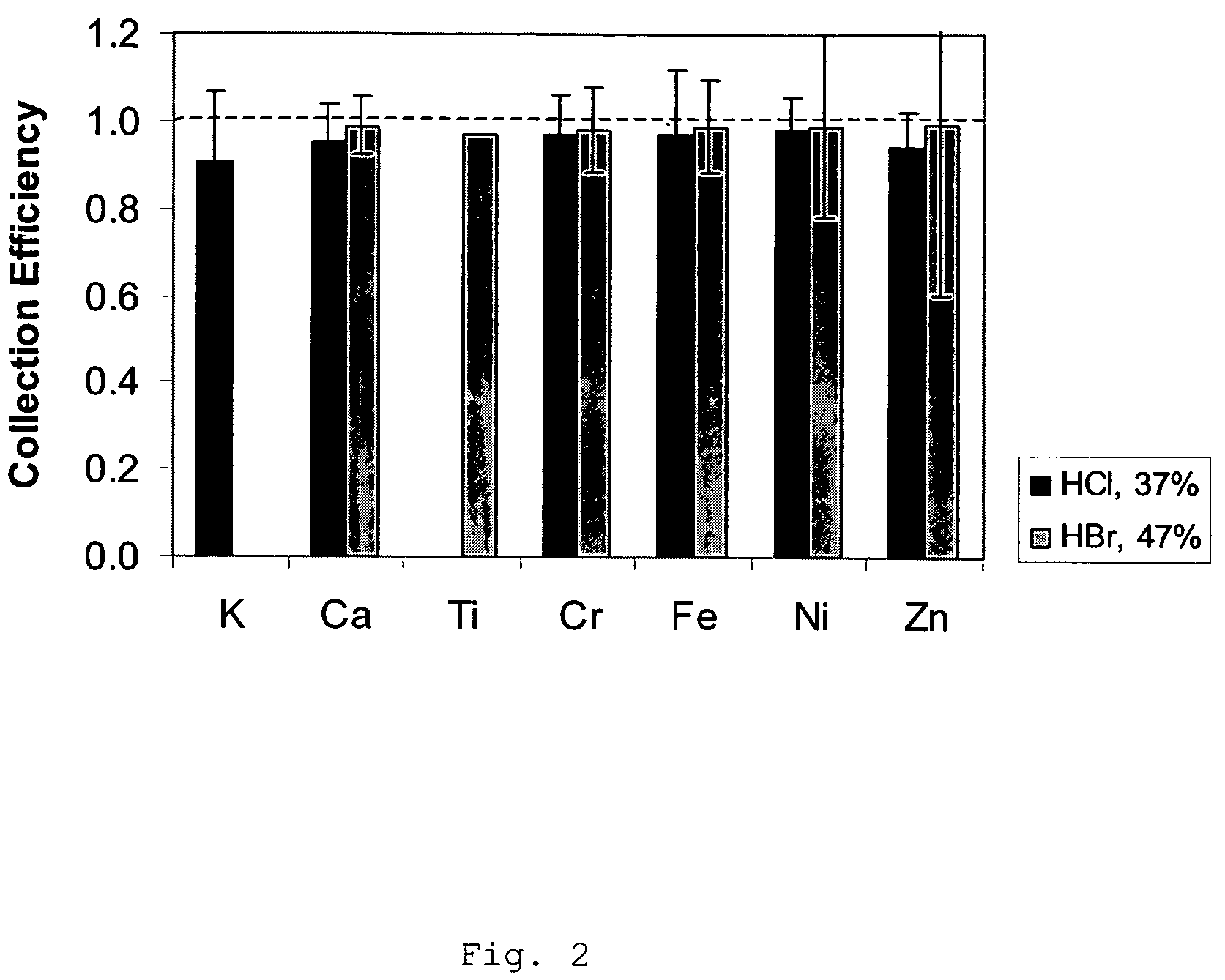

Impurity measuring method for Ge substrates

ActiveUS7399635B2Semiconductor/solid-state device testing/measurementWithdrawing sample devicesMetallic contaminationImpurity

The present invention provides an impurity measuring method comprising the steps of dropping a drop of a first solution on the surface of a substrate to be measured, moving the drop dropped on the surface of the substrate so that the drop is kept in contact with the surface and collects an impurity absorbed on the surface, recovering the drop after the movement and analyzing the recovered drop by chemical analysis to determine the type and concentration of the impurity, characterized in that the first solution is phobic to the substrate and the substrate consists substantially of Ge. The method is of particular importance for measuring metallic contamination on the surface of Ge substrates.

Owner:N V UMICORE

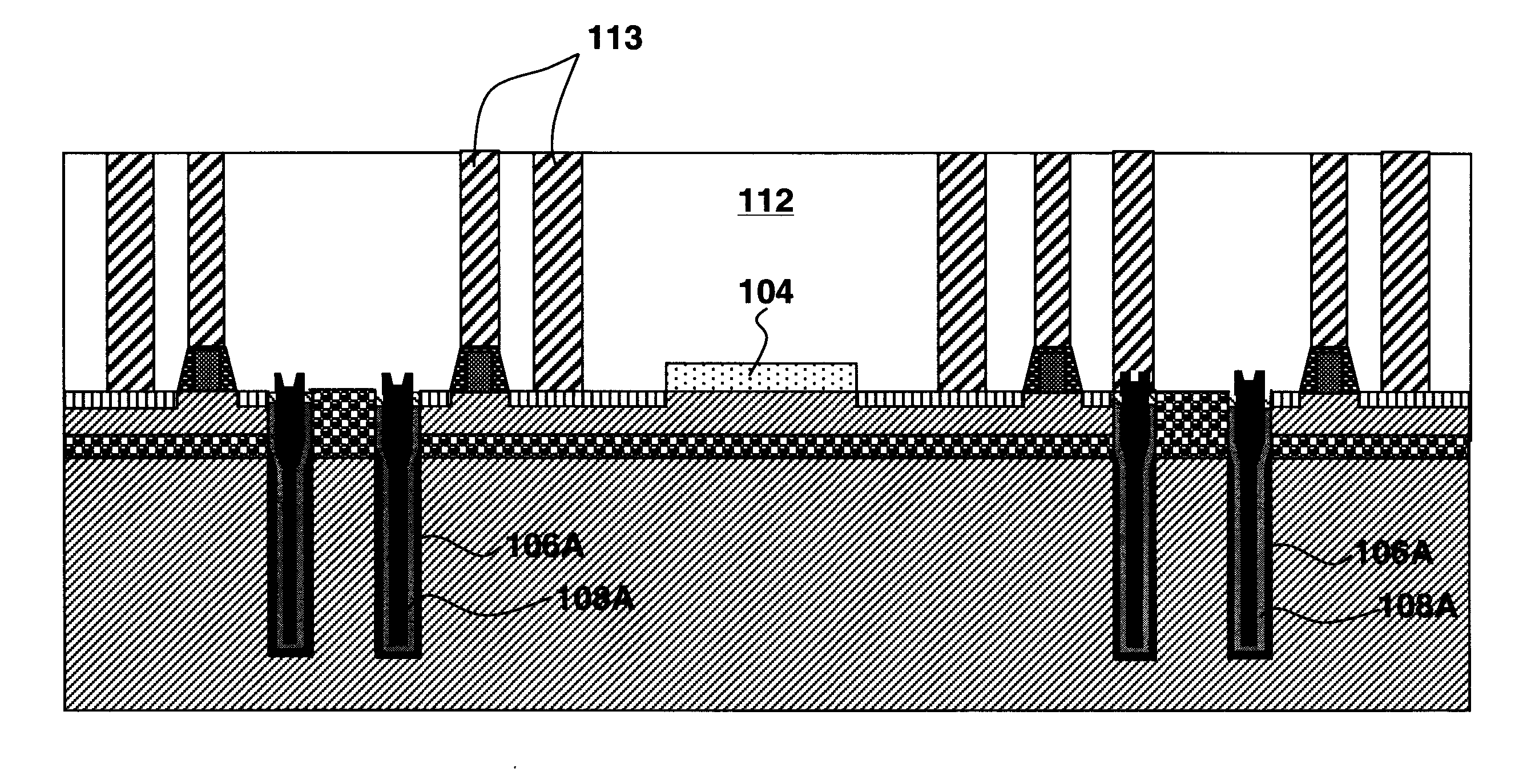

Semiconductor Device and Manufacturing Method Thereof

InactiveUS20070158784A1Avoiding characteristicReduce concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

In manufacturing a semiconductor device, the first gettering layer is formed on the backside of a wafer, and the second gettering layers are then formed on the backside and side surfaces of a chip, allowing these gettering layers to serve as trapping sites against metallic contamination that generated after backside grinding in assembly processes.

Owner:LONGITUDE SEMICON S A R L

Method for in-situ remediation of heavy metal hexavalent chromium-contaminated soil

InactiveCN104259198AImprove removal efficiencyLow costContaminated soil reclamationSoil heavy metalsElectronics

The invention discloses a method for the in-situ remediation of heavy metal hexavalent chromium-contaminated soil. According to the method, by using the advantages of a microbial fuel cell (MFC), an anode assembly and a cathode assembly (a diaphragm is arranged between the anode assembly and the cathode assembly) is embedded in the contaminated soil, the anode assembly locally utilizes organic matters in the soil as fuel, generated electronics reach the cathode assembly by virtue of anodes and leads, heavy metal hexavalent chromium adsorbed on the cathode assembly is reduced, and thus the degradation and the transformation of heavy metal hexavalent chromium contaminants in the soil are promoted, and the in-situ remediation of the heavy metal hexavalent chromium-contaminated soil is realized. By adopting an in-situ remediation process, the method has the advantages of high removal efficiency, low cost, good safety, no need of ventilation and energy consumption, capability of recycling and no secondary pollution because the anode assembly and the cathode assembly can be combined and optimized according to the actual conditions, has the great importance in remediating the heavy metal hexavalent chromium-contaminated soil, has a wide application prospect in fields of resources and environments such as the remediation of the heavy metal hexavalent chromium-contaminated soil, and the like.

Owner:东莞市环境科学研究所 +1

Process for metallic contamination reduction in silicon wafers

ActiveUS7084048B2Promote migrationSmall sizeSemiconductor/solid-state device manufacturingCopperOxygen

A process for removing a contaminant selected from among copper, nickel, and a combination thereof from a silicon wafer having a surface and an interior. The process comprises cooling the silicon wafer in a controlled atmosphere from a temperature at or above an oxidation initiation temperature and initiating a flow of an oxygen-containing atmosphere at said oxidation initiation temperature to create an oxidizing ambient around the silicon wafer surface to form an oxide layer on the silicon wafer surface and a strain layer at an interface between the oxide layer and the silicon wafer interior. The cooling of the wafer is also controlled to permit diffusion of atoms of the contaminant from the silicon wafer interior to the strain layer. Then the silicon wafer is then cleaned to remove the oxide layer and the strain layer, thereby removing said contaminant having diffused to the strain layer.

Owner:GLOBALWAFERS CO LTD

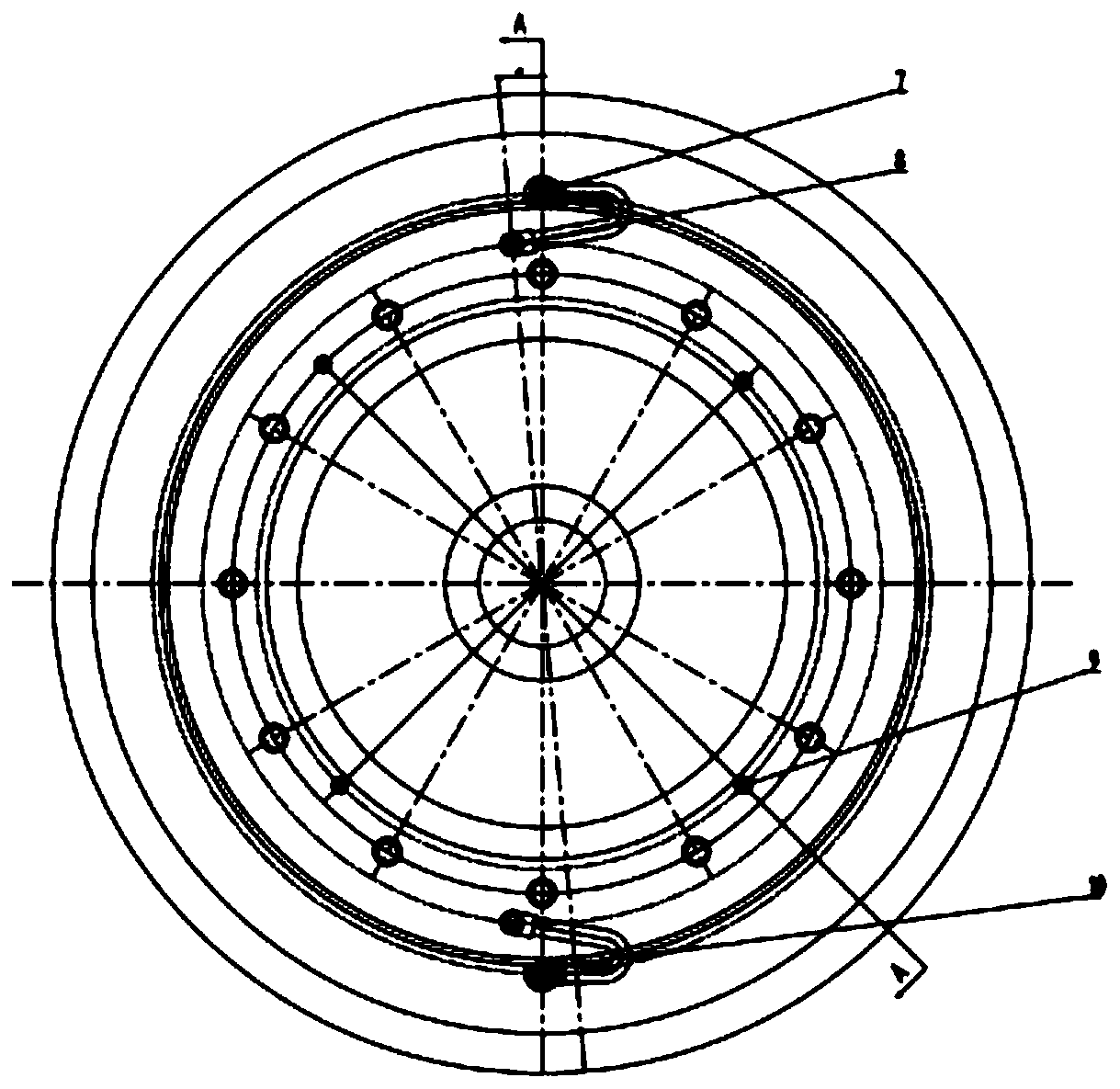

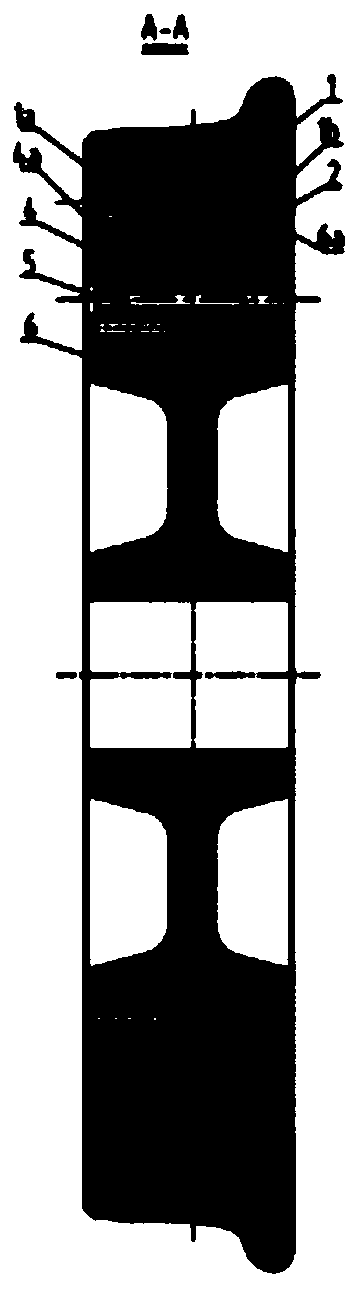

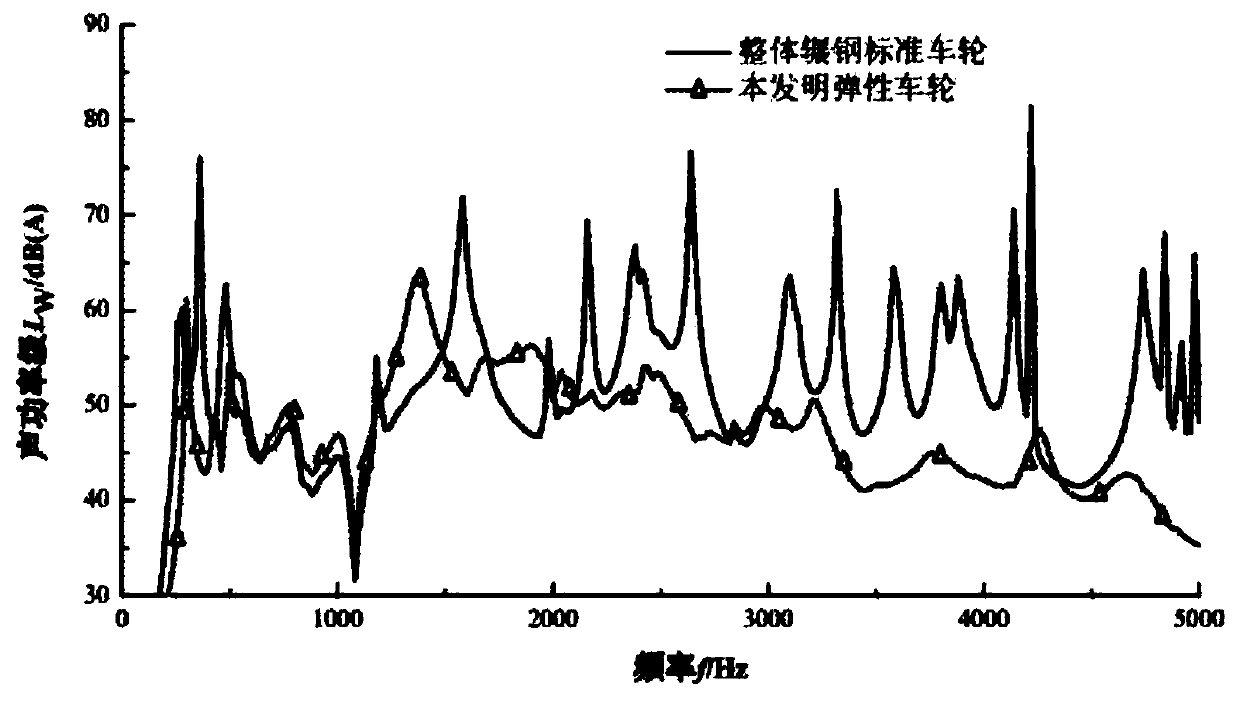

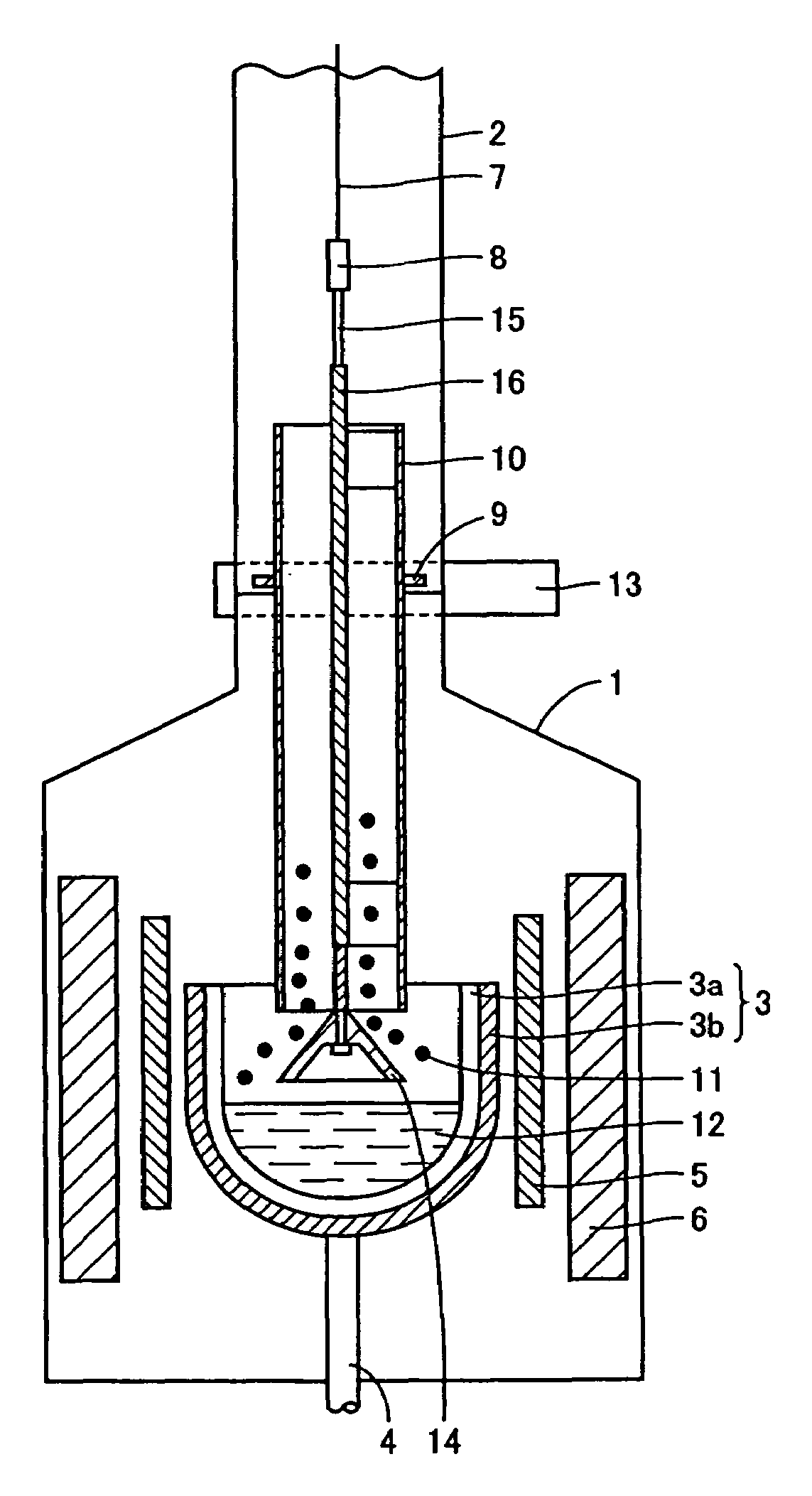

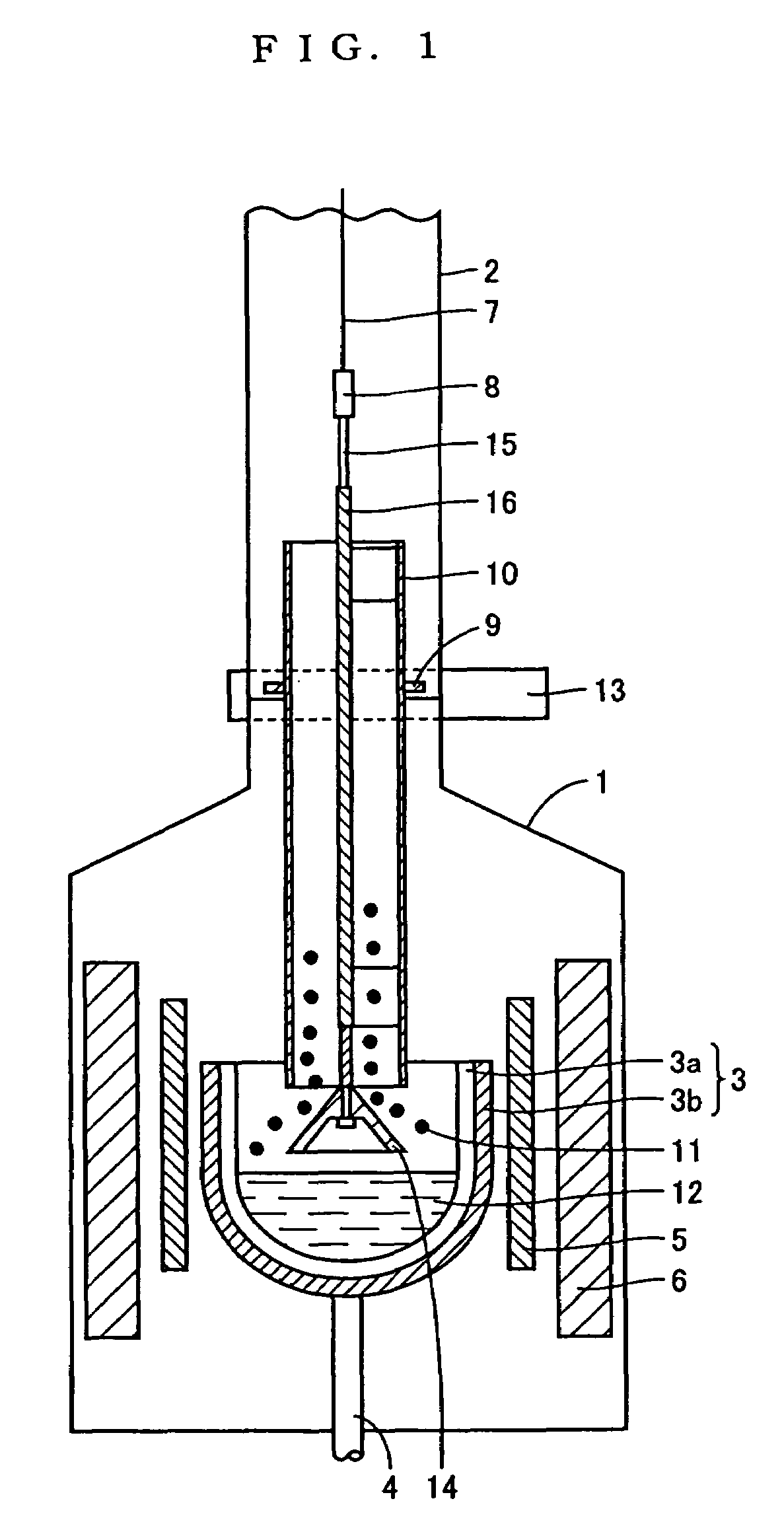

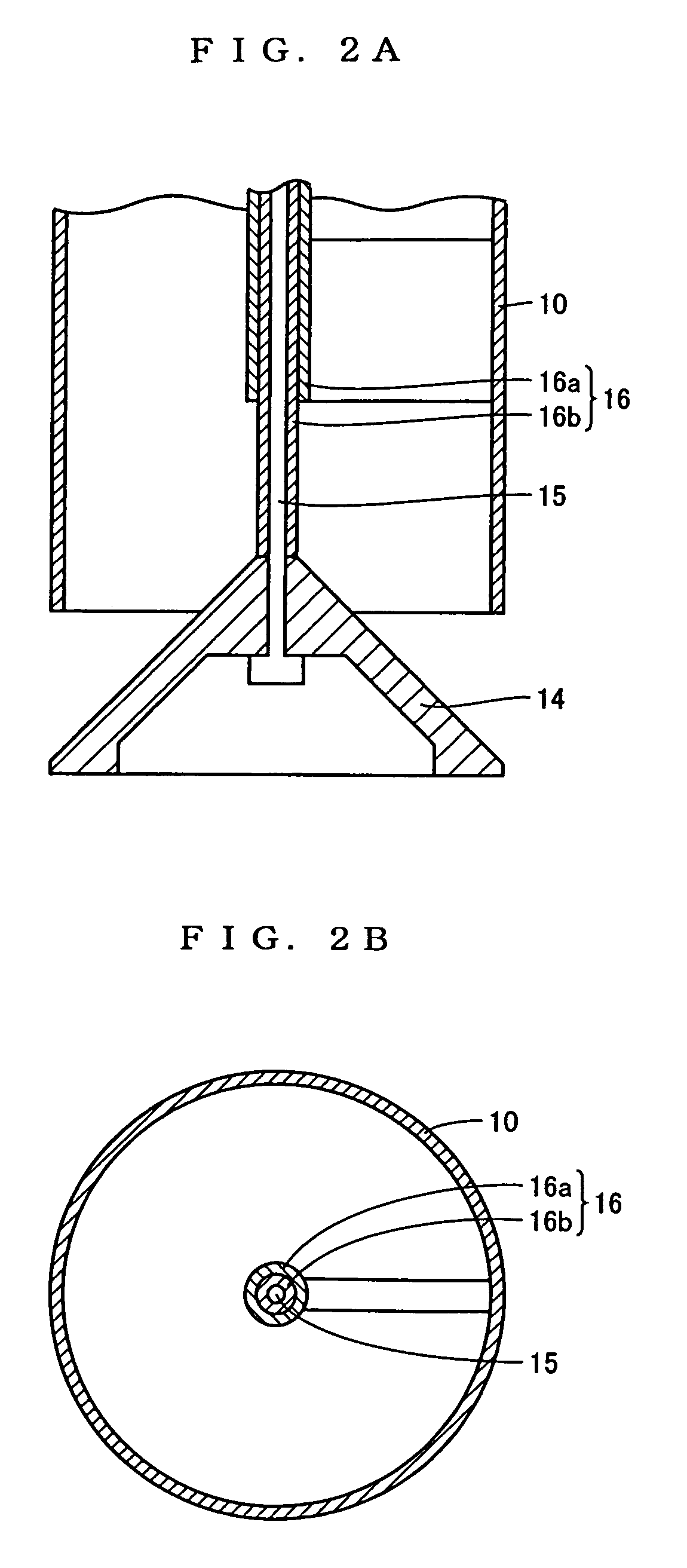

Shear-press composite type elastic wheel for low-floor tramcar and production process thereof

InactiveCN110539585AHigh tensile strengthImproves strength uniformityRail-engaging wheelsFurnace typesRare-earth elementNoise reduction

The invention provides a shear-press composite type elastic wheel for a low-floor tramcar and a production process thereof. The shear-press composite type elastic wheel for the low-floor tramcar comprises a wheel band, a press ring and a wheel core; the wheel band, the press ring and the wheel core are all made of high-purity iron alloy; the mass percentage of each component of the high-purity iron alloy is as follows: 0.015-0.5% of Si, 0.6-0.9% of Mn, 0.65-0.7% of C, 1.8-2.1% of Mg, 3.45-4.21% of Al, 0.005-0.04% of S, less than or equal to 0.3% of Cr, less than or equal to 0.30% of Cu, less than or equal to 0.25% of Ni, less than or equal to 0.04% of P, less than or equal to 0.08% of Mo, less than or equal to 0.05% of V, less than or equal to 0.02% of Sc, less than or equal to 0.03% of Tiand the balance of Fe. According to the shear-press composite type elastic wheel for the low-floor tramcar, by using a mode of adding a rare earth element and refining the rare earth element in steps, the tensile strength of the wheel band, the press ring and the wheel core is enhanced, the center of a material is close without a gap, and moreover, no metallic contamination is caused, and the strength uniformity of the surface is high; a rubber layer is embedded between the wheel band and the wheel core and has a vibration absorbing effect; the rubber layer possesses good radial stiffness andaxial stiffness; and meanwhile, the freedom of a wheel rim is limited; the problem that a tuned mass damper is additionally mounted on the external side of the wheel to suppress medium and low noisesis solved; the structure is simple; and the vibration absorbing and noise reduction effect is good.

Owner:ANHUI UNIVERSITY OF TECHNOLOGY