Display device and method of manufacturing the same

a technology of display panel and manufacturing method, which is applied in the field of display panel, can solve the problems of not meeting the need for the above-mentioned technical trend, difficult to form ultra-high-definition display panel, and difficult to build peripheral circuit in the frame region, so as to reduce the occupied area of semiconductor circuit made of tfts, reduce the alignment margin, and eliminate the margin required to add impurities.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

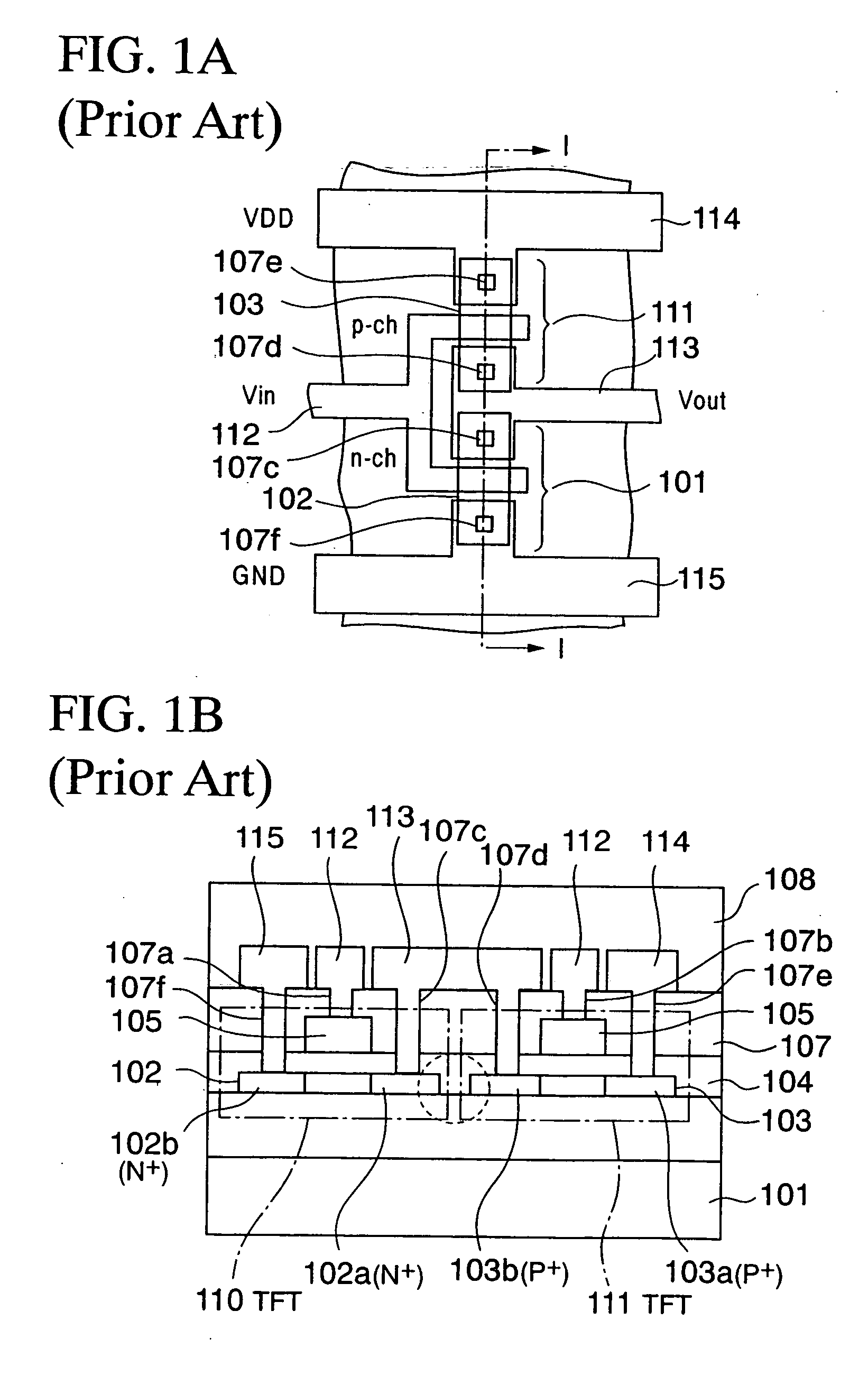

[0057] In the first embodiment, a CMOS inverter and a CMOS analog switch both having a configuration, in which one n-type impurity diffusion region constituting an n-channel TFT and one p-type impurity diffusion region constituting a p-channel TFT are not separated but formed continuously and adjacently on one silicon island, will be explained hereunder.

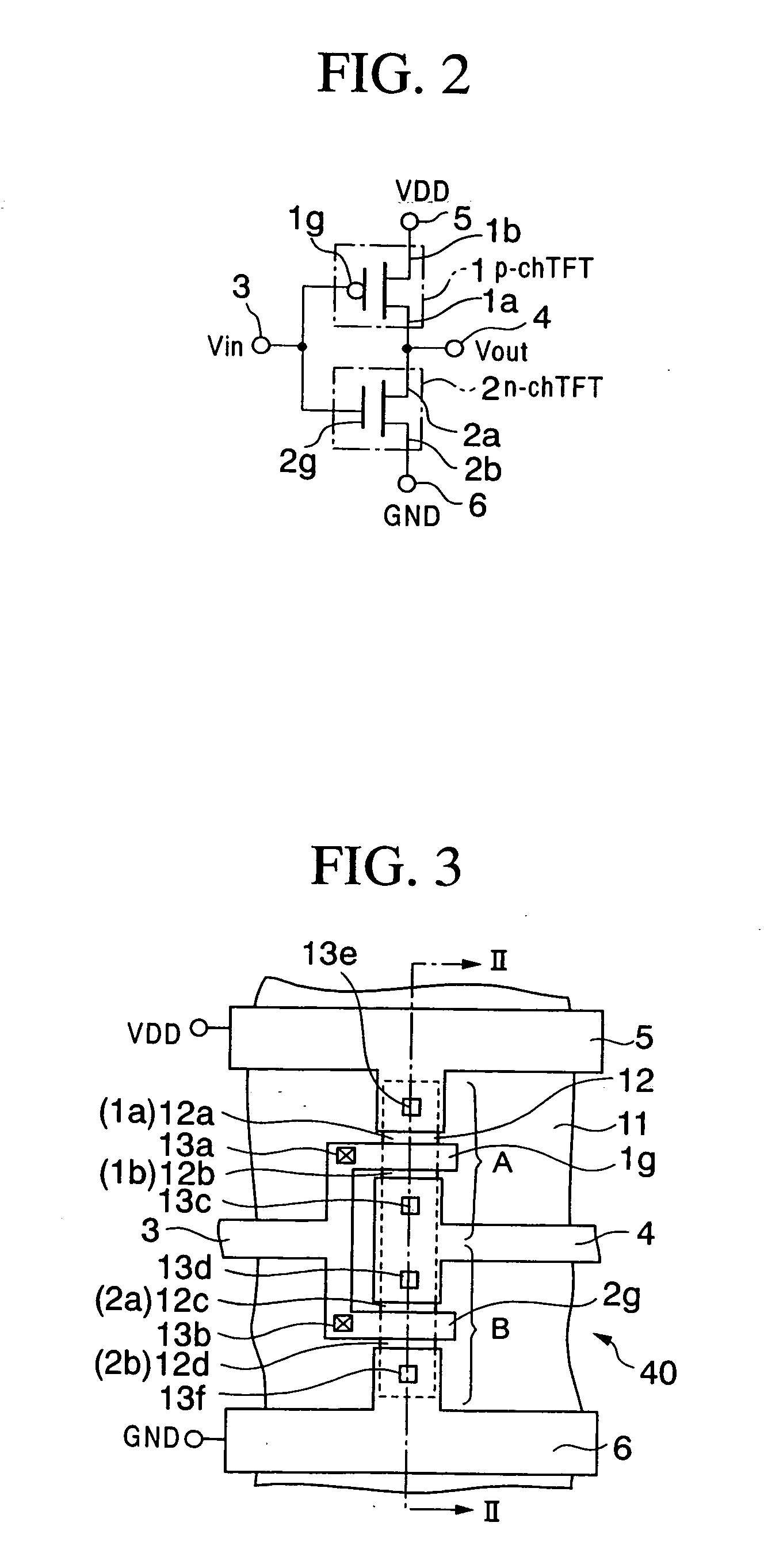

(i) CMOS Inverter

[0058]FIG. 2 is an equivalent circuit diagram showing a CMOS inverter. In FIG. 2, gate electrodes 1g, 2g of a p-channel thin film transistor (p-ch TFT) 1 and an n-channel thin film transistor (n-ch TFT) 2 are connected to the same input wiring 3 respectively. Also, a second source / drain 1b of the p-ch TFT 1 and a first source / drain 2a of the n-ch TFT 2 are connected to the same output wiring 4. In addition, a first source / drain 1a of the p-ch TFT 1 is connected to a power supply wiring 5, and a second source / drain 2b of the n-ch TFT 2 is connected to a ground wiring 6.

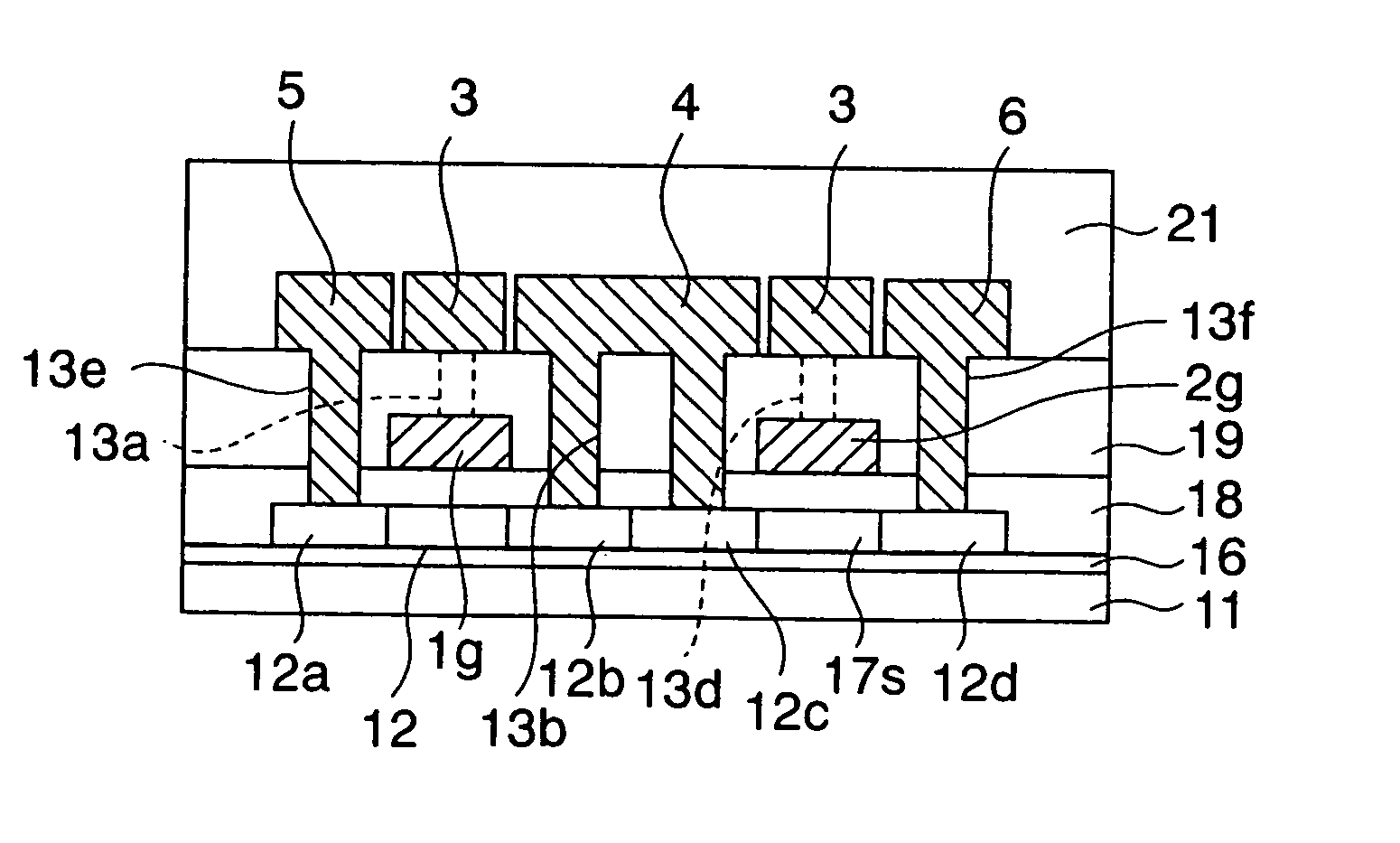

[0059]FIG. 3 is a plan view showing a layout ...

second embodiment

[0102] In a second embodiment, a CMOS TFT having such a configuration that mutually neighboring source / drain regions of the p-channel thin film transistor and the n-channel thin film transistor are formed continuously not to leave a space between them and neighboring n-type source / drain and p-type source / drain are connected to the same wiring via one contact hole will be explained hereunder.

[0103]FIG. 7 is a plan view showing a layout of a CMOS inverter according to a second embodiment of the present invention, and FIG. 8 is a sectional view taken along a IV-IV line in FIG. 7. In FIG. 7 and FIG. 8, the same references as those in FIG. 3 and FIG. 6J denote the same elements.

[0104] A CMOS inverter 41 in FIG. 7 employs the p-ch TFT 1 and the n-ch TFT 2 disclosed in the first embodiment, and has such a configuration that a contact hole 13h is formed at the boundary portion between a second p+-type impurity region 12b serving as one source / drain of the p-ch TFT 1 and a first n+-type im...

third embodiment

[0111] In a third embodiment, a CMOS analog switch having such a configuration that mutually neighboring source / drain regions of the p-channel thin film transistor and the n-channel thin film transistor are formed continuously not to leave a space between them and contact portions of the n-type source / drain and contact portions of the p-type source / drain are aligned on a straight line by arranging zigzag the boundary portions (joint portions) between neighboring n-type source / drain and p-type source / drain will be explained hereunder.

[0112]FIG. 11 is a plan view showing a layout of a CMOS analog switch according to the third embodiment of the present invention, FIG. 12A is a sectional view taken along a VI-VI line in FIG. 11, and FIG. 12B is a sectional view taken along a VII-VII line in FIG. 11. In FIG. 11 and FIG. 12, the same references as those in FIG. 5 and FIG. 6J denote the same elements.

[0113] In order to flow the large current, the polysilicon film 14 of the p-ch TFT 1 and...

PUM

| Property | Measurement | Unit |

|---|---|---|

| size | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More