Method of designing semiconductor integrated circuit device and semiconductor integrated circuit device

a technology of integrated circuits and semiconductors, applied in the direction of solid-state devices, semiconductor/solid-state device details, instruments, etc., can solve the problems of increased design effort, increased design inconvenience, and increased design cost, so as to reduce design and labor burden, chip size, power consumption and operating speed are optimized, and the effect of reducing the burden on design and labor

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0055] Preferred embodiments of the present invention will hereinafter be described with reference to the accompanying drawings.

[0056] A description will first be made of how to view common cell topology, using a CMOS (Complementary MOS) inverter cell INV as an illustrative example.

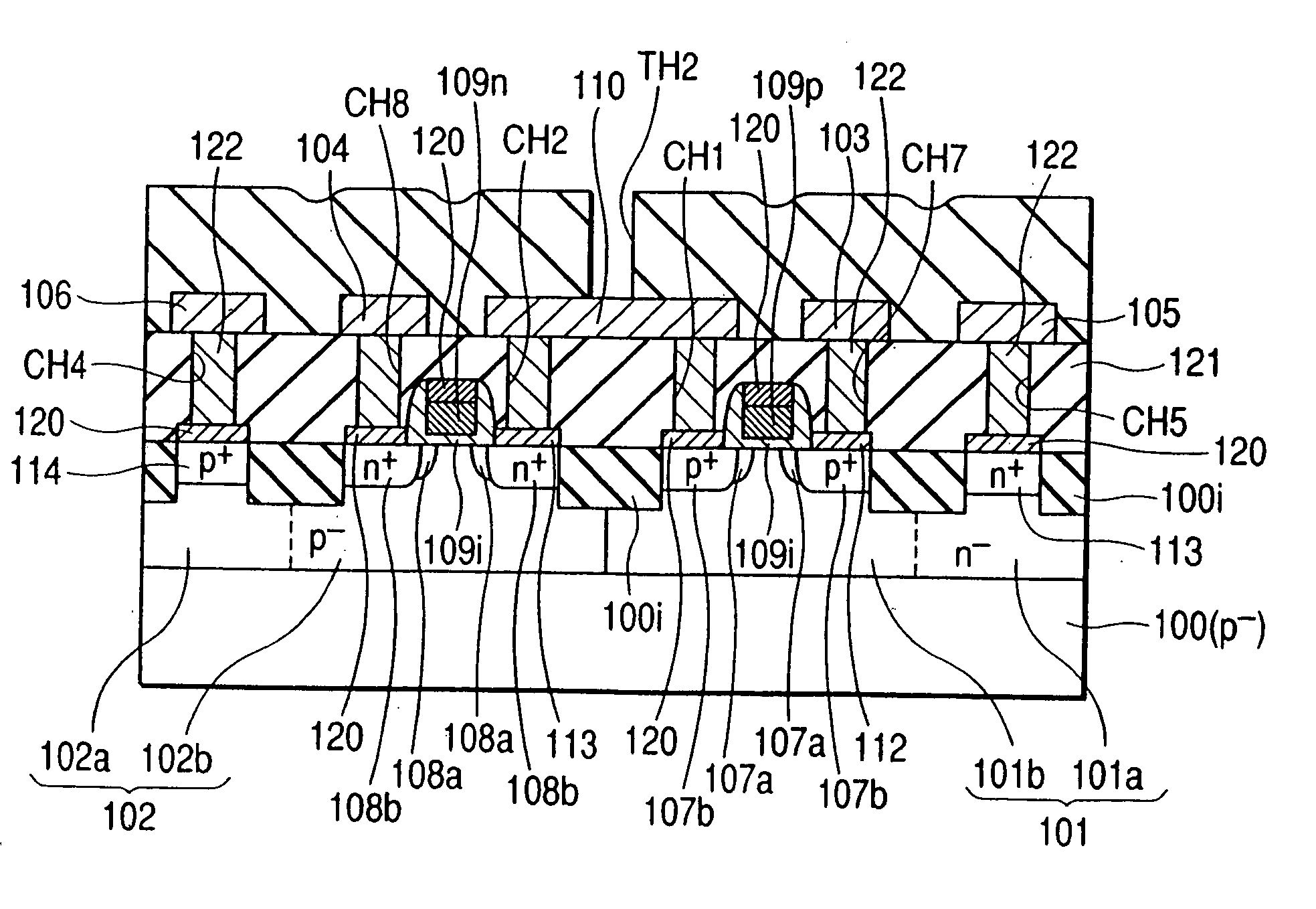

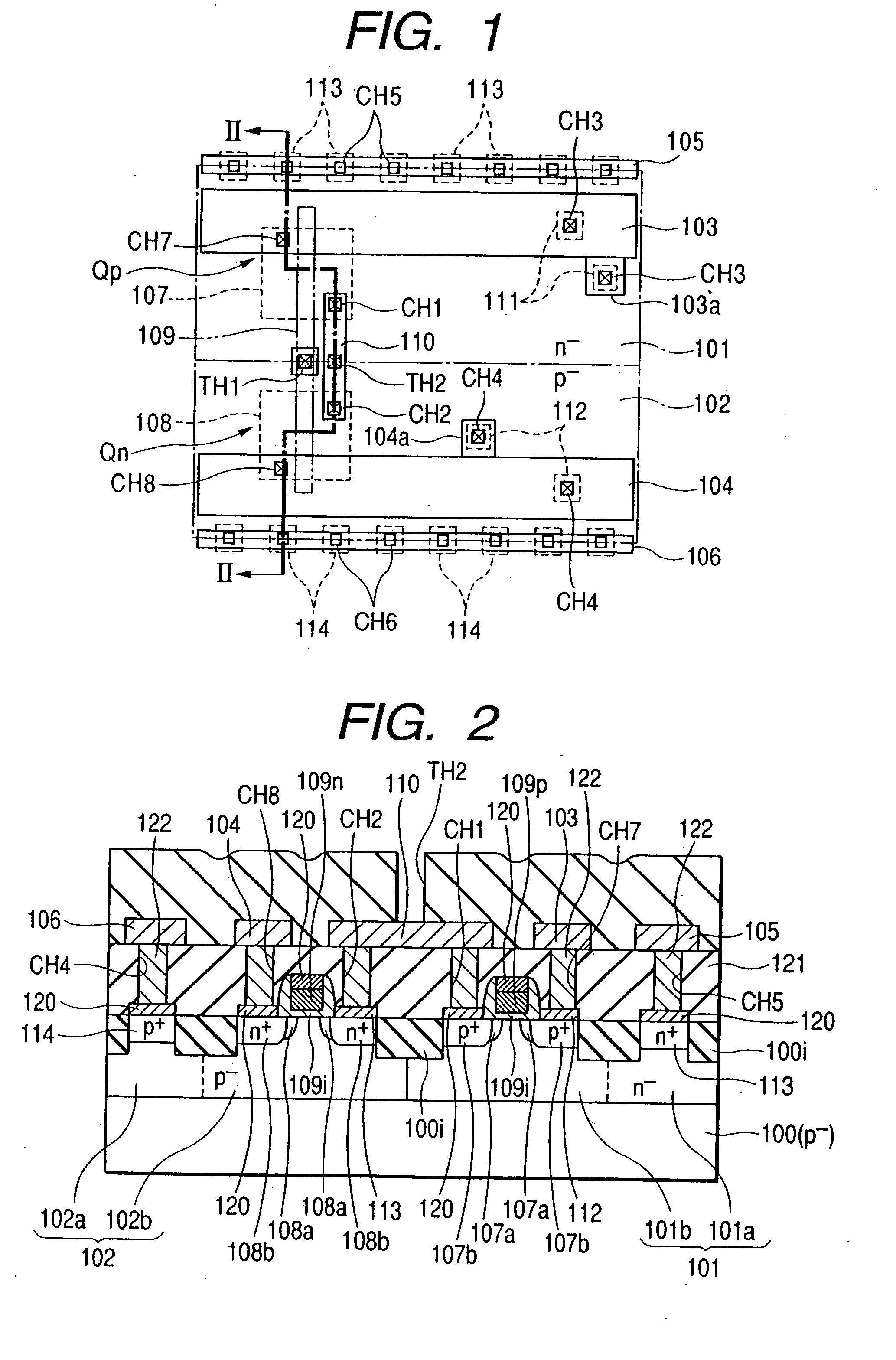

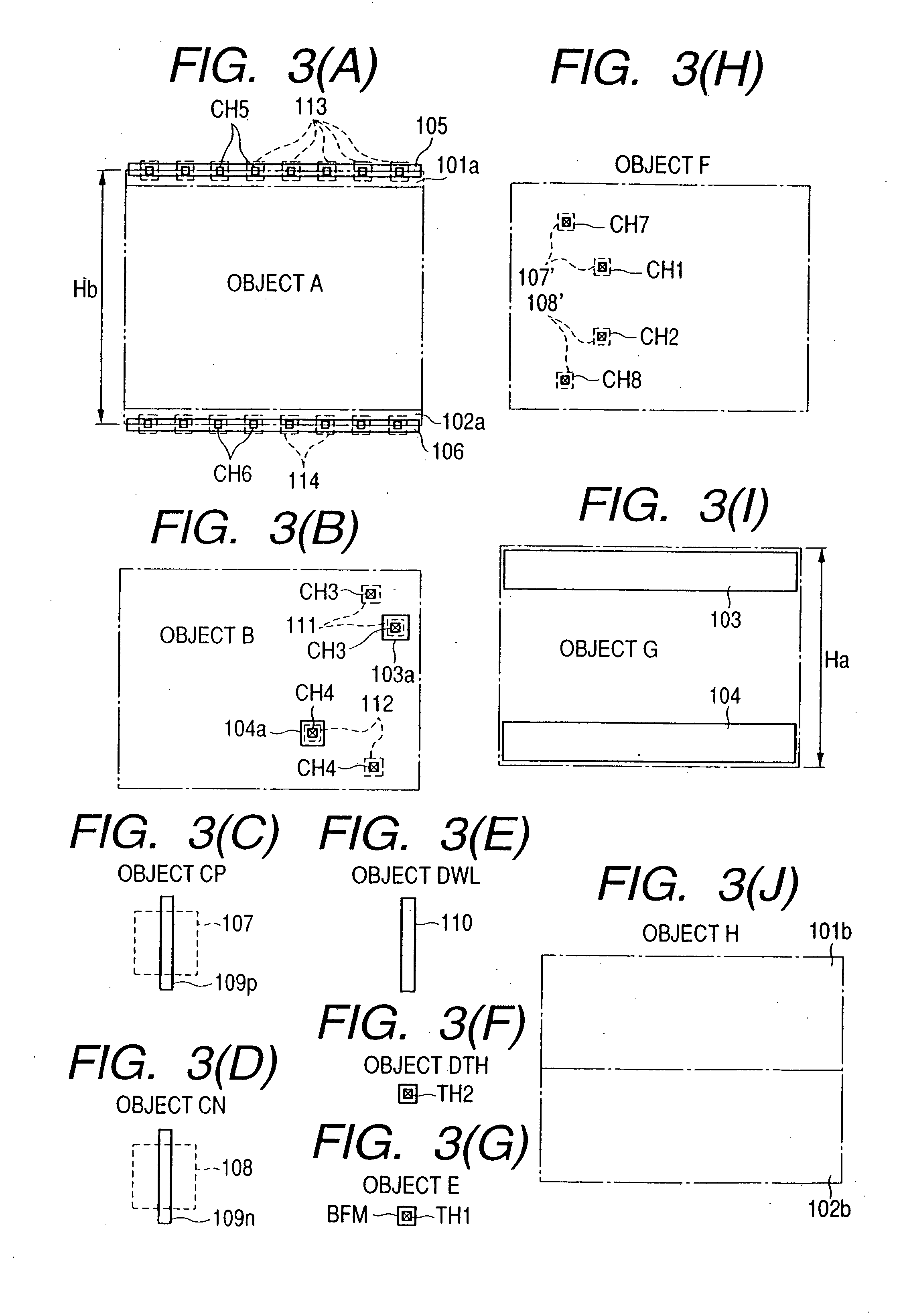

[0057]FIGS. 1 and 2 respectively show one example of a common cell topology for a CMOS inverter cell INV comprised of a pair of elements including a p channel MISFET (Metal Insulator Semiconductor FET) Qp and an n channel MISFET Qn. Of these, FIG. 1 illustrates an example of a layout pattern of a circuit cell and FIG. 2 shows an example of a sectional view taken along line 11 - II of FIG. 1.

[0058] In FIGS. 1 and 2, reference numeral 100 indicates a p-type single-crystal silicon substrate used as a base, for example. Reference numeral 100i indicates a device or element separator, and reference numerals 101 and 102 indicate an n well region (101a, 101b) and a p well region (102a, 102b) defined as relativ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More