High speed turbo codes decoder for 3g using pipelined siso log-map decoders architecture

a pipelined siso logmap and codes decoder technology, applied in the direction of coding, code conversion, fault response, etc., can solve the problems of long wait for decisions until the whole sequence, computational complexity of map algorithm, and implementation in semiconductor asic devices, so as to improve speed data throughput, reduce power consumption, and reduce costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Turbo Codes Decoder

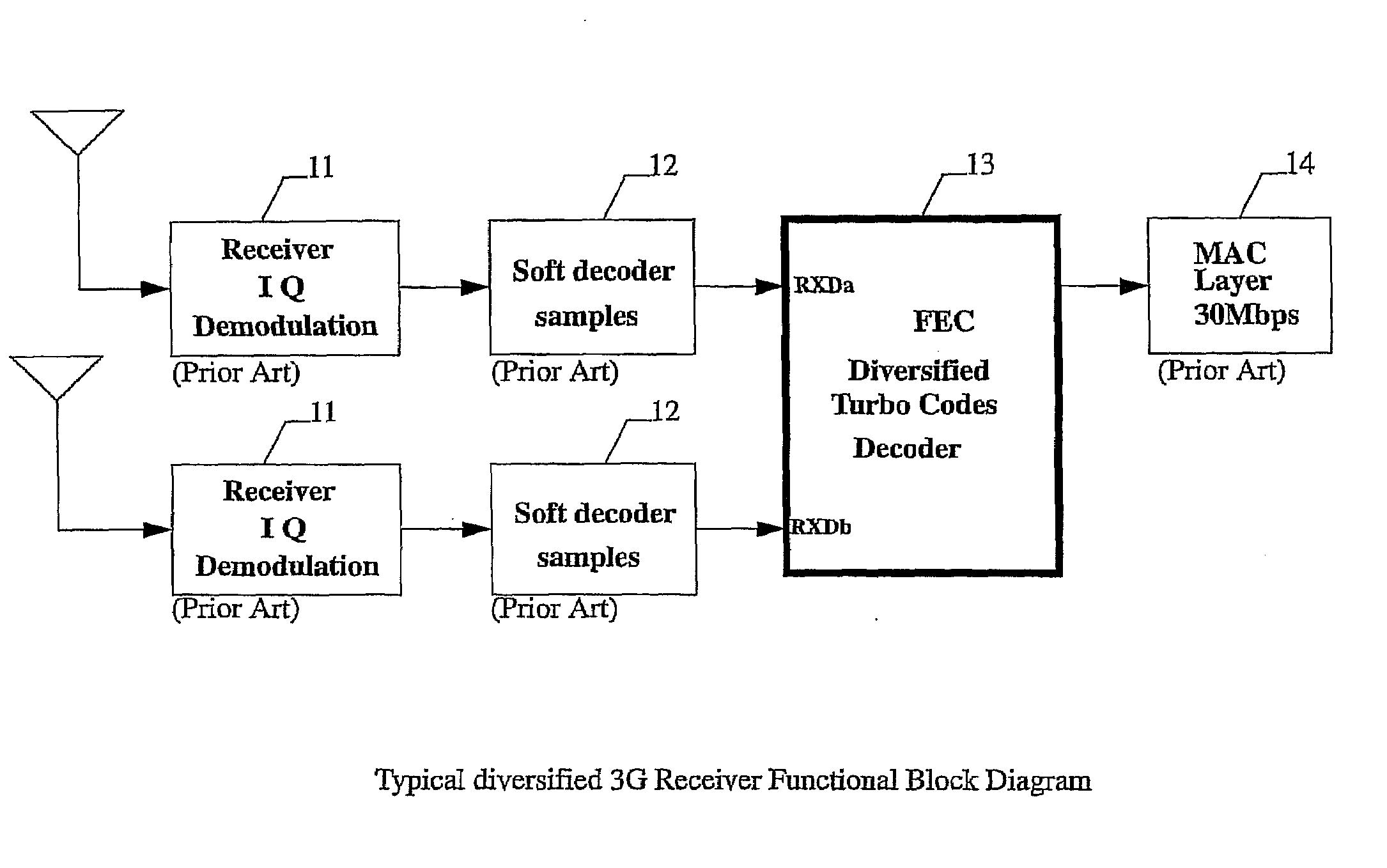

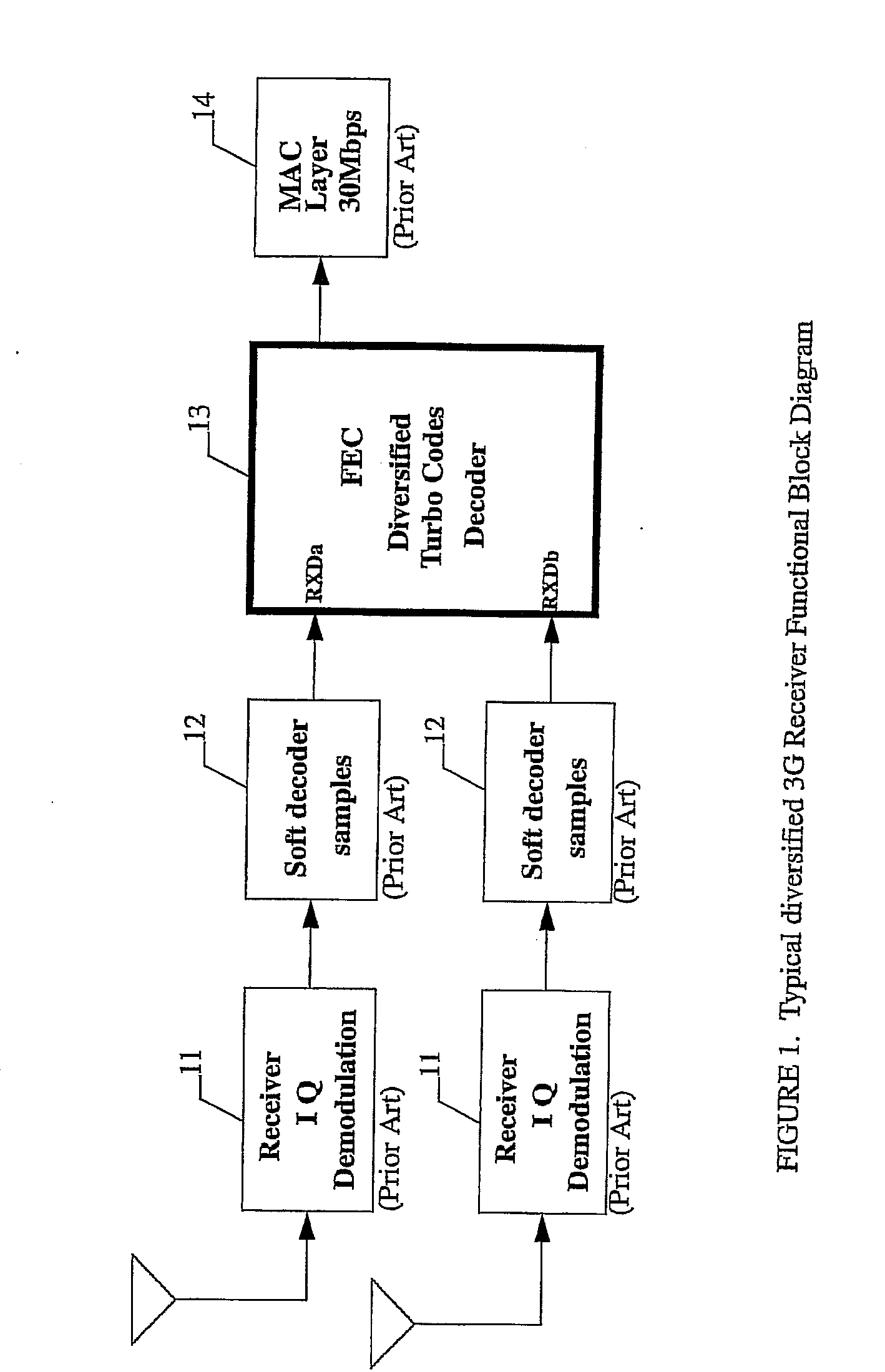

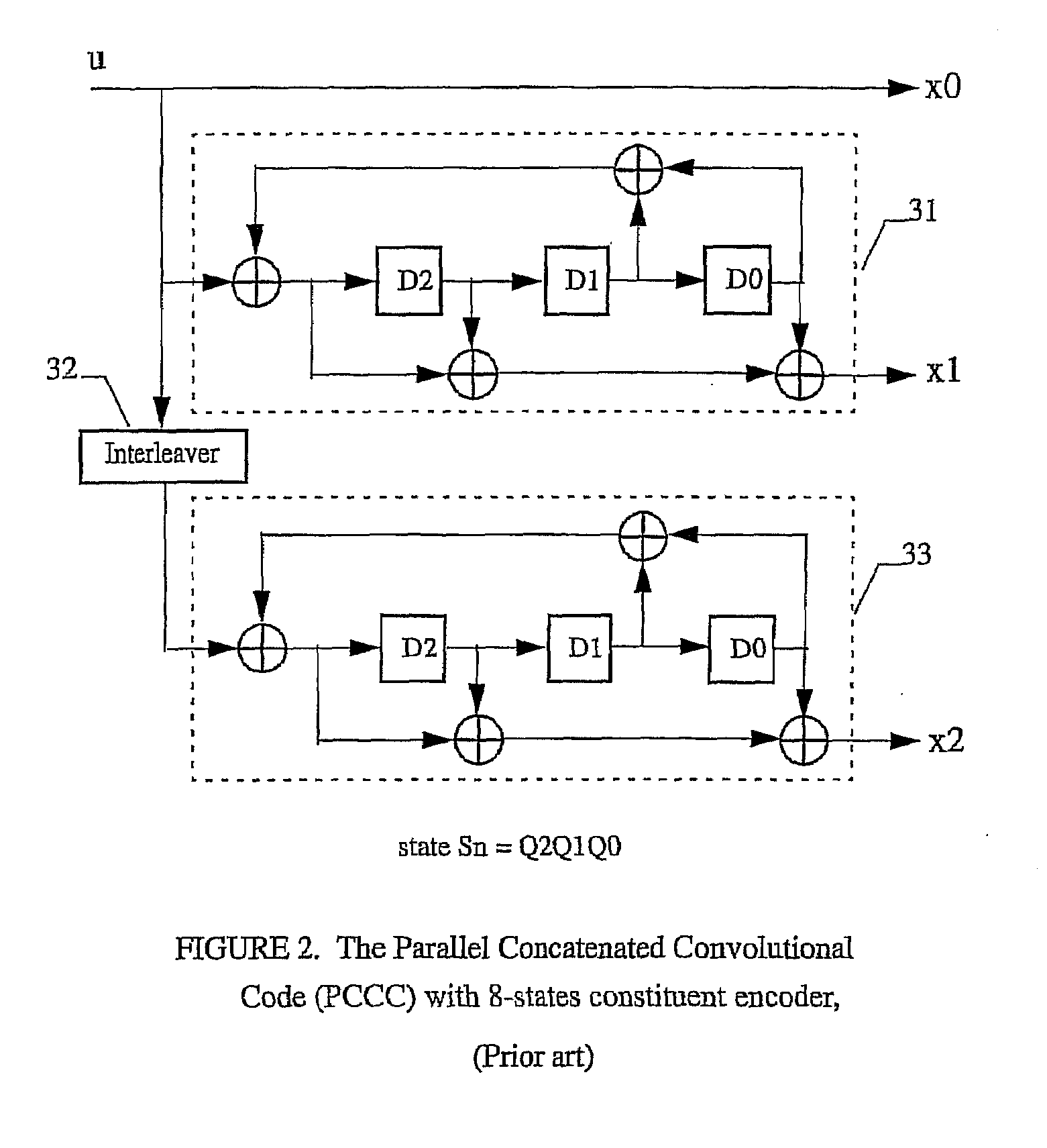

[0048]An illustration of a 3GPP 8-state Parallel Concatenated Convolutional Code (PCCC), with coding rate 1 / 3, constraint length K=4 is illustrated in FIG. 2. An implementation using SISO Log-MAP Decoders is illustrated in FIG. 3.

[0049]In accordance with an exemplary embodiment, a diversity processing Turbo Codes Decoder includes two parallel blocks 40a, 40b of Turbo Codes Decoders for each path of received data RXDa and RXDb. Each identical Turbo Codes Decoder block 40a, 40b has concatenated max Log-MAP SISO Decoders A 42 and B 44 connected in a feedback loop with Interleaver Memory 43 and Interleaver Memory 45. The Soft output of Turbo Codes Decoder block 40a is fed into the input of the Diversified Logic block 48. Conversely, the Soft output of Turbo Codes Decoder block 40b is fed-back into the input of the Diversified Logic block 48. The sum of the two outputs Z1, Z3 of the Turbo Codes Decoder block 40a, 40b is fed into the Hard-Decoder to generate output Y da...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More