Thin film transistor having a two-layer semiconductor, manufacturing method therefor, and display apparatus using the same

a technology of thin film transistor and manufacturing method, which is applied in the direction of transistors, semiconductor devices, electrical devices, etc., can solve the problems of uniform display image and inhibit unstable operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

example 1

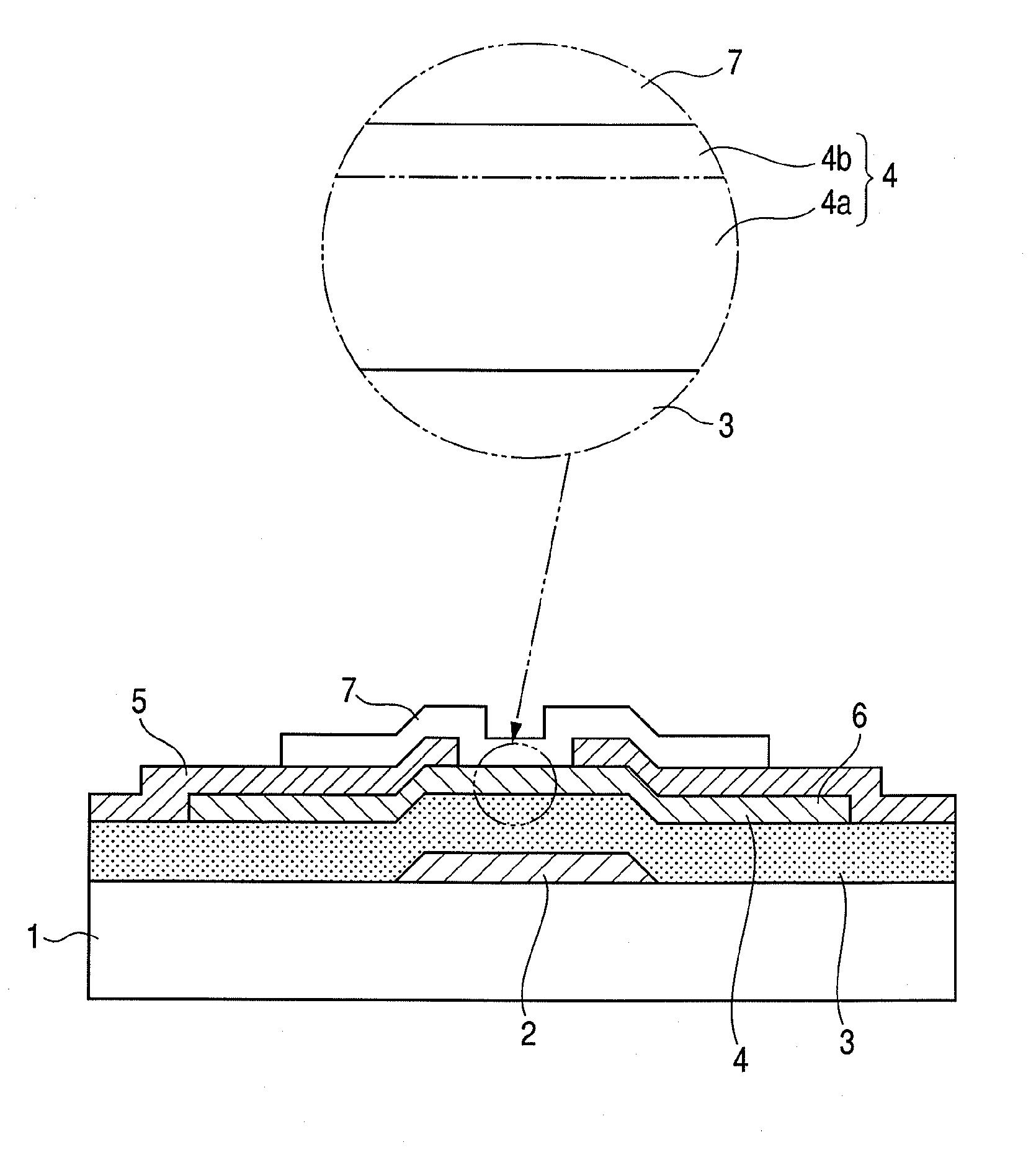

[0101]In the present Example, a TFT including a columnar structure in a semiconductor layer will now be described below.

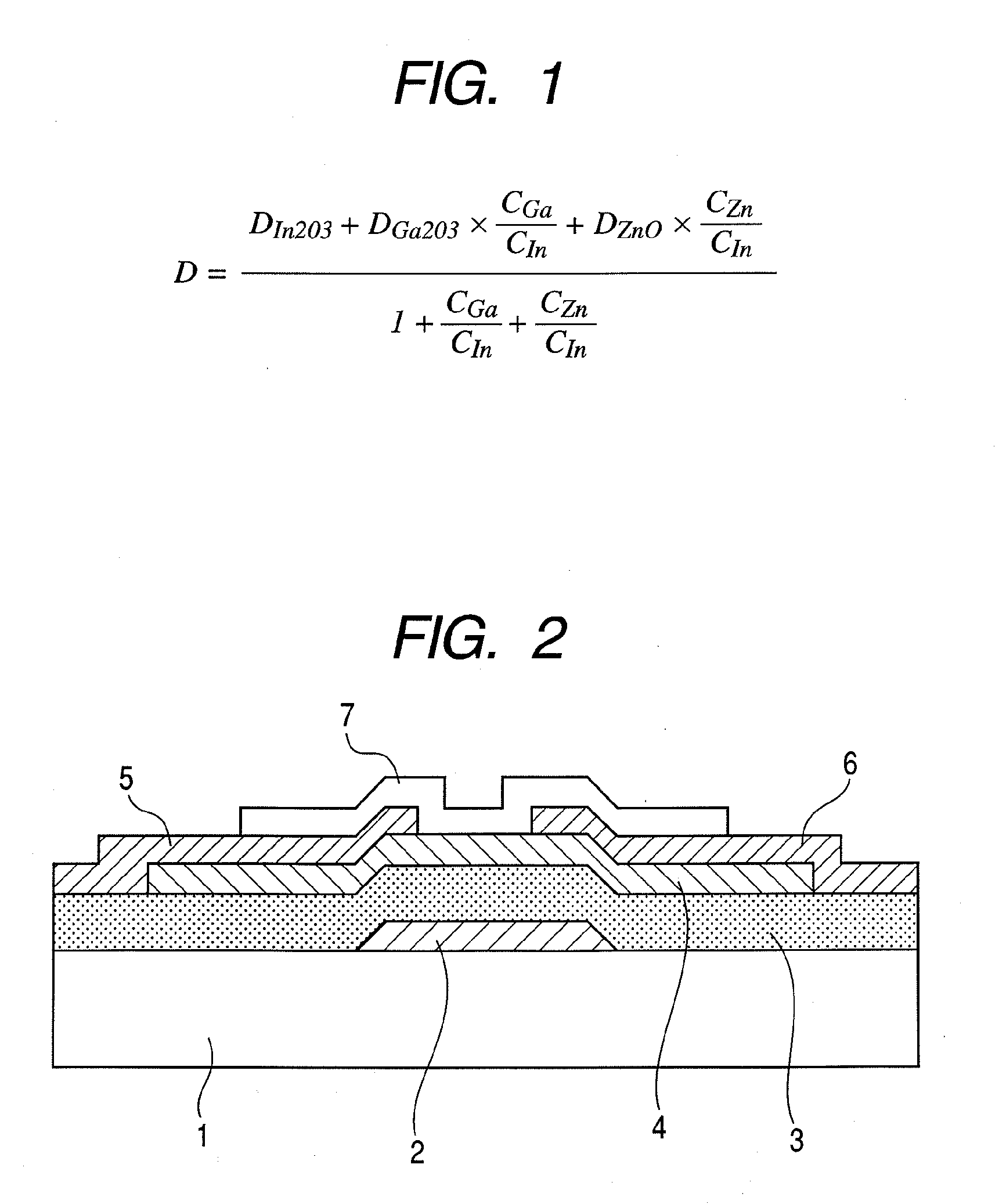

[0102]A bottom gate type TFT provided with a protective layer as illustrated in FIG. 2 is prepared with the use of a glass substrate.

[0103]At first, a metallic multilayer film including Ti of 5 nm, Mo of 40 nm and Ti of 5 nm is formed on the glass substrate with a sputtering technique which uses a Ti target and an Mo target. This metal film is patterned with a photolithographic technique to be formed into a gate electrode.

[0104]A film of amorphous SiOx of 200 nm is formed thereon with the sputtering technique which uses SiO2 as the target, and is formed into a gate insulation layer. At this time, Ar is used as a sputtering gas.

[0105]An amorphous oxide semiconductor film of 40 nm including In—Zn—Ga—O is formed thereon with the sputtering technique which uses In—Zn—Ga—O as the target. A semiconductor layer is then formed by patterning the semiconductor film with the ...

example 2

[0115]In the present Example, a TFT including a semiconductor layer made of a first layer having high mass density and a second layer having low mass density will now be described below.

[0116]A bottom gate type TFT provided with a protective layer as illustrated in FIG. 9 is prepared with the use of an n-type Si substrate.

[0117]At first, a thermal oxidation Si film (gate insulation film 93) is formed in a thickness of 100 nm on an n-type Si substrate 92. In FIG. 9, an independent gate electrode is not provided, but the n-type Si substrate 92 functions as a gate electrode. An amorphous oxide semiconductor film (first layer) including In—Zn—Ga—O is formed thereon into 30 nm with a sputtering technique which employs In—Zn—Ga—O as a target and room temperature as a substrate temperature. Furthermore, an amorphous oxide semiconductor film (second layer) including In—Zn—Ga—O is formed thereon into 10 nm with a PLD technique which employs room temperature as a substrate temperature. The tw...

example 3

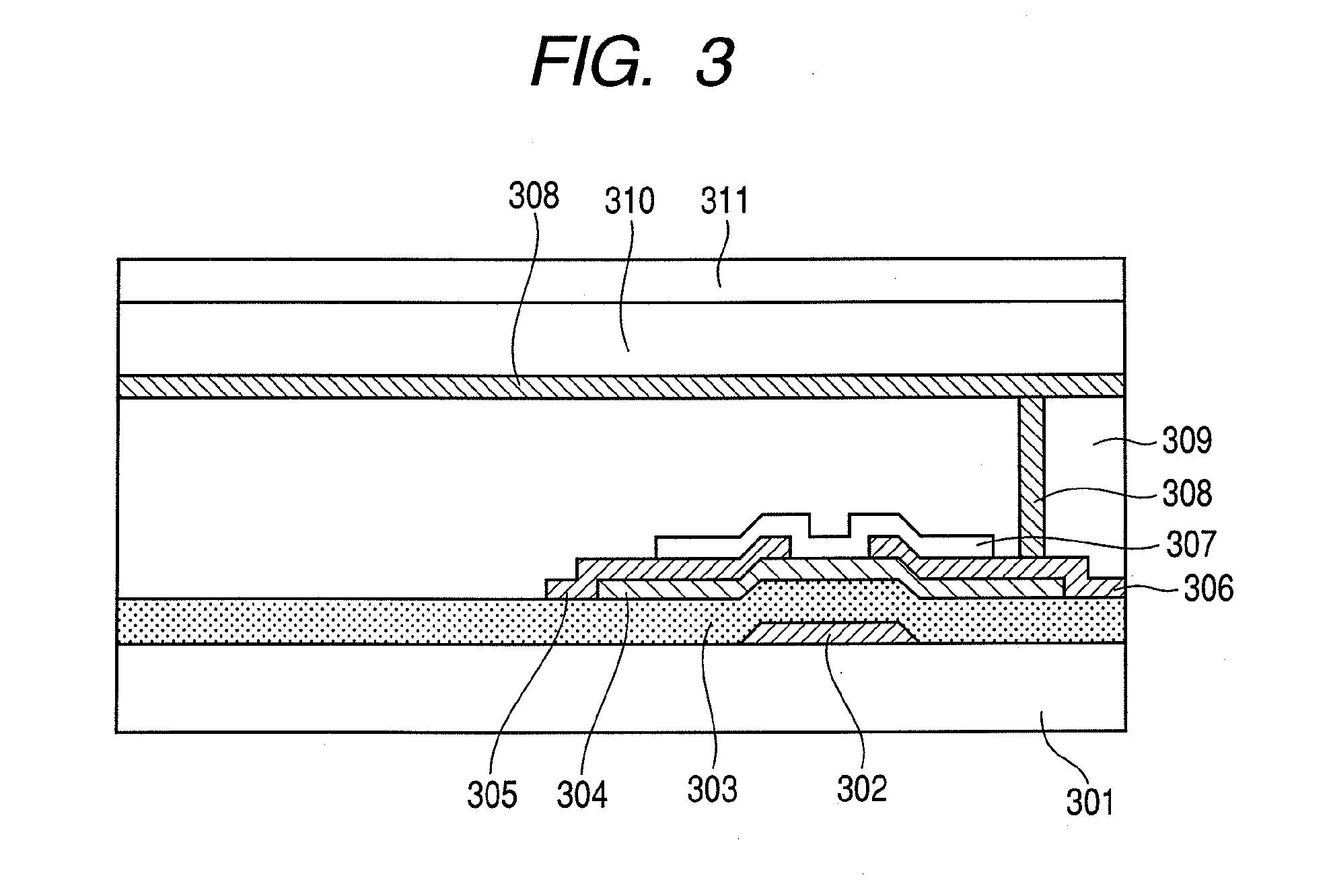

[0127]In the present Example, a display apparatus using a TFT in FIG. 3 will now be described.

[0128]A TFT is manufactured in a process similar to that in Example 1.

[0129]After the TFT has been prepared, an interlayer insulation film 309 is formed. At this time, a contact hole for connecting a drain electrode 305 with a lower electrode 308 is formed.

[0130]Subsequently, a lower electrode 308 is formed thereon by forming a film of Al with an electron beam vapor deposition technique. The lower electrode 308 is connected with the drain electrode 305 through the contact hole.

[0131]Next, an electron transport layer, a light-emitting layer, a hole transport layer, a hole injection layer are sequentially formed with a vapor deposition technique, which form an organic EL light-emitting layer as a whole.

[0132]Finally, an upper electrode 311 is formed thereon by forming a film of ITO with a sputtering technique.

[0133]Here, when voltage is applied to a source electrode 306 of the TFT and voltage...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More