Microcomputer, electronic equipment, and debugging system

a microcomputer and electronic equipment technology, applied in the field of microcomputers, electronic equipment, and debugging systems, can solve the problems of not being able to acquire trace information for the portions necessary for debugging, difficult to implement a trace range specification with external circuitry, and difficulty in obtaining real-time trace information

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

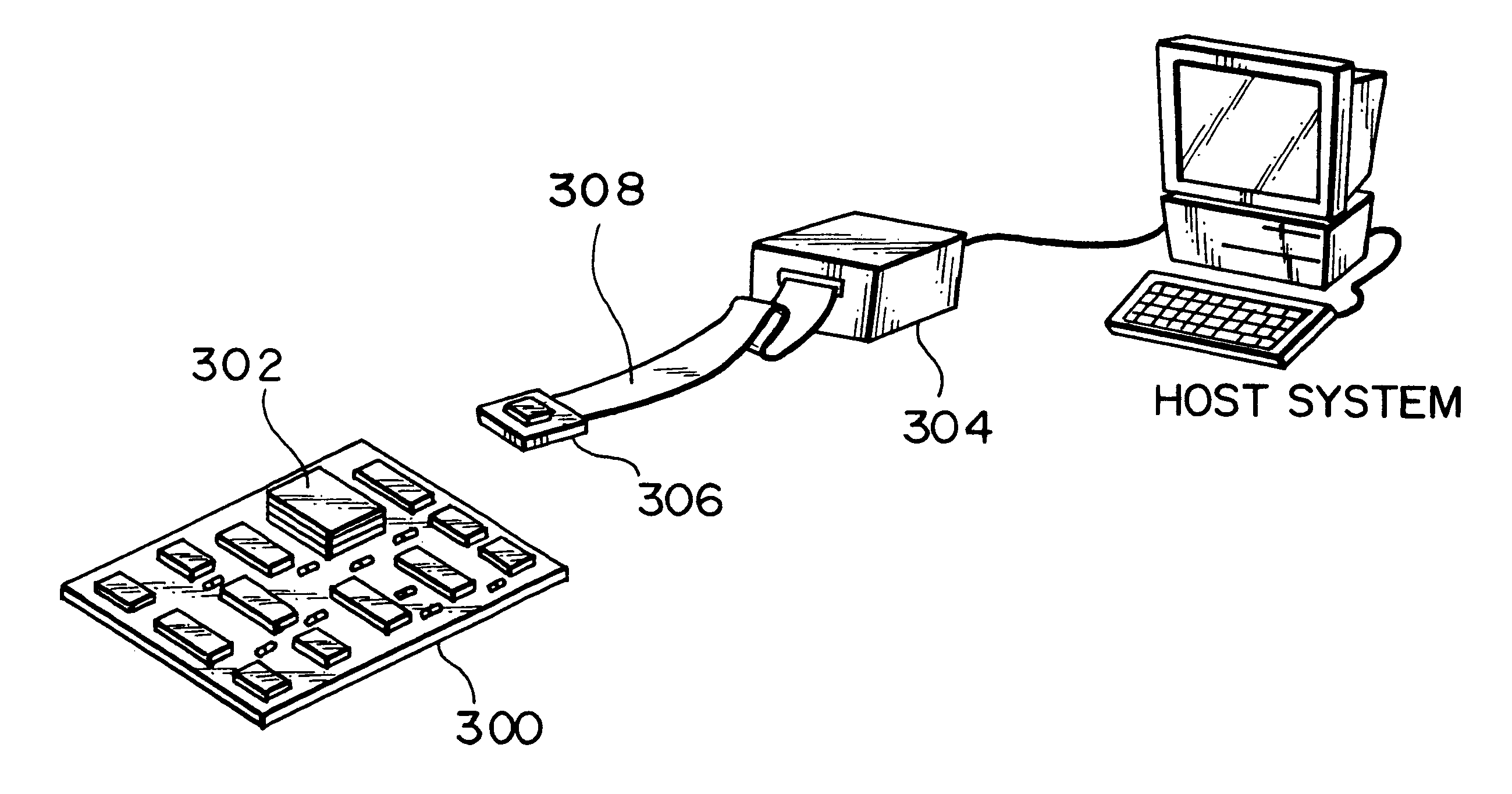

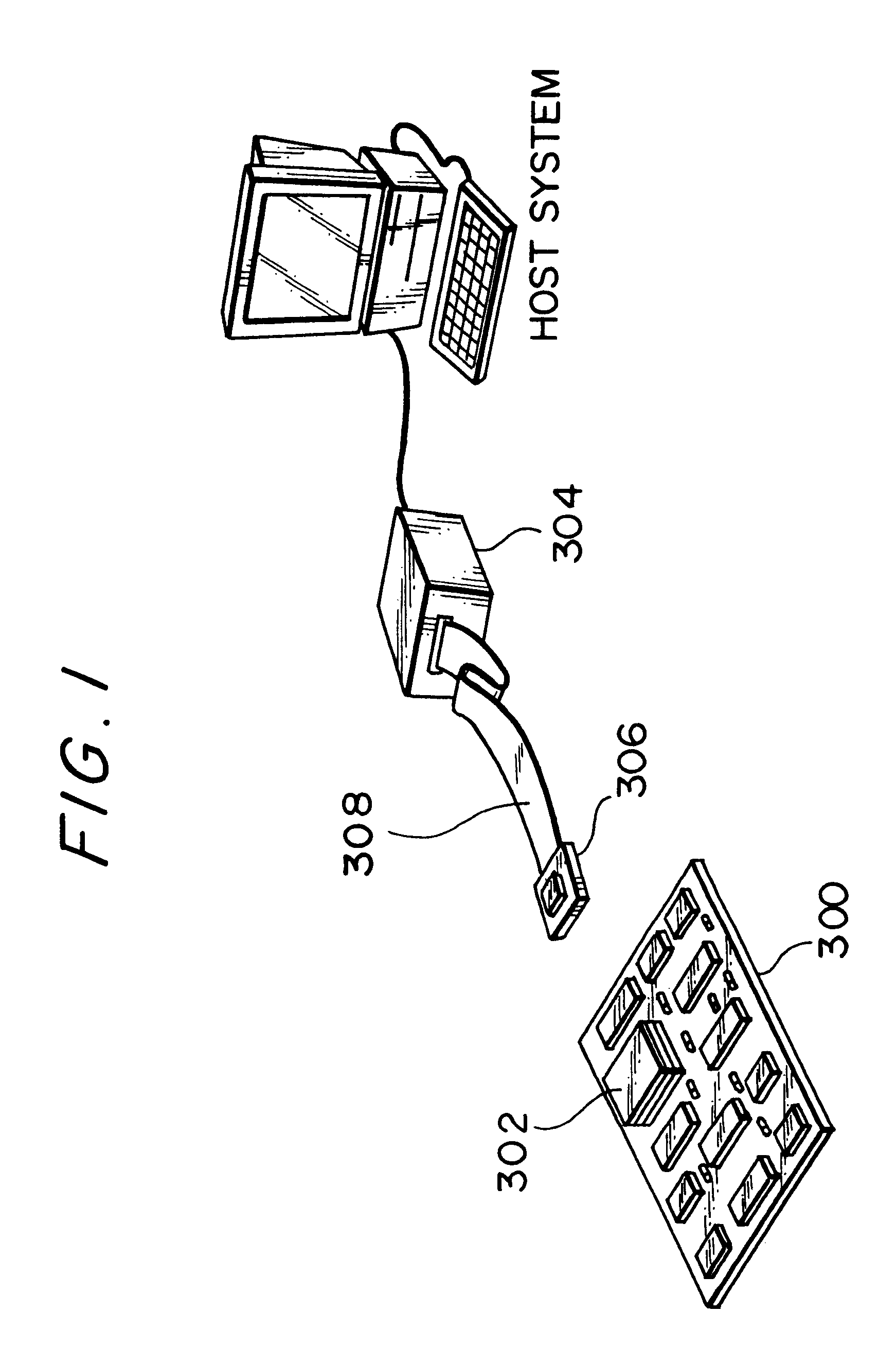

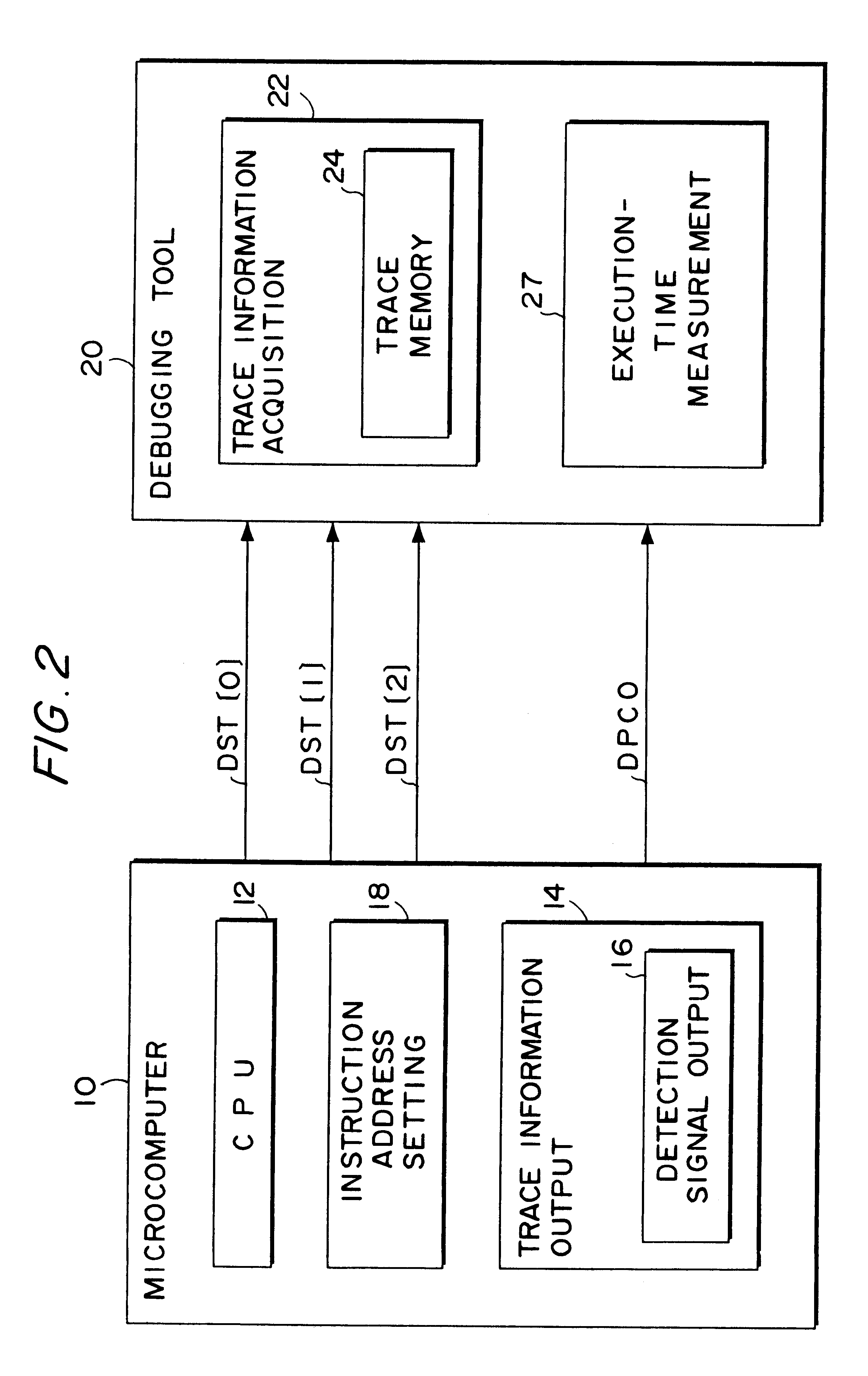

detailed example of the structure of the microcomputer and debugging system of this embodiment is shown in FIG. 6. As shown in FIG. 6, the microcomputer 10 comprises a CPU 12, a bus control unit (BCU) 26, an internal memory 28, a clock generation section 30, an on-chip monitor section 40, and the trace information output section 14.

In this case, the CPU 12 executes various instructions and comprises internal registers 13. The internal registers 13 comprise general-purpose registers R0 to R15 as well as a stack pointer (SP) register, a higher arithmetic register (AHR) for storing sum-of-products result data, and a lower arithmetic register (ALR) for storing sum-of-products result data, which are special registers.

The BCU 26 controls buses. It controls a bus 31 of a Harvard architecture connected to the CPU 12, a bus 32 connected to the internal memory 28, an external bus 33 connected to the external memory 36, and an internal bus 34 connected to components such as the trace informati...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More