Delay locked loop circuit for internally correcting duty cycle and duty cycle correction method thereof

a technology of delay locking loop and duty cycle, which is applied in the direction of pulse technique, generating/distributing signals, instruments, etc., can solve the problems of limiting the operating frequency, power consumption increasing, and dcc not performing properly, so as to achieve the effect of improving memory device characteristics, reducing power consumption, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037]The present invention now will be described more fully with reference to the accompanying drawings, in which preferred embodiments of the invention are shown.

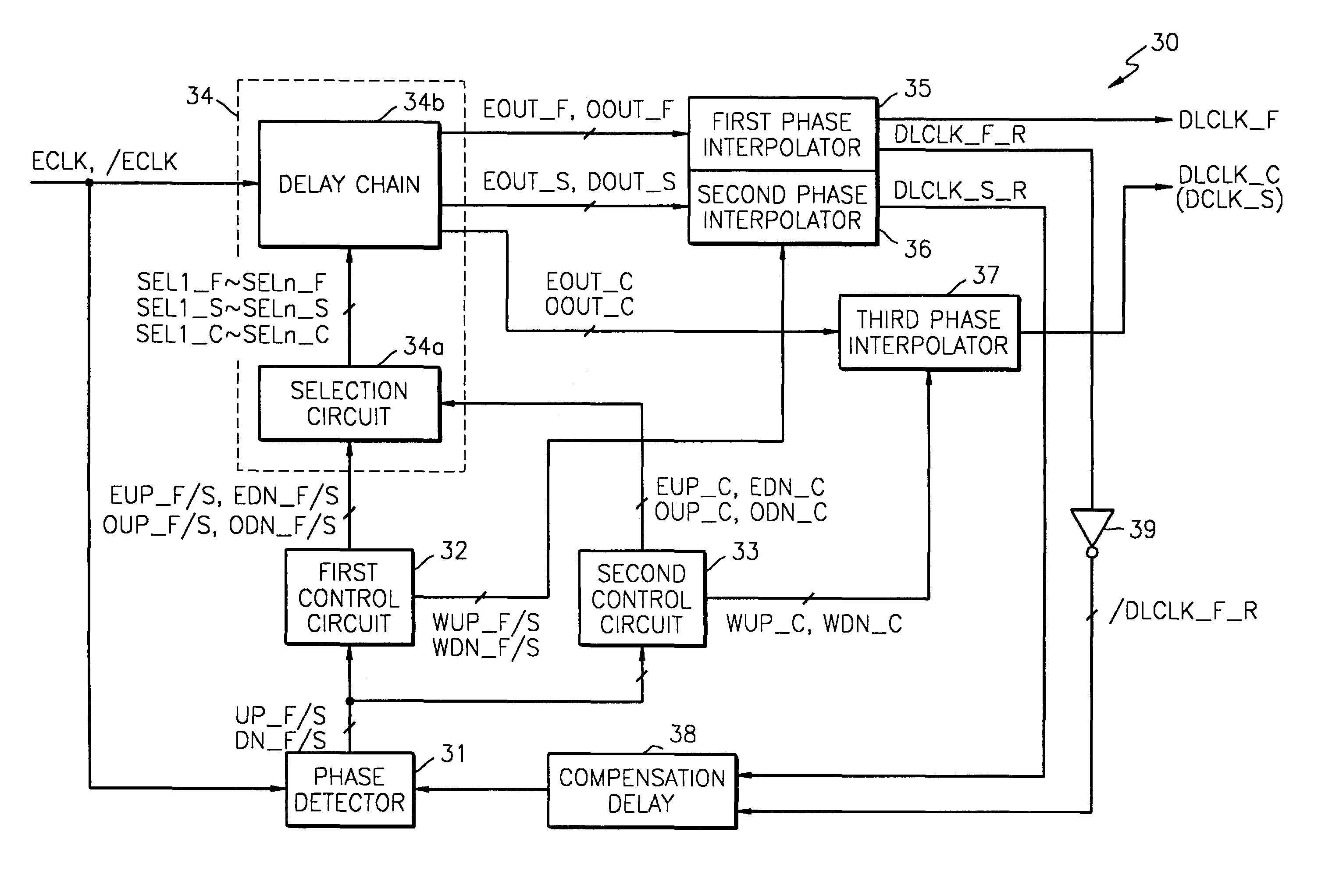

[0038]FIG. 3 is a block diagram of a DLL30 having a duty cycle corrector (DCC) according to an embodiment of the present invention. Referring to FIG. 3, DLL30 includes a phase detector 31, a first control circuit 32, a second control circuit 33, a delay line unit 34, a first phase interpolator 35, a second phase interpolator 36, a third phase interpolator 37, and a compensation delay 38.

[0039]DLL30 is capable of correcting duty cycle. The conventional DLL for a double data rate (DDR) system includes two loops to control a rising edge and a falling edge and includes a phase blender to correct the duty cycle. In contrast, in DLL30, another loop is included, instead of the phase blender, to correct the duty cycle. That is, the second control circuit 33 and the third phase interpolator 37 are added to the conventional DLL of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More