Quickflashing memory unit and its manufacturing method

A storage unit and manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve problems such as high process difficulty, slow component operation speed, and increase the complexity of back-stage processes, etc., to achieve The effect of increasing the reading rate and improving the performance of the device

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

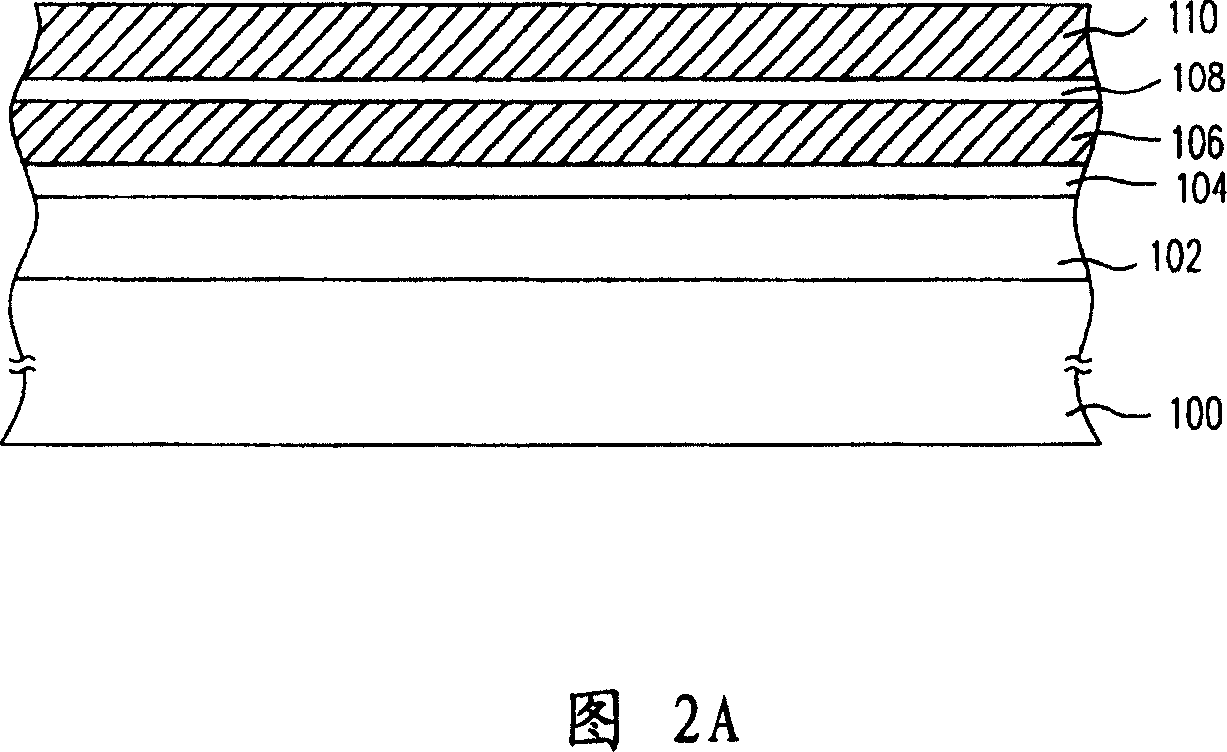

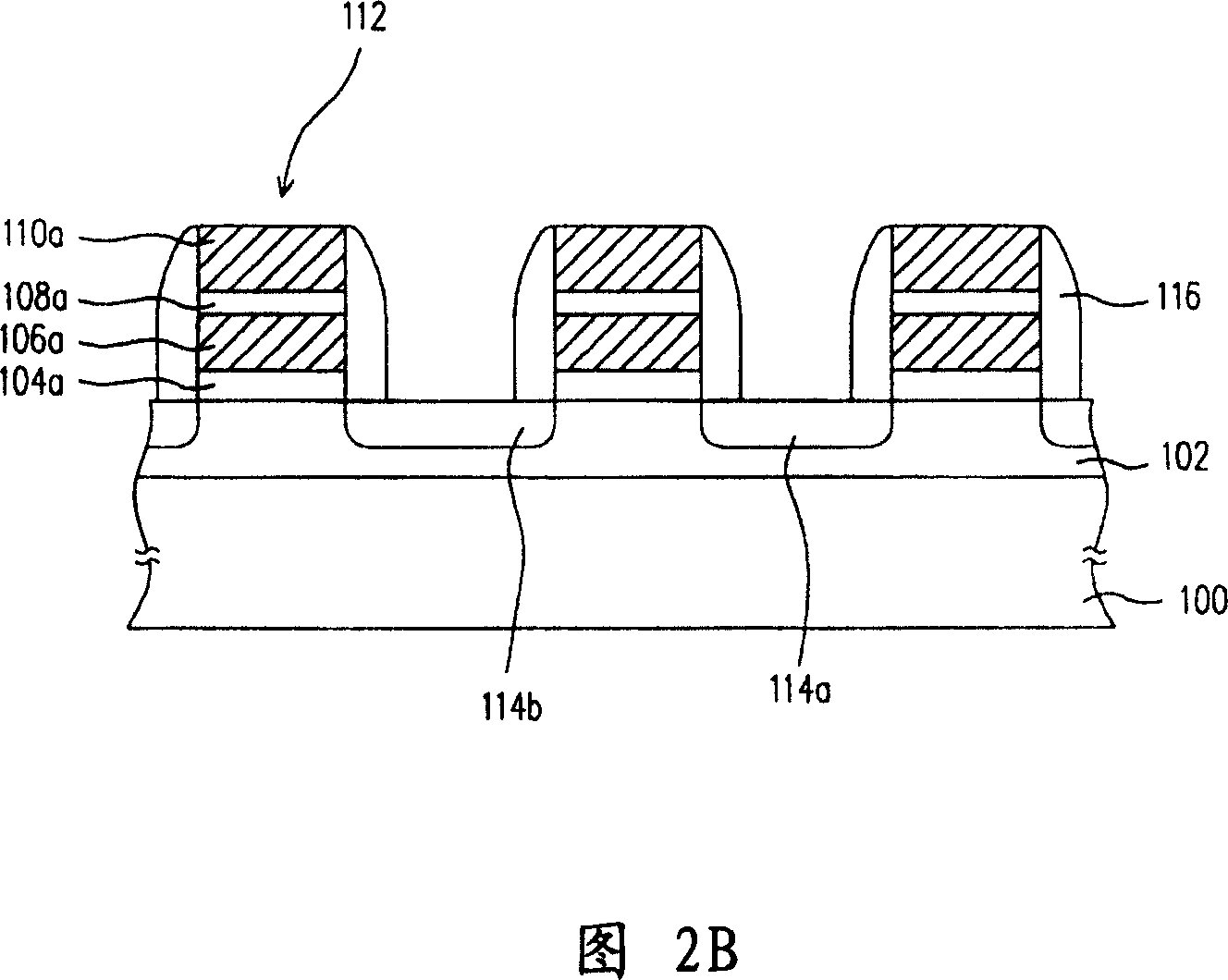

[0048] 2A to 2E are cross-sectional views of a manufacturing process of a flash memory unit according to a preferred embodiment of the present invention.

[0049] Referring to FIG. 2A , first a p-type shallow well region 102 is formed in an n-type substrate 100 , and then a dielectric layer 104 , a conductive layer 106 , a dielectric layer 108 and a conductive layer 110 are sequentially formed on the n-type substrate 100 . Wherein, the material of the dielectric layer 104 is, for example, silicon oxide, and its forming method is, for example, thermal oxidation. The material of the dielectric layer 108 is, for example, silicon oxide / silicon nitride / silicon oxide, etc., or is composed of a silicon oxide layer or a silicon oxide / silicon nitride layer, etc., and its formation method is, for example, Low Pressure Chemical Vapor Deposition (Low Pressure CVD) , LPCVD). The material of the conductor layer 106 and the conductor layer 110 is, for example, polysilicon doped with impurit...

no. 2 example

[0063] In the present invention, a doped region can also be formed in the n-type drain region and the p-type shallow well region first, and then a metal silicide layer is formed in the n-type drain region, so as to reduce the process required for forming the doped region. energy. 3A to 3B are sectional views of a part of the manufacturing process of a flash memory unit according to another preferred embodiment of the present invention. The components in this embodiment are the same as those in the first embodiment, that is, they are denoted by the same reference numerals. For the forming method and materials, please refer to the description of the first embodiment, and will not be repeated below.

[0064] Please refer to FIG. 3A , after completing the structure shown in FIG. 2B according to the description of FIGS. 2A to 2B of the above-mentioned embodiment, a photoresist with an opening 124 is then formed on the n-type substrate 100 and the gate stack structure 112 layer 122...

no. 3 example

[0068] 4A to 4B are schematic cross-sectional views showing a part of the manufacturing process of a flash memory unit according to another embodiment of the present invention. Referring to FIG. 4A , after the structure shown in FIG. 2B is completed according to the processes described in FIGS. 2A to 2B of the first embodiment, a mask layer 140 having an opening 142 is then formed on the n-type substrate 100 . Wherein, the opening 142 exposes the n-type drain region 114b. Then, the metal silicide layer 120a is formed in the n-type drain region 114b by using the mask layer 140 as a mask. In particular, the metal silicide layer 120 runs through the junction of the n-type drain region 114 b and the p-type shallow well region 102 . At this time, the n-type drain region 114b is electrically short-circuited with the p-type shallow well region 102 through the metal silicide layer 120 .

[0069] In a preferred embodiment, the method of forming the metal silicide layer 120a is, for e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More